Physical Design Techniques for Three-Dimensional ICs

Abstract

The complexity of the three-dimensional (3-D) physical design process is discussed in this chapter. Several approaches for classic physical design issues, such as floorplanning, placement, and routing, from a 3-D perspective, are extensively reviewed. To enhance the understanding of these techniques targeted to 3-D systems, certain fundamental methods and algorithms used in the physical design of planar circuits are also discussed. Traditional issues such as partitioning, floorplanning, placement, and routing are reviewed. The task of through silicon via planning and the effect that this task has on the quality of 3-D floorplans are also described. Some layout tools developed specifically for 3-D circuits are briefly reviewed.

Keywords

Tier partitioning; 3-D floorplanning; 3-D placement; 3-D routing; fixed outline floorplanning; force directed placement; sequence pair technique

A variety of recently developed and emerging fabrication processes for three-dimensional (3-D) systems are reviewed in Chapter 2, Manufacturing of Three-Dimensional Packaged Systems, and Chapter 3, Manufacturing Technologies for Three-Dimensional Integrated Circuits. A complete and effective design flow, however, for 3-D ICs has yet to be demonstrated. This predicament is due to the additional complexity and issues that emerge from introducing the third dimension to the integrated circuit design process. Existing techniques for 3-D circuits primarily focus on the back end of the design process. Floorplanning, placement, and routing techniques for 3-D circuits are discussed, respectively, in Sections 9.2, 9.4, and 9.5. Many of these techniques are based on physical design methods for planar circuits. Some of these methods for floorplanning and placement of planar circuits are presented, respectively, in Sections 9.1 and 9.3.

The primary difference in the physical design of 3-D circuits is the management (or planning) of the intertier interconnects (i.e., the through silicon vias (TSVs)), which differ from the intratier interconnects that occupy silicon area. Treating the TSVs the same as the horizontal interconnects results in underperforming systems (both lower speed and higher power). During the past few years, physical design techniques for 3-D circuits have evolved to consider these issues, producing increasingly more compact circuits, which effectively translate to shorter wirelength and less area. Furthermore, many of these techniques consider thermal objectives or are primarily focused on mitigating thermal hot spots in 3-D ICs. Although all of these physical design techniques share several characteristics, due to the importance of thermal issues in 3-D integration, a discussion of thermal management techniques is deferred to Chapter 13, Thermal Management Strategies for Three-Dimensional ICs. In addition to physical design techniques, a brief discussion on layout tools for 3-D circuits is presented in Section 9.6. A short summary relating to physical design methodologies for 3-D circuits is included in the last section of this chapter.

9.1 Floorplanning Techniques

The predominant design objective for floorplanning a two-dimensional (2-D) circuit has traditionally been to achieve the minimum area while interconnecting the circuit blocks with minimum length wires and with no overlap among the circuit blocks [328]. These two objectives are employed in most floorplanning algorithms, which can be classified as either slicing [329] or nonslicing [330,331]. For any circuit that comprises N blocks (where the size of these blocks has evolved over time from a handful of logic gates to thousands of logic gates), each with width wi and height hi, area driven techniques target minimum area floorplans that fit the total area A of the blocks, described by

(9.1)

(9.1)

(9.1)

Both fixed outline [332–334] and free outline techniques have been developed. For fixed outline methods, the outline can be set with an increase in A by a multiplication factor (1+β)A, where β is the percent area of the floorplan not occupied by blocks and is typically called “whitespace.”1

Although a fixed outline floorplan implies a fixed area, this assumption is typically not the case for the aspect ratio of the outline which can vary within specified limits. Fixed outline algorithms are more suitable for hierarchical floorplanning, where a variable outline is employed for the cells within the individual blocks and a fixed outline is used at the highest level, producing a compact floorplan [332]. Consequently, depending upon the floorplanning technique, the blocks can be either variable or fixed area and can also either have a constant (hard block) or variable (soft block) aspect ratio. The primary difference between a fixed and variable aspect ratio is that soft blocks produce more compact floorplans [330,335,336], but the solution space explodes as each block can assume any aspect ratio [332].

Another important issue in floorplanning is the representation of the blocks. Many representations have been proposed such as the transitive closure graph [335], O-trees [336], corner block list [337], and sequence pair (SP) [338]. For the SP technique, at least one floorplan with minimum area exists. Several floorplanning methods for 3-D circuits utilize the SP representation technique [339]. The SP is therefore discussed in greater depth to assist the reader in understanding the main features of this popular technique.

9.1.1 Sequence Pair Technique

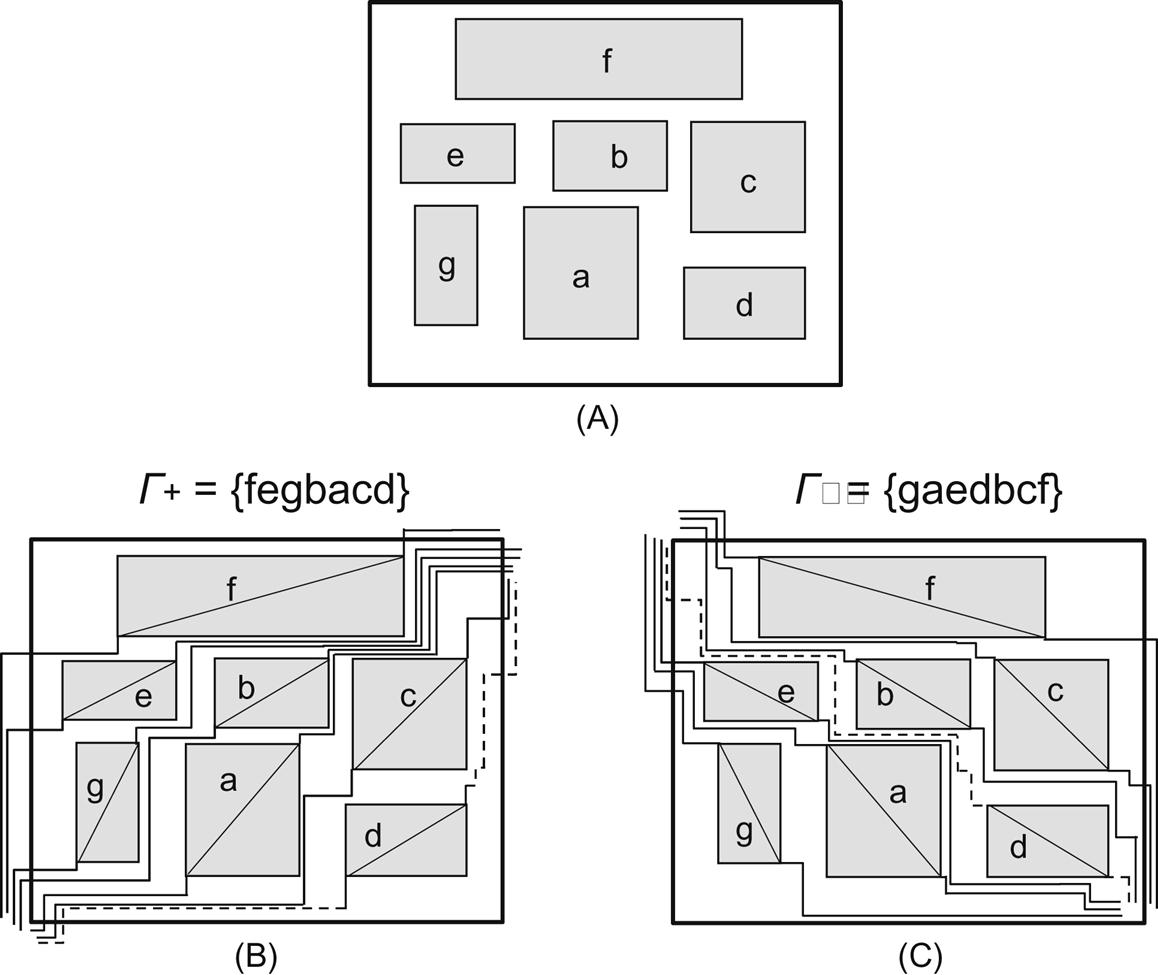

The salient feature of the SP technique is the formation of a pair of orderings of blocks that is floorplanned (or packed) within some area outline, as illustrated in Fig. 9.1. To generate a pair of sequences, several lines are formed according to three rules. The lines should not cross (1) the boundary of other modules other than the module for which the line is drawn, (2) previously drawn lines, and (3) the boundary of the outline. Two types of lines are drawn for every block, which are the “positive step line” and the “negative step line.” The positive step lines are formed for each block as follows. A line segment begins from the upper right corner of a block (say block b) and moves upwards and to the right in a stepwise manner towards the upper right corner of the circuit boundary, obeying the three rules. Additionally, another line segment begins from the lower left corner of the block and moves downwards and to the left towards the lower left corner of the circuit boundary. These two line segments with the diagonal line through b form the positive step line for block b. In a similar manner the negative step lines are formed, where the line segments for each block begin, respectively, from the upper left and lower right corners of the block. These segments are drawn by moving, respectively, up and left and down and right.

An example of these lines for the circuit blocks shown in Fig. 9.2A is illustrated in Figs. 9.2B and C, where the relevant lines for block d are depicted in this figure with dashed lines. The lines can be linearly ordered, leading to the two orderings for the blocks notated as Γ+ and Γ− corresponding, respectively, to the order of the positive and negative step lines. Based on Fig. 9.2, the SP is Γ+={fegbacd} and Γ−={gaedbcf}, which also provides useful information for ordering the blocks. Note that each block appears only once in each sequence and relates in four unique ways with the other blocks. For example, assuming two blocks s and s′, s can only appear after/before s′ in ![]() . To determine the relative position among the blocks, the four disjoint sets can be described where [338]

. To determine the relative position among the blocks, the four disjoint sets can be described where [338]

(9.2)

(9.3)

(9.4)

(9.5)

Based on these definitions, the following theorem has been proven [338]: assuming the SP (Γ+, Γ−) produced with the use of positive/negative step lines, the relative order of the blocks can be determined. Consequently, if ![]() , s is left of s′, if

, s is left of s′, if ![]() , s is right of s′, if

, s is right of s′, if ![]() , s is above s′, and if

, s is above s′, and if ![]() , s is below s′.

, s is below s′.

Based on this theorem, SP (Γ+, Γ−), and assuming that the circuit area is divided into an m×m grid, the optimal packing can be reached in O(m2) by utilizing the longest path algorithm [340]. In this process, horizontal and vertical constraint graphs are employed. Construction of these graphs is commonly used in physical design techniques [328]. More recent methods based on the SP representation have further reduced the complexity to produce floorplans in O(m log(m)) [340] and O(m log(log(m))) [341].

In addition to an efficient representation, producing high quality floorplans requires appropriate objective functions, where if the problem is packing driven, the objective is to minimize area, while connectivity driven functions emphasize minimizing wirelength. Many floorplan methods utilize cost functions that target both of these objectives and typically are of the form,

(9.6)

where the coefficients c1 and c2 indicate the importance of each of the two objectives. Area can be described, for instance, by (1+β)A. Irrespective of the formulation of the floorplanning problem, determining the area of the blocks within a floorplan is a straightforward process. Alternatively, at this early stage, wirelength cannot be accurately known. Among different models for calculating the wirelength, the half perimeter wirelength (HPWL) model is often utilized, where the efficiency of this metric for 2-D circuits has been evaluated by many techniques [342]. An example of HPWL is illustrated in Fig. 9.3.

The two objectives in (9.6) indicate a multiobjective optimization process even for the simplest floorplanning cost functions, requiring efficient solvers. Simulated annealing (SA) [343] is a popular solving technique that has been extensively applied to floorplanning and placement problems. The annealing process progresses towards an efficient floorplan by applying different block movements, such as swapping two blocks or rotating a block. Issues with this rather classic approach are that the wirelength is determined after each block movement and the solver only considers the size of the blocks, not the available whitespace. A more compact floorplan may be possible by moving a block to a different location within an outline of the floorplan (assuming this outline is fixed).

To address these issues of increasing computational time, approaches to handle incremental moves of the blocks have recently been explored which consider the whitespace. The notion of slack is borrowed from static timing analysis [344] and a spatial slack is assigned to a block sequence where the SP representation is employed. Similar to critical timing paths, a critical path for a floorplan is a sequence of blocks in the x- or y-direction adjacent and constrained with respect to each other to ensure that changing the site of a block causes neither an overlap or an increase in floorplan area. No whitespace in a specific path direction exists when a block is moved, similar to zero slack for the delay of a critical path. The slack analogy from timing analysis requires that all of the slacks (i.e., whitespace) of paths (i.e., sequences) of blocks must be determined for each direction, which is straightforward if the SP representation is followed. An example of slack computation for two different floorplans is depicted in Fig. 9.4. Subtracting the x coordinate of a block from the results when the blocks are packed, respectively, from left-to-right and from right-to-left, yields the x-slack of the block. Subtracting the y coordinate of this block from results when the blocks are packed, respectively, from bottom-to-top and top-to-bottom, yields the y-slack of the block.

The spatial slack information can lead to more efficient block moves to reduce the floorplan area. Block paths (or sequences) with zero slack are appropriate candidates for moves as these zero slack block paths determine the span of the floorplan along a physical direction. Moving a block from a path with high slack along a direction only mildly affects the length of the floorplan along this direction. Therefore, blocks within paths with zero slack along one direction but a large slack in the other direction are good candidates for single block moves. For example, a block with close to zero slack in both directions is a good candidate to be moved to a path with a large slack in both directions [332]. Application of these slack-based criteria for guiding block moves have led to improved results in producing valid floorplans, where a maximum 15% whitespace of the total block area is allowed and the outline is fixed. Considering whitespace in the floorplaning process becomes more important in 3-D circuits as significant area is consumed by the TSVs. Moreover, determining the wirelength for intertier connections where the TSVs are placed within whitespace regions can render the traditional HPWL metric a low accuracy estimate of the actual wirelength. These challenges require a different approach when floorplanning 3-D circuits.

9.2 Floorplanning Three-Dimensional ICs

An efficient floorplanning technique for 3-D circuits should adequately handle three important issues: representation of the third dimension, any related increase in the solution space, and the allocation (number and position) of the TSVs. These requirements affect specific aspects of the floorplanning process for 3-D circuits, such as the wirelength metric and the block representation. Techniques that investigate the first two issues considering the increased solution space are discussed in Section 9.2.1. The TSVs in these techniques are either assumed to be integrated within the 3-D circuit blocks (or cuboids) during floorplanning or to be placed anywhere across the entire tier as long as no overlap exists. In Section 9.2.2, floorplanning methods that bound the allocation of TSVs within a 3-D circuit are reviewed. These techniques emphasize the effect of inserting TSVs on several design objectives. These results demonstrate that a planning step for TSV allocation is indispensable when floorplanning 3-D circuits.

9.2.1 Floorplanning Three-Dimensional Circuits Without Through Silicon Via Planning

Certain algorithms incorporate the 3-D nature of the circuits, such as a 3-D transition closure graph (TCG) [345], sequence triple [346], and a 3-D slicing tree [347], where the circuit blocks are notated by a set of 3-D modules that determine the volume of a 3-D system. Utilizing these notations for the circuit blocks, an upper bound for 3-D slicing floorplans is determined [348]. In 3-D slicing floorplans, a tier successively bisects the volume of a 3-D system. The upper bound for 2- and 3-D slicing floorplans is illustrated in Fig. 9.5. The coefficient r shown in Fig. 9.5 is the shape flexibility ratio and denotes the maximum ratio of the dimensions of the modules (i.e., max(width/height, depth/height, width/depth)). This ratio is assumed to be greater than two. The use of this ratio implies that all modules are assumed to be “soft blocks.” Moreover, as observed in Fig. 9.5, Vtotal is the sum of the volume of the blocks that comprise the target system, and Vmax denotes the maximum volume among the blocks. In general, 3-D floorplans result in larger unused space as compared to 2-D slicing floorplans primarily due to the highly uneven volume of the 3-D modules. For high flexibility ratios, however, this gap is considerably reduced and, in certain cases, the upper bound for 3-D floorplans is smaller than in 2-D floorplans.

Although a high flexibility ratio offers more compact floorplans with less unused area, this assumption may not be practical as changing the length of a circuit block along the z-direction (i.e., changing the number of tiers spanned by a block) can greatly affect the number of intertier connections required by this block. This number can affect, in turn, the number of blocks violating the assumption that the volume of the block remains constant for all values of r. Furthermore, treating blocks as soft (variable r) is not an option for IP blocks developed for 2-D systems. These legacy circuits can often be hard macros where the size of these blocks is unlikely or not permitted to change if, for example, some circuits originate from a third party source. This situation can lead to less compact floorplans with significant whitespace. Although this restriction results in area overhead, the whitespace can, alternatively, be used to insert TSVs for signaling, power and ground distribution, and thermal management, thereby avoiding additional area overhead.

Another computational issue relates to the notation of the dimensions of the blocks as continuous variables. The use of continuous variables is convenient as analytic methods can be used to accurately determine bounds or optimally solve similar problems. The third dimension, however, should be treated as a discrete variable, which can produce suboptimal solutions if continuous analytic methods are applied, since the blocks must be placed into a small number of physical tiers. Consequently, 3-D systems are more efficiently described as an array of two-dimensional planes where the circuit blocks are treated as rectangles rather than cuboids placed on any of the planes constituting the 3-D circuit [349–351]. This approach reduces complexity; despite the number of blocks increasing with the number of stacked tiers. The combinations rise drastically, exacerbating the solution space for floorplanning a 3-D system. This second challenge for 3-D floorplanning, which is to effectively explore the solution space within reasonable time, has led to multistep approaches that often are more efficient for floorplanning 3-D circuits than a single step approach.

In 3-D circuits, a multistep floorplanning technique commences by partitioning the blocks among the tiers of a stack [352]. An illustration of single and multistep approaches is shown in Fig. 9.6. In single step floorplanning algorithms, the floorplanning process proceeds by assigning the blocks to the tiers of a stack followed by simultaneous intratier and intertier block swapping, as depicted in Fig. 9.6. Alternatively, a multistep approach does not allow intertier moves after the partitioning step. The reason for this constraint is that intertier moves among blocks result in a formidable increase in the solution space, greatly affecting the computational time of a single step floorplanning algorithm. Indeed, assuming N blocks witihin a 3-D system consisting of n tiers, a flat floorplanning approach increases the number of candidate solutions by Nn−1/(n−1)! times as compared to a 2-D circuit consisting of the same number of blocks. The solution space for floorplanning 2-D circuits based on the TCG technique [335], and 3-D circuits with a single and multistep approach are listed in Table 9.1. Consequently, a multiphase approach can be used to significantly reduce the number of candidate solutions.

Table 9.1

Solution Space for 2-D and 3-D IC Floorplanning [352]

| Characteristic | 2-D IC | n-Tier 3-D IC | |

| TCG | TCG 2-D Array | Multistep | |

| Solution space | |||

| Ratio | 1 | ||

The partitioning scheme adopted in the multistep approach plays a crucial role in determining the compactness of a particular floorplan, as intertier moves are not allowed when floorplanning the tiers. Different partitions correspond to different subsets of the solution space which may exclude the optimal solution(s). The objective function for partitioning should therefore be carefully selected. Due to the silicon area of the TSVs, reducing the number of intertier connections is a reasonable objective. This objective typically minimizes the number of TSVs across the entire stack. Thus min-cut algorithms, such as the hMETIS algorithm [353], can be employed to produce 3-D partitions. However, other alternatives exist where the number of TSVs is not an objective for partitioning but rather a constraint. The partitioning can, for instance, be based on minimizing the estimated total wirelength of the system [352]. For example, a partitioning problem based on minimizing the estimated total wirelength can be described as

(9.7)

(9.8)

where ELnet is the estimated interconnect length connecting two blocks of a 3-D circuit, which can contain both horizontal and vertical interconnect segments. This estimate is not based on the traditional HPWL metric but is probabilistically determined [352]. The total number of intertier vias is denoted by TNvia, and the maximum number of allowed intertier vias within a 3-D system is notated by TVmax.

The issue is therefore which target objective will produce a more compact floorplan with shorter wirelength. If the cut size is proportionally related to the total wirelength, minimizing the cut size decreases not only the area of the TSVs but also the wirelength. Alternatively, if the dependence of wirelength on the number of TSVs is loose, from (9.7) and (9.8), where the TSV count approaches the upper bound may be a better choice, as more intertier connections will reduce long horizontal wires.

A 3-D floorplanner for two tiers based on [350] has been applied to the benchmark circuits included in the Microelectronic Center of North Carolina/Gigascale Research Center (MCNC/GSRC) benchmark suite [355] to better evaluate this tradeoff. The partition is based on [356] where a fixed cut size is utilized. The cut size is neither the minimum nor the maximum, as these extrema cut sizes limit the flexibility of the partition algorithm [354]. Rather, a fixed cut size lying between these bounds is employed. In addition, a 5% imbalance in area between the two tiers is allowed, and the whitespace is set to 20% of the total area of the blocks. Results of this evaluation indicate that partitioning is not important for circuits where the interconnects among blocks exhibit a narrow wirelength distribution (e.g., the n100, n200, and n300 benchmarks). Alternatively, circuits that include interconnects with a wide distribution of lengths are affected more by the partitioning step (e.g., ami33 and ami49). In addition, results characterizing the relationship between the total wirelength and the number of vertical interconnects across the tiers of the stack demonstrate that the total interconnect length does not strongly depend on the cut size if the circuit consists of a small number of highly unevenly sized blocks. This behavior can be attributed to the significant computational effort required to optimize the area of the floorplan rather than the interconnect length. Alternatively, in circuits composed of uniformly sized blocks, an inverse relationship between the number of vertical vias and the interconnect length is demonstrated. These results are useful indicators when floorplanning a multitier circuit, although the fixed cut size has only been applied to two tier circuits. It is unclear whether the same behavior occurs in stacks with more than two physical tiers.

The partitions are an input to another phase of the multistep process where the floorplan of each tier of a 3-D circuit is generated. Note that the floorplan of each of the tiers is simultaneously produced. In [352], the circuit blocks are represented in three dimensions by the corner block list method [337], while in [354], the SP [338] is used to represent the floorplans. In both of these techniques, SA is employed to produce the floorplans. For single step approaches, where partitions are not available, the starting point for the SA engine is generated by randomly assigning the blocks to the tiers of the system to balance the area of the individual tiers. The SA process progresses by swapping blocks between two tiers (for single step approaches) or changing the location of the blocks within one tier. A candidate solution is therefore perturbed by selecting a tier within the 3-D stack and applying one of the moves described in [337]. The expected wirelength and number of vertical vias are reevaluated after each modification of the partition (which can be a computationally expensive step, as mentioned in the previous section), where the algorithm progresses until a floorplan is obtained at the target low temperature of the SA algorithm.

Application of the technique in [352] (with bounded but not fixed TSVs) to the MCNC and GSRC benchmark suites [355] with a comparison to the TCG-based 2-D array and the combined bucket and 2-D array techniques (CBA) [351] is provided in Table 9.2. A small reduction, on the order of 3%, in the number of vertical vias and a significant reduction of approximately 14% in wirelength is exhibited, while the total area increases by almost 4% for certain benchmark circuits.

Table 9.2

Multistep Floorplanning Results [352]

| Benchmark | TCG-Based 2-D Array | CBA | Multistep Floorplanning | ||||||

| Area | Wirelength | Vias | Area | Wirelength | Vias | Area | Wirelength | Vias | |

| ami33 | 3.52E+05 | 23,139 | 106 | 3.44E+05 | 23,475 | 111 | 4.16E+05 | 21,580 | 108 |

| ami49 | 1.49E+07 | 453,083 | 191 | 1.27E+07 | 465,053 | 203 | 1.42E+07 | 420,636 | 198 |

| n100 | 53,295 | 97,066 | 704 | 51,736 | 90,143 | 752 | 54,648 | 74,176 | 733 |

| n200 | 51,714 | 198,885 | 1487 | 50,055 | 175,866 | 1361 | 55,944 | 142,196 | 1358 |

| n300 | 74,712 | 232,074 | 1613 | 75,294 | 230,175 | 1568 | 79,278 | 213,538 | 1534 |

| Avg. | 1.00 | 1.17 | 1.03 | 0.96 | 1.14 | 1.02 | 1.00 | 1.00 | 1.00 |

Although the techniques discussed in this section utilize a different metric for wirelength, both the HPWL and the probabilistic wirelength estimate in [352] neglect the increase in wirelength due to the placement of the TSVs and the wires. Including the effect of the TSVs in the floorplanning process requires different metrics and approaches, as discussed in the following subsection.

9.2.2 Floorplanning Techniques for Three-Dimensional ICs With Through Silicon Via Planning

The complexity of 3-D integration requires different wirelength metrics and advanced cost functions that include several objectives beyond area and wirelength (A/W) to produce efficient floorplans for 3-D circuits. These objectives can consider, for example, the communication throughput among the circuit blocks and/or the number of intertier vias. The effect of utilizing more accurate metrics than the traditional model of the half perimeter of the bounding box of the nets to estimate the length of the intertier nets is discussed in Section 9.2.2.1. Approaches to integrate TSV planning with the floorplanning process are presented in Section 9.2.2.2, while techniques treating the TSV planning as a post-floorplanning step are reviewed in Section 9.2.2.3. Practical issues in inserting TSVs within whitespace also used by other resources are considered in Section 9.2.2.4, where some nonconventional approaches to floorplanning are briefly mentioned.

9.2.2.1 Enhanced wirelength metrics for intertier interconnects

In addition to the cut size or, equivalently, the number of connections between tiers, the processing technique to bond the tiers of a 3-D circuit also affects the partition step in a multistep floorplanning methodology. The various bonding mechanisms employed in a 3-D system contribute in different ways to the final floorplan as these bonding styles support different densities of vertical wires (i.e., TSVs) with dissimilar electrical characteristics.

For example, front-to-front bonding produces a large number of short intertier vias, improving the performance of those modules with a high switching activity. Furthermore, a block with a large area can be divided into two smaller blocks assigned to adjacent tiers and employ front-to-front bonding to minimize the effect of the physical separation on the performance and power consumption. Alternatively, intertier vias utilized in front-to-back bonding can adversely affect the performance of a 3-D system if not used with caution due to the overhead in active area of these interconnections. In addition, TSVs require a different approach for determining the wirelength of a 3-D system. This situation occurs if a TSV is placed outside the bounding box of the net containing the TSV.

To better explain this situation, an example is depicted in Fig. 9.7 where blocks within a three-tier system are illustrated. A net connects the pins p1,1, p1,2, and p1,3, (depicted with solid squares), respectively, of blocks b1, b2, and b3, employing TSVs v1,12 and v1,23 (depicted with solid circles). In Fig. 9.7A, all of the pins of this net across the stack are projected onto tier 1. The projected pins from tiers 2 and 3 are shown with empty squares. If the classic HPWL is employed to determine the length of this net, this length is LHPWL=w+h, as determined by the rectangle drawn with a dashed-dotted line. HPWL, however, does not include the segments of the nets to the TSVs, thereby, for this specific example, underestimating the length. To address this issue, the bounding box of the net assumed in Fig. 9.7A is extended to include the TSV locations [357]. The new bounding box plotted in Fig. 9.7B with the dotted line results in a new length equal to LHPWL-TSV=w′+h′ which is greater than LHPWL. To determine LHPWL-TSV, all of the pins and TSVs are projected onto a single tier, tier 3 in this specific example. If the location of the TSVs is contained within the dashed-dotted bounding box of the net shown in Fig. 9.7A, LHPWL=LHPWL-TSV. This situation is however unlikely to occur, in particular if floorplanning is at the block level, where longer interconnects typically occur. Although including the TSV locations when determining the length of the nets produces a better estimate as compared to HPWL, greater accuracy is achieved if the individual segments of the net in each tier are considered. In this approach, the bounding box—typically between a pin and a TSV—is determined for each tier. Consequently, the total length of the net is LHPWL-NET-SEG=(w1+h1)+(w2+h2)+(w3+h3), where the length of each segment is assumed to be the HPWL of the bounding box of this segment depicted by the dashed lines. Note that, for this example, LHPWL-TSV=(w2+h2) < LHPWL-NET-SEG.

All of these metrics have been used to estimate wirelength during floorplanning of 3-D circuits. Intuitively, these metrics produce similar results if the floorplanning process generates whitespace close to the pins connected to the intertier wires. The TSVs in this case can be placed within the bounding box determined solely by the pins projected onto a single tier. Furthermore, the whitespace does not include a single TSV but rather several TSVs; therefore, the notion of a TSV island is introduced [357]. Each TSV island is associated with a capacity, which can be adapted to accommodate a greater number of TSVs without incurring a considerable length overhead for certain nets. In this case, the center of the island determines the vertex of the bounding box rather than a single TSV. Consequently, the TSVs can have a nonnegligible effect on the length of the intertier nets, which should be considered when floorplanning a 3-D circuit, as discussed in the following subsection.

9.2.2.2 Simultaneous floorplanning and through silicon via planning

These advanced wirelength metrics are useful to perform accurate TSV planning for 3-D floorplans while producing short wirelengths to achieve a target stack. The steps of a general floorplanning methodology including TSV planning are illustrated in Fig. 9.8, where an SA engine and SP representation produce candidate floorplans. The input of the process includes: (i) a set of blocks with fixed dimensions (fixed aspect ratio), (ii) a netlist indicating connections among the blocks, (iii) the dimensions and number of tiers, and (iv) the physical parameters of the TSVs for the target technology. The objective of the technique is to determine: (1) the coordinates of each block including the tier number, (2) the coordinates and size of the TSV islands, and (3) for every TSV within each tier, the TSV island in which a TSV is allocated. Related constraints are: (1) no block coordinate can exceed the dimensions of the tier (assuming a fixed outline), (2) no block overlap is allowed, and (3) the total area of the TSVs assigned to a TSV island does not exceed the area of this island.

The process, shown in Fig. 9.8, proceeds as follows. A floorplan is randomly produced and successive perturbations are performed to generate low cost floorplans, where the cost function is [357]

(9.9)

The last term penalizes any change in the aspect ratio of the floorplan. Note that this expression does not differ considerably from (9.6) used in 2-D circuits. The area now includes, however, the area of the TSVs, and the wirelength metric LHPWL-TSV is considered rather than LHPWL.

The perturbations of a solution are based on the notion of slacks, as described in Section 9.1, where the horizontal and vertical slack for each block is determined. The perturbations include: (1) intertier swapping of a block or a pair of randomly chosen blocks, and (2) moves of blocks between tiers to balance the area among the tiers. The blocks in congested tiers are given a higher probability to be relocated. (3) The spatial slack information is used to perform a block move, where blocks of opposite slack are placed close to each other.

Based on the floorplan produced after applying these perturbations, the cost function shown in (9.9) determines whether the most recent iteration of the floorplan is accepted. If accepted, the TSV planning step commences. This step progresses by assigning in a greedy way a TSV into a TSV island. As the annealing temperature cools, a more detailed TSV assignment follows. During the greedy assignment process for each intertier net, the bounding box (see Fig. 9.7B) can contain several whitespaces, which are used as TSV islands. If several of these TSV islands for a tier exist, a TSV is placed within any of these islands with equal probability, yielding no increase in wirelength. This practice may, however, lead to some islands with more TSVs than is physically possible. The area of these islands is expanded to fit the excessive number of TSVs. The resulting overlap between the TSV islands and surrounding blocks is resolved during the finer assignment step. The reason for allowing the overlap is that no increase in wirelength occurs if as many TSVs as possible are kept within those islands contained within the bounding box of a net. The increase in area, however, should not outweigh the savings in wirelength.

Consequently, the stage of TSV refinement uses two pieces of information to decide how best to allocate the TSVs into an island. The TSVs are sorted according to the total area of the candidate TSV island(s) where a TSV is placed. Candidate TSV islands are contained within the bounding box of a net, as illustrated in Fig. 9.9, where some noncandidate TSV islands for a specific net are also shown. The smaller the area of the island, the higher the priority for a TSV. As this island can be more quickly filled, the TSV may be placed within another TSV island, potentially beyond the bounding box. To avoid these expensive placements, if the candidate island for a TSV has been filled, allocation of this TSV is deferred to a later step in the process.

At the end of this stage, some TSVs may not have been assigned to any of the candidate TSV islands. Two options can be followed, either expanding the area of a candidate TSV island or assigning one TSV to a noncandidate TSV island (i.e., a TSV island not inscribed within the bounding box of the net containing the TSV). In both cases, the wirelength relates to the nets crossing the expanded TSV island or the additional wire segment needed to reach the noncandidate island. A linear cost function to consider the increase in wirelength caused by either option is used in [357]. The option with the lower cost is selected, leading to an iteration to produce a floorplan if an expansion is chosen. If the additional wire connecting a pin to a TSV island outside the bounding box of the net is longer than the increase in wirelength due to the expansion of a candidate TSV island, the latter option is chosen. The computational cost required to generate a new floorplan should however be considered. In addition, this choice implicitly favors wirelength reduction over area minimization, which may increase the difficulty of the SA algorithm to produce a high quality floorplan, particularly if greater emphasis is placed on the area or aspect ratio term in (9.9).

A limitation of this flow is that the TSVs are treated individually, potentially leading to suboptimal results. To improve the quality of the solution, another stage of TSV reassignment, notated as stage II in Fig. 9.8, is added to the flow, where the main task is to reassign TSVs among the TSV islands. The area and number are fixed to further reduce the wirelength. The task is formulated as a minimum cost maximum flow problem which can be optimally solved in polynomial time [358].

The technique described in [357] has been applied to benchmark circuits used in physical design problems, such as the ami, n100, n200, and n300 benchmark circuits, and is compared with a TSV unaware floorplanning method where the length of the nets is LHPWL. In addition, the location of the TSVs is considered after a floorplan is generated and not during the floorplanning process. These results, listed in Table 9.3, demonstrate improved wirelength while satisfying a fixed outline constraint with an increase in computational time (attributed to the TSV planning steps within the floorplanning process).

Table 9.3

Flooplan With and Without TSV Planning [357]

| # of Tiers | Circuit | TSV Aware | TSV Unaware | ||||||

| Success Rate | Avg WL | TSVs | Time (s) | Success Rate | Avg WL | TSVs | Time (s) | ||

| 3 | n100 | 100% | 160,825 | 833.2 | 1195.91 | 80% | 157,480 | 888.8 | 22.68 |

| 3 | n200 | 100% | 310,924 | 1509.1 | 7720.45 | 0% | 339,768 | 1689.5 | 87.38 |

| 3 | n300 | 100% | 424,585 | 1899.7 | 21155.10 | 0% | 440,954 | 2019.3 | 159.02 |

| 4 | n100 | 100% | 148,748 | 1171.4 | 1306.39 | 90% | 165,940 | 1290.5 | 23.38 |

| 4 | n200 | 100% | 291,091 | 2179.0 | 8237.10 | 0% | 367,602 | 2431.5 | 94.45 |

| 4 | n300 | 100% | 391,694 | 2730.6 | 21450.50 | 10% | 448,905 | 2865.0 | 234.12 |

9.2.2.3 Through silicon via planning as a post-floorplanning step

A different path to plan and insert TSVs can also be followed where the size of a TSV island is insufficient to fit the assigned TSVs. In the previous subsection, this situation is handled by increasing the size of the whitespace or allocating a TSV to an island located farther away. The increase in size of the TSV islands is considered in the next floorplanning iteration. Alternatively, this increase can be achieved by avoiding a floorplanning iteration if area is borrowed from other whitespace regions. Although this borrowing shifts blocks, this process can be performed by shifting only specific blocks in the vicinity of this island rather than floorplanning the entire circuit. In this way, any fixed outline constraint is easily satisfied. To perform these block shifts, however, information describing the slack of all of the blocks of the circuit should be available. The technique, discussed in [339], utilizes this information to treat TSV planning as a post-floorplanning step.

A fixed outline 3-D floorplan with no overlaps among blocks is the primary input of this technique, where the coordinates of each block are xb and yb, and nb is the physical tier in which the block is placed. Other inputs include the number of TSV islands, where each island has a specific capacity and dimensions (hTSV_island, wTSV_island), and a netlist describing the connections among the blocks. As LHPWL-NET-SEG provides an improved estimate of the wirelength, this metric is employed to determine the total wiring of the circuit. Although LHPWL-NET-SEG is a better estimate, LHPWL-TSV is faster to determine and is, therefore, used if the granularity of the floorplanning/placement is at the gate level rather than at the block level. Employing TSV islands at the gate level results in unacceptably long wires since the TSV should be placed adjacent to the connecting cell. Additionally, at the block level, providing capacity for each TSV island is not a straightforward task and can affect the quality of the overall floorplan. The decision for the TSV island capacity can be based either on user experience or on a probabilistic allocation of capacities similar to the assignment process of inserting TSVs into islands [357]; however, no evidence exists as to whether these input parameters affect the resulting floorplan.

The approach of [339] clusters intertier connections to TSV islands, and assigns each of these clusters to a whitespace. The clustering step employs the notion of a “virtual die,” which is depicted in Fig. 9.10. The bounding box of the nets is projected onto the virtual die, and the intersection of several boxes forms a cluster with the respective nets. The capacity of the available TSV islands determines the number of clustered nets or, alternatively, the number of bounding boxes projected onto the virtual die of a TSV island.

An intersection graph is defined to determine the intersection of the overlapping bounding boxes, where the vertices correspond to bounding boxes while overlaps among blocks are expressed by edges. To determine the common region, a number of cliques are determined where the size of each clique satisfies the capacity of the target TSV islands. This step is NP-complete [359].

With the area of the whitespace across each tier known, the TSV islands are assigned to these areas where some whitespace may not be used for a TSV island or can be shared by more than one TSV island. Additionally, a net can include more than one TSV contained within several TSV islands. As previously discussed, the TSV assignment process can be achieved probabilistically or with some dynamic metric which considers the decreasing available whitespace as the TSV assignment process proceeds. An example of this metric is

(9.10)

which considers the available whitespace of a cluster as compared to the number of assigned nets within a cluster. Although clusters with high scores are prioritized to reduce the number of unassigned nets, by the end of the process, nets can exist which have not been assigned to a cluster. Failing to insert a TSV island means that greater whitespace is necessary, which can be achieved through two different schemes [339]. Additional whitespace can be made available by adding channels of whitespace between blocks to accommodate the TSVs as well as buffers and local logic. This straightforward method increases the overall area of the floorplan. Alternatively, the available whitespace can be redistributed to provide the required area within each tier.

Greater whitespace can be achieved by shifting the blocks, which eliminates unnecessary use of whitespace (for example, outside the common region of the projected bounding boxes of the nets, see Fig. 9.10B), thereby increasing the available area for other islands. Block shifting is performed in two ways, producing successful TSV assignments, where (1) the blocks are shifted at the beginning of the TSV planning process, and (2) the blocks are successively shifted during the TSV island insertion step. To determine the available shifting opportunities, the notion of spatial slack is used as previously discussed. The use of slack allows the fragmented and otherwise unsuitable whitespace to be consolidated among blocks in the x and y directions without increasing the area, leading to a more compact floorplan.

Experiments on standard benchmark circuits have shown that initial shifting performs better than iterative shifting in terms of the total wirelength, although the latter shifting is performed dynamically. A rationale for this preference is that during initial shifting none of the TSV islands has been assigned and full slacks can be exploited, albeit only once. During iterative shifting, the gradual insertion of TSV islands quickly dissipates the available slack, decreasing the likelihood of redistributing whitespace to provide additional space for the remaining TSV islands. Alternatively, channel insertion is achieved by first proportionally inflating the dimensions of the blocks and then contracting the blocks to the original dimensions after a floorplan is produced. The increased whitespace can, in this case, efficiently fit the TSV islands; yet an approximately 10% increase in the total area of the circuit is incurred. Moreover, the total wirelength is shorter due to iterative block shifting but longer than from the initial block shifting.

Note that all of the techniques discussed in this section assign a group of TSVs to some empty space but do not assign individual TSVs within this space (this problem is considered in Chapter 10, Timing Optimization for Two-Terminal Interconnects, and Chapter 11, Timing Optimization for Multiterminal Interconnects, where early timing driven techniques for TSV placement are presented). The coordinates at the center of the TSV islands are used to provide wirelength estimates, resulting in pessimistic estimates and potentially producing a suboptimal placement of TSVs.

Although enhanced wirelength metrics and TSV islands improve the quality of the floorplan, inserting TSV islands can still fail despite increasing the floorplan. This limitation can be alleviated if an alternative approach is followed, where the pins of the block, the bounding box of the nets, are moved along the boundary of the blocks to provide greater flexibility in allocating TSVs within each tier. Alternatively, pin assignment for each block is another degree of freedom to reduce wirelength. Moving pins leads to disparate bounding boxes that contain more or larger capacity TSV islands. This approach is also applied as a post-floorplanning technique to minimize wirelength, where the solution to the optimization problem places both the TSVs of the intertier net as well as the pins of each block [360]. The technique adapts the problem to ensure that a minimum cost maximum flow algorithm is applied. A solver with a time complexity of O(|V|2|E| log(C|V|)), where V and E denote the vertices and edges of the related graph constructed for the target problem and C is the maximum cost of the arcs within the graph [358]. The technique optimally solves the case where a block is connected to several blocks through single and/or multiple fan-out nets. The algorithm determines the position of the pins and TSVs to minimize the wirelength of the nets. Alternatively, for the algorithm to be optimally solved, the multipin nets can be decomposed into several two-pin nets. This task requires the use of additional source terminals. The technique proceeds by replicating pins for the specific net at the source block. Once the minimum cost maximum flow algorithm terminates, the replicated pins are mapped back into the original pin, which can produce a nonoptimal floorplan. Furthermore, in practical systems, blocks are connected in many different ways. Many blocks behave both as a source and destination for different nets. A straightforward procedure to cope with this issue is to successively apply the single block source—multiple block destinations problem to all blocks within a system where the blocks are randomly chosen. The optimality of this process is however not guaranteed. In addition, HPWL is used as the wirelength metric which performs poorly in 3-D circuits. Consequently, although the technique reduces the wirelength by simultaneously manipulating pins and TSVs, additional space for decreasing the wirelength is possible through enhanced TSV planning.

9.2.2.4 Practical considerations for floorplanning with through silicon via planning

The use of whitespace has to date been limited to the important resource of TSVs. Unoccupied regions in 2-D circuits have, however, traditionally been used for repeaters and decoupling capacitors, particularly in the case where the circuit is comprised of hard macros. Consequently, in 3-D circuits, repeaters and TSVs share the same whitespace. Furthermore, TSV planning techniques which only focus on assigning TSVs to the available whitespace do not consider the effect that this assignment can have on the non-optimal placement of repeaters for intertier nets. Since these nets tend to be the longest interconnect in a multitier system, this situation can degrade system performance. To address this problem, repeaters and TSVs should be simultaneously placed to better utilize the available whitespace.

Employing the concept of (independent) feasible regions [361,362], the largest polygon should be placed to satisfy local timing constraints. Simultaneous buffer and TSV insertion improve timing closure for these intertier nets [363]. If this feasible region overlaps the whitespace, the intersection between these two areas represents a valid location for these buffers. The intertier nets, however, require a different treatment as the feasible regions should be determined for each tier before placing buffers in those tiers. Consequently, a two-step process is followed where the feasible regions for each tier spanned by the target net are determined, while simultaneously, TSVs are inserted within these regions.

The second step is allocating buffers and TSVs to each tier. To better describe this process, an example of an intertier net is illustrated in Fig. 9.11, where the pins of the net are in tiers one and three, and k buffers are assumed to be needed. The feasible region for the second tier is shown in Fig. 9.11. The feasible regions within each tier are similarly determined. Since all of these regions are candidates for buffers driving the same net, a buffer connection graph is employed to link these regions together. An example of this graph is shown in Fig. 9.11B for the net depicted in Fig. 9.11A. The rows in this graph represent the tiers spanned by the net, and the columns represent the number of inserted buffers (k=3 in this example). Thus, the vertex indicated by (rowi, columnj) means that the jth buffer can be placed in tier i. A vertex does not exist in (row1, column3), which means that the third buffer cannot be placed in the feasible region of that tier. The edges of the graph indicate whether a TSV can be placed within the feasible regions of the tiers connected by this TSV. The projections of the two feasible regions from two adjacent tiers intersect, resulting in a nonempty (available) area for placing a TSV. In this example, edge e means that a TSV can be placed between tiers 1 and 2 connecting the buffers in the corresponding feasible regions while satisfying existing timing constraints. The edges among vertices in the same row simply indicate that routes between buffers of the same tier are possible.

With this graph describing the connections of the buffers and TSVs, the location of these items need to be determined, preferably in a form of a path connecting the pins of a net. An example path is illustrated in Fig. 9.11C, where other paths are also shown. The choice of the path is supplemented by other objectives in addition to timing and wirelength, such as congestion, by adapting the weight of the edges. The path with the lowest cost is chosen for each net.

The complexity of this technique is O(mn2Mbuf), where m is the number of nets, n is the number of tiers, and Mbuf is the greatest number of buffers required for a net among the P interconnections. Considering that the complexity of the method is linear with the number of nets and that the number of buffers and tiers are low, buffer and TSV planning can be integrated with floorplanning. Similar to other techniques, whitespace redistribution offers a means to further improve the efficiency of this technique. A heuristic is employed [357] based on the constraint graphs along the two physical directions x and y, which provide the spatial slack of each block as in [339]. This heuristic, however, does not shift any of the blocks during the TSV allocation process but rather assigns a TSV to a region, expanding the area of the whitespace during subsequent floorplanning iterations.

The blocks can be shifted only after all of the TSVs and buffers have been allocated. Breadth first traversals along the horizontal and vertical directions within each tier are applied to expand the feasible regions based on spatial slack information. If the greatest possible shift of blocks does not enable the assignment of all TSVs, the floorplan is perturbed, initiating a new iteration. SA is utilized for floorplanning but the typical linear cost function is extended and annealing proceeds in three different stages, where a different cost function is utilized to emphasize a different objective. Thus, the first stage emphasizes area as the modules are initially far apart (high temperatures of the annealing process). As the compactness of the floorplan increases, timing is also added to the cost function, as described by

(9.11)

where the timing violations are included in the cost function. If during this phase, the temperature slowly decreases, another term is added to the cost function (which constitutes the third stage) which satisfies the timing of those intertier wires with unassigned buffers and TSVs. Note that the same perturbations as in [352] are applied, where intertier moves for blocks are disallowed.

The performance of the simultaneous treatment of buffers and TSVs has been explored on two MCNC and other synthetic benchmark circuits. Some of these results are reported in Table 9.4, where these benchmark circuits are floorplanned in a single tier without (F2D/NWR) and with whitespace redistribution (F2D/WR) using the SA approach from [356]. These results are compared to the 3-D floorplanner without (F3D/NWR) and with (F3D/WR) whitespace redistribution where a four tier system is assumed. A comparison of the A/W for these scenarios shows that F3D/WR performs best where redistributing the whitespace slightly improves the floorplans (4.8% and 2.4% for, respectively, wirelength and area). The disadvantage of whitespace redistribution is, however, a higher number of buffers and TSVs, as listed in, respectively, columns 9 and 10 to improve the timing of the circuit. Therefore, additional nets can satisfy the timing requirements, as listed in columns 11 and 12 of Table 9.4.

Table 9.4

Comparison of 2-D and 3-D Floorplans With and Without Whitespace Redistribution for Simultaneous Buffer and TSV Planning [363]

| Circuit | Area (mm2) | Wirelength (mm) | B/#B | Net Timing Met | Net Timing Failed | Area (mm2) | Wirelength (mm) | TSV/#TSV | B/#B | Net Timing Met | Net Timing Failed |

| F2D/NWR | F3D/NWR | ||||||||||

| ami33 | 1359.16 | 5922.63 | 52.30% | 241 | 70 | 1317.72 | 3937.08 | 76.29% | 58.48% | 279 | 84 |

| ami49 | 1373.10 | 8921.08 | 79.73% | 353 | 156 | 1095.68 | 5781.72 | 79.37% | 68.16% | 381 | 164 |

| F2D/WR | F3D/WR | ||||||||||

| ami33 | 1251.02 | 5745.40 | 33.05% | 213 | 43 | 1350.52 | 3519.18 | 92.17% | 86.04% | 317 | 46 |

| ami49 | 1067.57 | 9663.90 | 68.35% | 330 | 188 | 1068.64 | 5185.88 | 95.85% | 94.33% | 432 | 113 |

9.2.2.5 Microarchitecture aware three-dimensional floorpanning

Before closing this discussion on the various aspects of 3-D floorplanning, it is worth noting that disruptive approaches for floorplanning 3-D circuits have been developed, where the length of the nets is weighted differently. Thus, a communication-based objective can utilize information from the microarchitectural level, resulting in floorplans with a higher number of instructions per cycle (IPC) [364]. In a 3-D system, blocks that communicate frequently can be assigned to adjacent tiers, decreasing the interconnect length of the interblock connections. The communication throughput is also increased while reducing the power consumed by the system. Alternatively, blocks with high switching activities should not overlap in the vertical direction to ensure that the temperature profile of the system remains within specified limits. Consequently, the communication throughput is carefully balanced with operating temperature.

A multi-objective floorplanning approach targeting microprocessor architectures is illustrated in Fig. 9.12, where a variety of tools characterize different parameters of the functional blocks within a processor. The CACTI [365] and GENESYS [366] tools provide an estimate of the speed, power, and area of the processor. The SimpleScalar simulator [367] combined with the Watch [368] framework records the information exchanged across the system to predict the power consumption of each benchmark circuit. A hierarchical approach is utilized where the SA engine is replaced by a slicing algorithm based on recursive bipartitioning [369]. This algorithm distributes the functional blocks of the processor onto the tiers of the 3-D stack to decrease computational time.

The additional objectives include area and wirelength (A/W), area and performance (A/P), area and temperature (A/T), and area, performance, and temperature (A/P/T). Based on evaluating MCNC/GSRC benchmark circuits, A/W achieves the minimum area as compared to the other objectives, decreasing by almost 40% the interconnect length as compared to a 2-D floorplan of the same microarchitecture. A/P increases the IPC by 18% over A/W, while simultaneously increasing the temperature by 19%. The more complex objective A/P/T generates a temperature close to A/W, while the IPC increases by 14%. In general, the performance generated by the A/P/T objectives is bounded by the performance provided by the A/T and A/P objectives. In addition, A/P/T achieves higher performance as compared to A/W with a similar temperature [364].

9.3 Placement Techniques

Placement algorithms traditionally target minimizing the overall area of a circuit and the interconnect length among the cells, while reserving space for routing the interconnect. A brief discussion of the different approaches used for placing 2-D circuits is offered in this section, where specific techniques are described in greater detail to provide the necessary background for applying 2-D placement techniques to 3-D circuits.

As with floorplanning, SA is also applied to placement problems [370], but the large number of cells in the placement step as compared to the fewer number of blocks during floorplanning can result in excessive computational time [371]. Other placement methods are based on partitioning, where the netlist and area of a circuit are successively partitioned, minimizing the number of connections between juxtaposed partitions during each partitioning step. Some placers rely on partitioning methods including, for example, Capo [372] and Fengshui [373].

In addition to stochastic and min-cut placement methods, another category includes analytic-based placers where an appropriate cost function is optimized for a specific single objective or multiple objectives through a combination of diverse optimization methods. The cost functions can be, in general, nonlinear and quadratic (as compared to typical linear cost functions assumed in SA-based techniques). Examples of nonlinear placers include NTUplace [374] and mPL [375].

In quadratic placement, the wirelength is described as a quadratic cost function which can be optimized effectively through a system of linear equations. Quadratic placement is based on several methods, such as partitioning [376], force directed [377,378], and warping [379]. In partition-based methods, the cost function is optimized at each level of the partition to place the blocks and/or cells with minimum wirelength [376]. Alternatively, in warping, the outline of the circuit is changed to indirectly move the circuit blocks during placement [379].

Alternatively, the force directed method applies diverse forces to bring the modules closer or to spread them apart, depending upon the intended objective [380]. Several placers based on the force directed method have been developed for 2-D circuits and exhibit useful results. This method has been employed for placement within multitier systems, where objectives unique to these systems are considered. Before discussing these extensions to 3-D circuits, the basic characteristics of the force directed method are reviewed in the following subsection, providing background for this method.

9.3.1 Placement Using the Force Directed Method

The force directed method is utilized in several placement algorithms due to the low computational time to produce a legal placement. Attractive or repelling forces are applied to each of the components (cells or blocks comprised of many cells) being placed. These components are successively moved within a specified area until the forces cancel each other.

Using an analogy from physics, the components can be thought of as being connected through elastic springs exerting forces on these components. A placement is produced when this system of elastic springs reaches a state of minimum energy. Since the derivative of energy is force, this state of minimum energy is achieved when the position of the components ensures that the sum of forces among the components is zero.

To determine the position(s) of equilibrium (or minimum energy) for the components comprising a circuit, a system of linear equations is solved. A large variety of analytic and numerical methods exists to solve this system, each with different computational efficiencies. The quality of the placements, however, depends primarily on the accuracy of the model of the forces characterizing the different properties or, equivalently, placement objectives of the circuit.

The primary circuit parameter modeled as a force is the interconnect length between components, where a force corresponds to a two pin connection between a pair of components. A wirelength model is used, as with floorplanning, since the length is not known at the time of placement. The choice of model is crucial, affecting both the quality of the placement and speed of convergence. Based on these observations, the main steps of force directed placement methods are described in this section, starting from a basic (and early) formulation towards more complex expressions that incorporate more forces in addition to a wirelength driven force.

Application of the force directed method to the placement problem begins by considering a number of components N comprising a circuit. This set can be further distinguished into movable Nm and fixed Nf location components. Fixed components can, for example, refer to hard macros, where the positon on the x–y plane is constrained due to timing or I/O requirements. The position of each component i is described by the coordinates at the center of this component (xi, yi) where another subscript (m or f) is used whenever necessary to indicate whether the component i is movable or not. With this notation, the position of all of the components and placement is described by a 2N-dimensional vector,

(9.12)

A quadratic cost function to minimize wirelength is a primary objective for placement. The Euclidean distance among pairs of blocks is a suitable metric to describe the length of the connections among the blocks. Note that this wirelength model is quite different from the Manhattan distance used to describe routes in integrated circuits and the net models discussed in Section 9.1 used in floorplanning. Based on the model of a Euclidean distance, the overall cost of a placement in matrix notation is [371]

(9.13)

where C is a 2N×2N symmetric matrix and ![]() is a 2N-dimensional vector. The derivative of (9.13) is

is a 2N-dimensional vector. The derivative of (9.13) is

(9.14)

yielding a system of linear equations. Setting (9.14) equal to zero and solving for ![]() provides the position of the components that minimizes (9.13). This system of equations is only true if B is convex, which is ensured if C is positive definite or semidefinite. This property of C applies to systems that include both only movable [381] and a mixture of movable and fixed location components [382]. In addition, the cost function of (9.13) is separable into x- and y-directions, permitting each direction to be treated independently.

provides the position of the components that minimizes (9.13). This system of equations is only true if B is convex, which is ensured if C is positive definite or semidefinite. This property of C applies to systems that include both only movable [381] and a mixture of movable and fixed location components [382]. In addition, the cost function of (9.13) is separable into x- and y-directions, permitting each direction to be treated independently.

The elements of matrix C and vector ![]() are formed by considering the Euclidean distance (or any other appropriate (quadratic) wirelength model) between pairs of movable components and pairs of one movable and one fixed component. These distances are described by

are formed by considering the Euclidean distance (or any other appropriate (quadratic) wirelength model) between pairs of movable components and pairs of one movable and one fixed component. These distances are described by ![]() for any pair of movable components i and j. In the case of fixed components, this expression is adapted to reflect this situation,

for any pair of movable components i and j. In the case of fixed components, this expression is adapted to reflect this situation, ![]() where the subscript f denotes that the j component cannot be displaced. As function B is separable, each direction can be independently solved.

where the subscript f denotes that the j component cannot be displaced. As function B is separable, each direction can be independently solved.

In the following discussion, the x-direction is analyzed by considering the matrix Cx and vector ![]() . A similar treatment applies to the y-direction. Consequently, expanding the squared terms for the x coordinate

. A similar treatment applies to the y-direction. Consequently, expanding the squared terms for the x coordinate ![]() , the first and third terms contribute to the diagonal elements of matrix Cx at, respectively, rows i and j. The second term results in negative entries in matrix Cx at, respectively, rows and columns i and j, and j and i. Vector

, the first and third terms contribute to the diagonal elements of matrix Cx at, respectively, rows i and j. The second term results in negative entries in matrix Cx at, respectively, rows and columns i and j, and j and i. Vector ![]() is formed by expanding the square of the differences between a movable and a fixed component (xif, yif), while the term

is formed by expanding the square of the differences between a movable and a fixed component (xif, yif), while the term ![]() contributes to the constant term in (9.13). The x-direction of (9.13) is

contributes to the constant term in (9.13). The x-direction of (9.13) is ![]() . Similarly, (9.14) is

. Similarly, (9.14) is

(9.15)

where the notation ![]() indicates the force along the x-direction due to connections among the components. If the only applied force is due to the interconnections of components, the resulting placement contains significant overlap among the components. This behavior can be understood by observing that the Euclidean distance decreases by bringing the connected components closer to each other. To avoid illegal placements, other forces can also be included within the cost function. Consequently, (9.14) is recasted as

indicates the force along the x-direction due to connections among the components. If the only applied force is due to the interconnections of components, the resulting placement contains significant overlap among the components. This behavior can be understood by observing that the Euclidean distance decreases by bringing the connected components closer to each other. To avoid illegal placements, other forces can also be included within the cost function. Consequently, (9.14) is recasted as

(9.16)

where vector ![]() describes these additional forces. These forces greatly affect the quality of the placement and should therefore be carefully chosen. For example, the new forces can remove or decrease the overlaps among the components caused by the force

describes these additional forces. These forces greatly affect the quality of the placement and should therefore be carefully chosen. For example, the new forces can remove or decrease the overlaps among the components caused by the force ![]() due to the interconnections. To achieve this objective, a spread force

due to the interconnections. To achieve this objective, a spread force ![]() gradually removes the overlap among components due to the wirelength force acting upon these components. A hold force

gradually removes the overlap among components due to the wirelength force acting upon these components. A hold force ![]() , opposite to the wirelength force

, opposite to the wirelength force ![]() , allows the spread force to iteratively move the components to those locations that nullify forces, thereby minimizing the wirelength. Consequently, the total force applied to the components is

, allows the spread force to iteratively move the components to those locations that nullify forces, thereby minimizing the wirelength. Consequently, the total force applied to the components is

(9.17)

The spread force is also modeled as the force of an elastic spring connected between the present location of a movable component and some other target location, which for the x-direction is [383]

(9.18)

where the vector wx is the spring constant. The spring constant affects the convergence of the placement, and xt are the target locations of the components during a placement iteration. As ![]() reduces the overlap among components, relating the amplitude of this force with the density of the components across the circuit area is a useful approach. Consequently, the target locations relate to the density of components across the circuit area. Thus, this force can be described by a general supply and demand system [371,383], which includes the density of the components as the demand and the available area for placing these components as the supply. A balanced demand and supply system imposes the constraint,

reduces the overlap among components, relating the amplitude of this force with the density of the components across the circuit area is a useful approach. Consequently, the target locations relate to the density of components across the circuit area. Thus, this force can be described by a general supply and demand system [371,383], which includes the density of the components as the demand and the available area for placing these components as the supply. A balanced demand and supply system imposes the constraint,

(9.19)

(9.19)

(9.19)

To determine the demand of the components at each point (x, y), a rectangle function R is used, leading to

(9.20a–c)

(9.20a–c)

(9.20a–c)

where xll and yll are the coordinates of the lower left corner of a component with width w and height h. From R the demand for component i at point (x, y) is

(9.21)

where the component i is located at (![]() ,

, ![]() ) (the center of the component is described by this point) with dimensions wi and hi. The coefficient dcomp,i captures the density of each component and is set to one in [383], where this coefficient is also used to remove/add some whitespace around each component. Based on these definitions, the total demand at (x, y) is equal to the number of components placed at that point, assuming that dcomp,i=1,

) (the center of the component is described by this point) with dimensions wi and hi. The coefficient dcomp,i captures the density of each component and is set to one in [383], where this coefficient is also used to remove/add some whitespace around each component. Based on these definitions, the total demand at (x, y) is equal to the number of components placed at that point, assuming that dcomp,i=1,

(9.22)

(9.22)

(9.22)

including both the movable and fixed location components. Similarly, the supply at each point across the placement area is

(9.23)

where the lower left corner of the circuit area is at (xchip, ychip) and the dimensions of the circuit are (wchip, hchip). The coefficient dsup is determined by considering the ratio between the area of the blocks over the overall available area for the circuit,

(9.24)

(9.24)

(9.24)

where Achip=wchip hchip. Based on these expressions, the overall supply and demand system is

(9.25)

which is treated as charge distribution with a nonzero value within Achip. This “charge” produces some electrostatic potential across the circuit area, which can be determined by solving Poisson’s equation. With the appropriate boundary conditions (typically Dirichlet boundary conditions), a unique solution exists for the electrostatic potential through

(9.26)

Based on (9.19) to (9.28), the target locations xt can be determined. Solving (9.26) however increases the computational time. If the gradient of the potential determines where to move the block, this increase in time can be avoided. The target location for a component i is therefore

(9.27)

The hold force ![]() is opposite to the wirelength force,

is opposite to the wirelength force,

(9.28)

Having defined all constituent forces, (9.17) is equated to zero and the placement of the components is determined. An iterative process is required as the target points depend upon the existing location and density of each of the components, as described by (9.19) to (9.26). Consequently, an initial placement is obtained by solving (9.14) when only the wirelength force is present. As only this force is applied, the component placement exhibits significant overlap. This initial placement is later refined until the overlap of the components is reduced to a user defined level (e.g., 20% in [383]). During this iterative refinement process, the potential Φ is used to compute the target locations (xt, yt). Expression (9.17) is set equal to zero and solved, producing a new location for the components, thereby modifying the density D and, in turn, potential Φ. The process is repeated until the overlap constraint is satisfied. A final detailed placement can be employed to remove any remaining overlaps.

The quality of the solution as well as the speed of convergence for the force directed method is a function of specific parameters integrated within the expressions characterizing the different forces. For example, the spring constant in (9.18) moves components at a greater or shorter distance. A definition of this coefficient is

(9.29)

where Aavg is the average area of the components. This definition encourages moving higher area components to greater distances as compared to moving smaller components. Furthermore, the coefficient can remain constant during the entire placement procedure or adjusted during each iteration, offering placements of higher quality. The disadvantage of this dynamic adjustment process is increased computational time. Another important parameter that affects the quality of these results is the choice of wirelength model. An elaborate model is used in [383]. Net models for 3-D circuits are revised to include TSVs, as discussed in the following section.

9.4 Placement in Three-Dimensional ICs

In vertical integration, a “placement dilemma” arises in deciding whether two circuit cells sharing a large number of interconnects can be more closely placed within the same tier or placed on an adjacent physical tier, decreasing the interconnection length. Placing the circuit blocks on an adjacent tier can often produce the shortest wire connecting these blocks. An exception is the case of small blocks within an SiP or system-on-package (SOP) where the length of the intertier vias is greater than 100 μm. Since intertier vias consume silicon area, possibly increasing the length of some interconnects, an upper bound for this type of interconnect resource is necessary. Alternatively, sparse utilization of the intertier interconnects can result in insignificant savings in wirelength.

Several approaches have been adopted for placing circuit cells within a volume, including SA as the core solving engine, force directed placers, and analytic placement [384–387]. Some of these techniques also consider the TSV placement process simultaneously with placing the circuit cells. In the following subsections, placement tools based on these methods are discussed.

9.4.1 Force Directed Placement of Three-Dimensional ICs

The force directed placement method presented in Section 9.3.1 has been extended to perform placement for multitier circuits, where the placement occurs at the cell level. As the third physical dimension is introduced in 3-D circuits, the exerted forces need to be properly adjusted. Additionally, similar to floorplanning techniques for 3-D circuits, the TSVs require different approaches, simultaneously placing the TSVs with the circuit cells or following the cell placement step. Other issues specific to TSVs, such as crosstalk between TSVs, can also be considered by modifying or adding new forces to the classic formulation of the force directed method. These topics are the foci of this subsection.

Since the location of circuit cells in a 3-D system is described by three coordinates (x, y, z), the inclusion of the z-direction in (9.13) is a reasonable yet not straightforward extension. The issue stemming from including a wirelength force ![]() is that this force may collapse the majority of the cells into a tier containing the I/O terminals (as these terminals are typically located in only one tier). Mitigating this behavior may require a significant change in the algorithm. Alternatively, a partition step can be employed to place the cells among the tiers. The partition step, which can reduce or maximize (depending upon the partition objective) the number of TSVs, eliminates the need for