2.1 INTRODUCTION

- Vacuum tube operational amplifier was first used as ‘summing amplifier’ at AT&T Bell Labs at New Jersey, USA by the engineer Karl D Swartzel Jr. in 1941. It was used in artillery director along with Radar in world war-II.

- Operational amplifier with non-inverting input was introduced in 1947 at Colombia University by Prof R Ragazzani.

- Commercial op amp was developed during 1953 by George A Philbrick.

- With the invention of transistor in 1947 and Silicon transistor in 1954 at AT & T Bell Labs, USA, the concept of integrated circuit (IC) became a reality. The introduction of planar technology in 1959 made transistors and ICs for stable production. Discrete operational amplifiers were commercially available by 1961. We can see tallest transistor monument at AT & T campus in New Jersey, USA.

- Operational amplifier is a high gain amplifier with dual input and single output. It has differential input (difference in voltage between the two input voltages to op amp) signal mode of operation. Input signals are DC coupled to the operational amplifiers. They are mostly used with negative feedback (a portion of output voltage is applied to inverting input) for stable operation. Open-loop gain is infinite for ideal operational amplifiers. However, in real-time use of operational amplifiers, they are used with negative feedback having finite values of gain and stable operation.

- Initially op amps were used for mathematical operations to solve the integral and differential equations in mathematical modelling of electronic systems using analog computers. Later, they find many applications in both analog and digital electronics and communication circuits.

- Operational amplifiers using transistors (active devices) came into commercial use during the early years of 1960s. They are used in signal conditioning circuits, analog computers, industrial electronics, analog to digital converter circuits, and digital to analog converter circuits.

The fundamentals of operational amplifiers are explained step by step as in the following:

- Block diagram of operational amplifier.

- Inside blocks of an op amp.

- Differential amplifiers.

- Analysis of op amp with pin diagrams and packages.

- Characteristic features of amp with voltage gain, frequency response, bandwidth, etc.

2.2 INTRODUCTION TO OPERATIONAL AMPLIFIER

Operational amplifier: Operational amplifier is popularly known as op amp. From its initial application in analog computers to perform mathematical operations such as addition, subtraction, integration, and differentiation, it had the popular name ‘operational amplifier’.

- Operational amplifiers are used in many industrial, commercial, and consumer electronic gadgets. It is a high gain voltage amplifier. It has many applications such as differential amplifier, voltage comparator, instrumentation amplifier, isolation amplifier (voltage follower for impedance matching application among different stages of amplifiers), and Schmitt trigger applications in waveform generators.

- Op amp in open-loop configuration functions as a voltage comparator with very large values of gain. Voltage comparator circuits find many applications in Schmitt trigger, etc.

- Due to the addition of negative feedback to operational amplifier (closed-loop configuration), it has finite values of gain. Amplifier gain and frequency response can be controlled by using suitable feedback network.

- Operational amplifiers using positive feedback circuit function as oscillator circuits.

2.3 BLOCK DIAGRAM OF AN OPERATIONAL AMPLIFIER

An operational amplifier is a multistage amplifier consisting four internal blocks, as shown in Fig. 2.1. Basic building blocks inside an op amp IC are as follows:

- First-stage differential amplifier.

- Second-stage differential amplifier.

- Voltage-level shifter.

- Power output stage.

Fig. 2.1 Block Diagram of an Operational Amplifier (Op Amp) in a Linear Integrated Circuit (LIC)

Two-stage Differential Amplifier

- Forms the input stage of operational amplifier (op amp).

- Provides ‘large values of gain’ and ‘very high input impedance’.

- Op-amp gain is mostly provided by first stage itself, and the second stage is added for some additional gain. First stage has two input terminals. It has the facility to operate on two signals working in differential mode of operation.

- One input is known as ‘inverting (INV) input signal’.

- Second input is known as ‘non-inverting (NINV) input signal’.

- Contributes to higher values of common-mode rejection ratio (CMRR).

- Provides ‘zero output’ to common-mode signals.

- Noise rejection capability due to large ratio of CMRR.

- Input signals are ‘DC coupled’ to operational amplifier.

Differential amplifier works with signals having frequencies from zero hertz to very high frequencies, as there are no frequency sensitive circuit elements in the form of coupling capacitors or bypass capacitors.

2.4 BJT (Bipolar junction transistor) DIFFERENTIAL AMPLIFIER

Differential Amplifier

- Amplifies the difference between two voltages applied at its inputs and produces an output voltage.

- Rejects the common mode or average of the two input signal voltages.

BJT differential amplifier is one of the building blocks of operational amplifier ICs. Before, they were used mostly in analog computers to solve differential equations used for computations in electrical modelling of physical systems and electronic instrumentation.

The differential amplifier is also known as difference amplifier. The difference amplifier amplifies the difference of the two input signals connected to the op amp. The differential pair is also known as emitter-coupled pair. Operational amplifiers having differential amplifier circuits are popularly used in LIC such as μA 741.

Working Principles of Differential Amplifier

The basic circuit of a BJT differential amplifier is shown in Fig. 2.2. Two identical transistors T1 and T2 are connected in common-emitter transistor operation with symmetrical configuration. Differential amplifier has the provision to connect two input voltages Vin (1) and Vin (2) and obtain two output voltages Vout (1) and Vout (2).

Fig. 2.2 BJT Differential Amplifier

Differential amplifier is primarily used to amplify the differential signal that is the difference between the two input signal voltages and produces two output voltages Vout (1) and Vout (2). The difference between the two output voltages is taken as a single output voltage Vout from the amplifier, as shown in Fig. 2.2.

The circuit is designed for equal biasing voltages VBE1 and VBE2, so that the biasing voltage becomes VBE = 0.7 V for the two identical transistors. Emitter terminals of the two transistors are connected together. The resulting DC bias current IE through RE will be shared equally by the two transistors T1 and T2. Each transistor shares 0.5 IE to contribute to total emitter current IE through the emitter resistor RE (connecting the two emitters).

The two collector currents IC (1) and IC (2) are equal to 0.5 IC. Each transistor collector current IC = 0.5 IE. Total current IE is the sum of the two DC collector currents of each transistor. The two collector resistances RC1 and RC2 are set to equal value RC. Then, the two collector currents will be equal resulting in equal magnitudes of DC collector voltages VC (1) and VC (2). The output voltages Vout (1) and Vout (2) are developed at the two collector points, when the input signal voltages are applied.

The output can be taken from any one of the output terminals and ground. Then, the amplifier operation is single-ended output differential amplifier. The difference of the two output voltages Vout (1) and Vout (2) functions as a single output voltage Vout. Then, it is known as double-ended output arrangement.

For a perfectly symmetrical amplifier, the output voltage

Vout = AD [Vin (1) − Vin (2)],

where AD is the gain of the amplifier in differential mode operation of the two input voltages. AD is known as the differential mode gain.

- Noise or any unwanted signal is generally common to both the input terminals of the amplifier. The differential connection causes cancellation of the noise based on the magnitude of CMRR.

2.4.1 Main Features of the Differential Amplifier

- Differential voltage Vd: Very large gain occurs when opposite signals are applied to both the input terminals. Difference voltage between the two inputs:

Vd = [Vin (1) − Vin (2)](2.1)

- The difference signal Vd is amplified with gain AD. Amplified output voltage (for differential inputs)

Vout (D) = AD [Vin (1) − Vin (2)] (2.2)

- Very small gain occurs when common type signals are applied to the two input terminals (for common inputs)

(2.3)

(2.3)The overall operation is to amplify the differential signals, while rejecting the common signals at the two inputs. However, total output voltage Vout = Vout (D) + Vout(C). It is the sum of the two types of output voltages that occur due to the differential-mode input signals and common-mode input signals.

(2.4)

(2.4) - Common signals in the amplifier undergo attenuation (due to cancellation) of the noise (unwanted) input signals. This feature is known as common-mode rejection (CMR).

- Since the amplification of the opposite signals is much greater than that of the common-mode input signals, the amplifier provides a CMR. It is described by a parameter known as CMRR.

- CMRR

(2.5)

(2.5)

CMRR in decibels (dB) =

(2.6)

(2.6)The typical values of CMRR are between 100 dB and 120 dB. Usually, differential amplifiers with larger values of CMRR are used. It measures how well the differential amplifier attenuates or rejects the common-mode signals. The amplifier is virtually free from interfering signals. The signal to noise ratio will be improved by a factor of the value of CMRR.

- Interference signals, static, induced voltages, etc., drive a differential amplifier in the common-mode operation.

- A common-mode input signal is used to test a differential amplifier to check how well the sections are working. The internal circuitry of operational amplifiers use differential amplifiers in cascade. As no coupling or bypass capacitors are used in differential amplifiers, they are simple cascaded direct-coupled (DC) amplifiers capable of amplifying signals with frequencies as low as zero hertz. (DC is nothing but AC with zero frequency.)

- Transistors in IC circuits using differential amplifiers will be almost at same temperature. Therefore, there will be almost no drift in cascaded differential amplifiers.

2.4.2 JFET (Junction Field Effect Transistor) Differential Amplifier

Differential amplifier using JFET is similar to BJT differential amplifier. It is shown in Fig. 2.3 and also known as source-coupled pair. The simple process of fabrication of

Fig. 2.3 JFET Differential Amplifier

JFET in IC version and very high input resistance of FET devices make the application of FET differential amplifiers more popular.

For a double-ended amplifier operation when two input voltages Vin (1) and Vin (2) (which are out-of-phase to one another) are applied, the effective input signal will be [Vin(1) − Vin (2)]. Then, two output voltages Vout (1) and Vout (2) will be developed at the two drain terminals of the FET devices with voltage gain AD. The effective output voltage Vout = [Vout (1) − Vout (2)].

Voltage Gain of Double-ended Differential Amplifier

Voltage gain  (2.7)

(2.7)

This is equal to the gain of common source FET amplifier (using single FET).

The voltage gain of single-ended amplifier AS with single input signal (single stage).

Voltage gain ![]() (2.8)

(2.8)

DC drain currents ![]() (2.9)

(2.9)

through each FET device, where ID (1) is the drain current through FET device T1 and ID is the drain current through FET device T1.

When the two FET devices are matched pair (identical transistors) ![]()

DC Drain voltages are as follows:

Drain voltage at FET (1) is ![]() (2.10)

(2.10)

Drain voltage at FET (2) is ![]() (2.11)

(2.11)

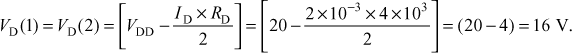

Example 2.1

In the JFET differential amplifier circuit of Fig. 2.3, ID (SS) = 4 mA and pinch-off voltage VP = − 4 V. Calculate the following:

- DC output voltage.

- Transconductance.

- Gain of single-ended amplifier.

- Gain of double-ended amplifier.

Solution: Current through

- DC voltages at drain terminals of FET devices

millimhos

millimhos- Voltage gain of single-ended amplifier

= 2.828

= 2.828 - Gain of double-ended amplifier

The differential amplifier circuit in Fig. 2.2 can be operated in any of the following three types of input signal voltage combinations.

2.4.3 Single-ended Differential Amplifier

When one input signal Vin is applied to one of the input terminals of the two transistors, while the second input terminal of the other transistor is grounded, the electronic amplifier is known as single-ended amplifier, which is shown in Fig. 2.4.

Fig. 2.4 Single-ended BJT Differential Amplifier

In this amplifier configuration, a single input signal is applied. However, due to common emitter connection of the two transistors, the input signal operates the two transistors into conduction. This results in two output voltages Vout (1) and Vout (2). The output voltage can be taken from any of the output terminals and ground. Then, it is considered as single-ended output differential amplifier.

Signal waveforms at different points in the amplifier circuit are shown in Fig. 2.4.

Transistor T1 acts as common-emitter transistor amplifier. Therefore, amplified output voltage Vout (1) of transistor T1 is 180° out-of-phase with input signal voltage. Transistor T2 functions as common base transistor amplifier. Amplified output voltage Vout (2) will be in-phase with input signal Vin.

- When only one output terminal is available at the collector terminal of transistor T1, output voltage Vout will be 180° out-of-phase to the input signal applied to Base-1 of transistor T1.

- When only one output terminal is available at the collector terminal of transistor T2, output voltage Vout will be in-phase to the input signal applied to Base-1 of transistor T1.

2.4.4 Double-ended Differential Amplifier

When two equal input signals Vin (1) and Vin (2) of opposite polarity are applied to the two inputs of differential amplifier, and two outputs are available, the electronic amplifier is known as double-ended differential amplifier. Typical amplifier configuration is shown in Fig. 2.5. The differential mode signals are amplified. The difference between the two equal and opposite polarity input signals is double the magnitude of each signal. Therefore, the amplifier provides large gain. The output voltage is taken between the two output terminals and it is known as double-ended output differential amplifier.

Fig. 2.5 Double-ended BJT Differential Amplifier

2.4.5 Common-mode Operation of Differential Amplifier

Common-mode differential amplifier circuit is shown in Fig. 2.6. When the same input signal is applied to both the input terminals of the two transistors of the differential amplifier, the electronic amplifier is considered to be in common-mode operation of the amplifier. Therefore, the input signals to the two transistors are in-phase and equal in magnitude. The common-mode input signals get cancelled or not amplified by the differential amplifier because it is designed to amplify only the differential signals.

Fig. 2.6 Common-mode Operation of Differential Amplifier

An amplifier consists of DC bias conditions and input signals for amplification. Various levels of DC bias voltages in the differential amplifier are fixed according to the following equations using the amplifier circuit in Fig. 2.7. The combination of emitter resistor and the supply voltage −VEE fix up the DC emitter current, as shown in the following design section.

Fig. 2.7 DC Bias Voltages in BJT Differential Amplifier

Design Equations to Calculate DC Voltages and Currents for Differential Amplifier

VCC is the collector supply voltage. The magnitude of collector supply voltage depends upon the required swing of the output voltage. If maximum output voltage required is 10 V, then the supply voltage VCC = 10 V. Similar design criteria holds good for MOSFET differential amplifier design considerations.

In this assumption, emitter supply voltage = −VEE = − VCC = 10 V.

From the voltage and current distributions shown in the amplifier circuit, using Kirchhoff’s law, VCC = VRC + VCE + VBE − VEE.

VRC is the voltage drop across the resistor RC due to the flow of collector current IC.

VCE = voltage across the collector and emitter of the transistor.

VBE = 0.7 V for the silicon transistor to conduct.

− VEE = emitter supply voltage = collector supply voltage = VCC.

Collector voltage VC = VCC − IC RC.

VB = base voltage = external input signal voltages (AC or DC) = 0 V.

VE = emitter voltage.

VBE = bias voltage between the base and the emitter for the transistor to conduct.

VBE = 0.7 V for silicon transistors.

When external input signal voltages (AC or DC) are not applied to the differential amplifier and the collector supply voltage VCC is applied to the amplifier various DC voltages and currents in the circuit can be calculated using the following equations.

Equations for DC Voltages and Currents of Single-ended Differential Amplifier

Between each base and common emitter terminal of the amplifier in Fig. 2.7,

[VB − VE] = VBE (2.12)

Data: external signal voltage VB = 0 V and VBE = 0.7 V(2.13)

Substituting the data in equation (2.12), (0 − VE) = 0.7 V (2.14)

Therefore, VE = 0.7 V(2.15)

DC bias emitter current

Therefore,  (2.16)

(2.16)

When matched pair transistors T1 and T2 are used in the differential amplifier circuit, the two collector currents are equal.

Therefore, IC (1) = IC (2) = IC(2.17)

From the transistor configuration, when the two emitter terminals are connected together, the collector currents of each transistor

![]() (2.18)

(2.18)

If collector voltages VC (1) and VC (2) of the two transistors are equal, then

VC (1) = VC (2) = VC = output voltage = Vout.

Vout = collector voltage VC = [VCC − IC RC](2.19)

Example 2.2

Calculate DC bias voltages and currents in differential amplifier circuit (see Fig. 2.8).

Fig. 2.8 DC Bias Voltages in BJT Differential Amplifier

Solution:

Emitter voltage VE = VBE = 0.7 V.

Current through resistor ![]() 2.766 mA.

2.766 mA.

Collector current ![]() = 1.383 mA.

= 1.383 mA.

Collector voltage VC = [VCC − IC × RC] = [9 − 1. 383 × 10−3 × 3.3 × 103] = (9 − 4.56) = 4.44 V.

2.4.6 AC Signal Voltage Gain of Single-ended Differential Amplifier

For single-ended amplifier operation of a difference amplifier, one input signal Vin (1) is applied to transistor T1. The input terminal of transistor T2 is connected to ground terminal so that Vin (2) = 0 (see Fig. 2.9).

Fig. 2.9 Single-ended Differential Amplifier AC Signal Analysis

The two transistors are selected with identical characteristics for symmetrical operation of the difference amplifier. Therefore, the characteristics are as follows:

- The current gain factors are equal, that is, β1 = β2 = β.

- The input resistances of the two transistors are equal rin1= rin2.

- The input AC base currents of the two transistors for the applied input signal voltage Vin (1) are also equal. That is, ib1 = ib2 = ib.

- Collector currents iC1 = iC2 = iC.

Voltage Gain Equation for Single-ended Differential Amplifier

It can be derived from the AC equivalent circuit of the amplifier and the following equations are obtained (see Fig. 2.9):

AC input base current ![]() (2.20)

(2.20)

Collector current ![]() (2.21)

(2.21)

Output voltage ![]() (2.22)

(2.22)

Using the transistor input resistance rin = β re (2.23)

![]() (2.24)

(2.24)

where the emitter diode resistance ![]() (2.25)

(2.25)

where VT = voltage equivalent of temperature and VT = 26 mV at 27°C.

Further, IC (Q) = quiescent component of collector current.

Voltage gain ![]() (2.26)

(2.26)

Example 2.3

Calculate the DC currents, output voltage, and voltage gain for the single-ended differential amplifier with an input voltage 5 mV (see Fig. 2.10).

Fig. 2.10 Single-ended Differential Amplifier for Gain Calculations Using AC Signal Analysis

Solution:

Emitter current

Collector current ![]()

Collector voltage VC = [VCC − IC RC] = [9 − 50 × 10−6 × 90 × 103] = (9 − 4.5) = 4.5 V.

Emitter diode resistance ![]()

AC voltage gain ![]()

Data given are as follows: input voltage Vin = 5 mV.

Output voltage ![]() = 0.4325 V.

= 0.4325 V.

2.5 DIFFERENT METHODS TO IMPROVE CMRR OF DIFFERENTIAL AMPLIFIER

There are mainly three methods of improving the CMRR of differential amplifier. It can be understood from the following equation for CMRR.

Definition of Common-mode Rejection Ratio

Aid = magnitude of differential mode amplifier gain

![]() (2.27)

(2.27)

ACm = common-mode differential amplifier gain

![]() (2.28)

(2.28)

CMRR = ![]() (2.29)

(2.29)

Using the three equations (2.27), (2.28), (2.29), we get the following form:

CMRR = ![]() (2.30)

(2.30)

Equation (2.30) is the CMRR for dual input, balanced output differential amplifier.

From equation (2.30), CMRR can be improved by increasing the value of emitter resistor RE. Increase in RE demands higher biasing voltages and larger chip area on IC for fabrication. Such requirements cannot be satisfied in real time design and manufacturing processes.

- Therefore, different methods such as (a) constant current bias method and (b) adding current mirror circuit in differential amplifiers are used for improving CMRR.

- To improve CMRR, differential mode gain Aid has to be increased (from the definition of CMRR) and Aid is increased by including (adding) active load to differential amplifier circuit.

2.5.1 BJT and MOSFET Current Sources

Normal amplifier operation with input and output signal waveforms on transistor output characteristics is shown in Fig. 2.11. Similar signal operations can be studied on the output characteristics of FET, MOSFET, and vacuum tube amplifiers.

Transistor works as ‘current source’ when the quiescent (DC) operating point of transistor operation is fixed on the constant-current portion of the active region of transistor output characteristics. The concept of DC load line, Q-point, constant collector current region between points ‘A’ and ‘B’ for current source operation of transistor are shown in Fig. 2.11.

Fig. 2.11 Transistor Operation as Current Source If ‘Q-point’ is Fixed in Constant Current Region of Transistor Output Characteristics

Further, similar concepts can be explained for MOSFET device to function as ‘current source’ with the help of MOSFET output characteristics. BJT or MOSFET function as current sources with large values of output resistance. As discussed in the previous sections, the requirement of high values of common-mode differential amplifier gains ACm can be achieved by using active load. The increase in ACm improves the CMRR of differential amplifiers. It is a primer advantage, when such differential amplifiers form the input stage in ‘operational amplifier IC’. It provides large CMRR to eliminate the common-mode signal noises, which enter their input stages along with transducer outputs.

Concept of BJT as current source is shown in Fig. 2.12. When the biasing voltages are used to fix the quiescent point ‘Q’ on the constant current region (active region) of transistor output characteristics, transistor works as a current source having high output resistance.

Fig. 2.12 Transistor Current Source Concept from Transistor Output Characteristics

MOSFET current source concept is explained using MOSFET output (drain) characteristics showing the location of quiescent operating point ‘Q’. If Q-point is located in constant (drain) current ID region between points A and B, active device MOSFET functions as active load with current source in parallel with the large value of device resistance RD.

Controlling (independent) parameter, the drain to source voltage VDS and controlled parameter, the drain current ID are shown in the output characteristics of MOSFET device in Fig. 2.13. MOSFET device symbol and its function as current source are shown in the figure.

Ideal output resistance ro (RD) of current source is infinite. Therefore, higher value of load resistance is achieved to improve CMRR of differential amplifiers with MOSFET as active load.

Fig. 2.13 MOSFET Current Source Concept from MOSFET Output or Drain Characteristics

Signal operations on output characteristic of transistor and MOSFET as active loads.

Output Characteristics of Active Transistor Load with Signal Waveforms

The location of ‘Q’-point on the transistor output characteristics is shown in Fig. 2.14. Q-point is located in constant current portion of output characteristic between VCE and IC for constant value of base current IB. Signal waveforms are also shown in the figure.

Fig. 2.14 Output Characteristics of Active Load Transistor with Signal Waveforms

Output Characteristics of Active MOSFET Load with Signal Wave Forms

MOSFET output characteristic is shown in Fig. 2.15. Q-point location on constant current region between the two points A and B causes MOSFET to behave as a constant current source. As a current source, the active device MOSFET is used as the load for differential amplifier. It has very large output resistance. It increases the common-mode gain of the amplifier so that differential amplifier works with increased values of CMRR.

Fig. 2.15 Output Characteristics of Active Load MOSFET with Signal Waveforms

2.5.2 Differential Amplifier with Constant Current Bias Using Transistor

Because of the two limitations for increase in value of RE (to improve CMRR), resistor RE is replaced by a transistor acting as a current source. Bipolar junction transistor is a current-controlled constant current (CCCS), which is evident from the transistor output characteristics. High (infinite) value for source resistance RS for current source (used for RS) improves CMRR. There will be considerable increase in CMRR by using constant current source (transistor circuit as shown in Fig. 2.16), without increasing biasing voltages or physical increase in the value of RE. The differential amplifier circuit with RE replaced by transistor constant current source circuit is shown in Fig. 2.16.

Fig. 2.16 BJT Differential Amplifier Circuit with Constant Current Source Using Transistor Circuit to Improve CMRR

2.5.3 Differential Amplifier with Constant Current

Source Biasing Using Zener Diode

Differential amplifier circuit with constant current biasing using zener diode is shown in Fig. 2.17. It keeps constant current and stable operating point to the differential amplifier. It improves CMRR of the amplifier.

Fig. 2.17 BJT Differential Amplifier Circuit with Constant Current Biasing Using Zener Diode to Improve CMRR

2.5.4 Current Mirror Circuit

Current mirror circuit uses transistor (BJT or FET or MOSFET) devices in ICs. It basically consists of two transistors as shown in Fig. 2.18. It is used to mirror the current in one active device into another (second) device in the load circuit. Some current mirror circuits use more than two active devices in the total circuit for improved performances. Such circuits are referred as current repeaters. Mirrored base current is used to cater to more number of loads. Simple structural details of transistor current mirror are shown in Fig. 2.18. The current mirror behaves as a current regulator, which provides nearly constant current (I) to broad range of load (RL) resistances.

Fig. 2.18 BJT Current Mirror Circuit

The principle of operation of ‘current mirror’ are as follows:

- Constant current Iin is fed into the collector terminal of left-hand side transistor T1. Transistor T1 is connected as a diode. Therefore, transistor conduction establishes forward bias voltage VBE for transistor T1. By virtue of the circuit structure, same voltage VBE appears between base and emitter terminals of transistor T2.

- Two transistors T1 and T2 will be identical because of their IC fabrication. Therefore, the emitter currents of the two transistors will be same (identical).

- If base currents IB (1) and IB (2) of the two transistors are negligibly small, output current Iout will be same and mirror replica for input current Iin. Thus, the current mirror circuit mirrors (or copies) the current flowing in one active device (for example, Iin) into another transistor T2 maintaining output current Iout constant regardless of different variations in load resistances in the circuits.

- ‘Current mirror’ can be classified as ‘current-controlled current source’, (CCCS), which is already familiar with as one type (class) of amplifier circuit.

- However, in practice, base terminals draw finite magnitudes of input base currents IB (1) and IB (2) due to the forward bias supplied to the ‘two input junctions’ of the transistor devices. Under such scenario, the two base currents are added and subtracted from the input current, so that the output current will be less. Finally, the output current will be less than the input driving current to a tune of the sum of the two base currents (IB (1) + IB (2)).

- Current gain A =

in the presence of finite magnitudes of base currents.

in the presence of finite magnitudes of base currents.

Current Mirror Circuit Analysis

The two transistors are identical in IC technology base currents IB (1) and IB (2) = IB and collector currents IC (1) and IC (2) = IC. Forward bias is same for the two transistors by virtue of ‘structure of current mirror’.

Current gains β1 = β2 = β, where β1 and β2 are current gains of transistors T1 and T2

![]()

Therefore, ![]()

Collector current ![]()

Since, current gain β >> 1 and Iin = IC

![]() , because VBE << VCC

, because VBE << VCC

Hence, input current Iin for the first transistor is constant current and the collector current is constant. Two collector currents IC (1) and IC (2) are mirror replicas to one another as evident from the structure and IC fabrication with common and identical features of devices.

2.5.5 BJT Differential Amplifier with Active Load Using Transistors

Differential amplifier with active load circuit is shown in Fig. 2.19. Differential amplifier uses two transistors T1 and T2. The two transistors T3 and T4 operated in active region of transistor characteristics are used as active loads for the differential amplifier. Transistor characteristics in active region are constant current characteristics. Therefore, transistors T3 and T4 operated in constant current regions having its characteristics function as constant current sources. They have very large resistance, once they are constant current sources. They act as active loads with very large resistances. Transistor current sources are used in place of usual resistors. (It eliminates the drawbacks for the use of large value conventional resistors.) Therefore, common-mode gain of the differential amplifier is high. The large values for common-mode gain ACm result in large values of CMRRs of the order of 150 dB.

Fig. 2.19 Differential Amplifier with Active Load Using Transistors

- Two collectors C2 and C4 are connected together. Single-ended output voltage Vout is taken between the common point of two collectors C2 and C4 and ground for the amplifier.

- Two voltages + VCC and −VEE are obtained from dual power supply.

- All the transistors are selected to have same values for current gains β. Therefore, currents in all the transistors will be identical. It results in identical or same values for collector currents. Thus,

- All the DC currents are balanced in the total circuit.

2.5.6 BJT Differential Amplifier with Active Load Using Three Transistors (see Fig. 2.20)

Fig. 2.20 BJT Differential Amplifier with Active Load Using Three Transistors

2.5.7 MOSFET Differential Amplifier with Active Load Using MOSFET (see Fig. 2.21)

Fig. 2.21 MOSFET Differential Amplifier with Active Load Using MOSEFTs

2.6 BASIC BUILDING BLOCKS OF AN OPERATIONAL AMPLIFIER

Basic building blocks of an operational amplifier are shown in Fig. 2.22 and it is explained in the following:

Fig. 2.22 Internal Blocks of Operational Amplifier IC: Two-stage Differential Amplifier Voltage-level Shifter and Darlington Pair

- The first stage differential amplifier has two input terminals B1 (base terminal of first transistor T1) and B2 (base terminal of second transistor T2) and two output (collector) terminals C1 and C2 of the two transistors. It is a dual input, balanced output differential amplifier.

- Input voltage Vin (1) applied at base terminal B1 undergoes 360° phase shift by the time it reaches the output port. Output voltage will be in-phase with the input terminal. Such base terminal (B1) is considered as non-inverting (NINV) input terminal.

- Inverting (dual) input voltage Vin (2) applied at base terminal (2) undergoes 180° phase shift by the time it reaches the output port. Hence, the output voltage will be 180° out-of-phase for inverting input signals. Therefore, the second base input terminal (B2) is considered as inverting (INV) input terminal.

- The two outputs of the first differential amplifier are connected to second stage. It has a single output. Its output is connected to voltage-level shifter (emitter follower).

Last stage is Darlington pair amplifier or complementary symmetry push–pull amplifier. These internal blocks are shown for understanding the basic configuration inside the operational amplifier.

To obtain CMRR with Vout = 0, when Vin (eff) = 0, it is necessary to use matched (pair) transistors and resistors with identical characteristics. Thus, the first amplifier stage is a ‘dual input, balanced output differential amplifier’. The first stage provides most of the gain of operational amplifier.

Voltage-level Shifter (Intermediate Stage Between the Input and the Output Stages)

The first two stages of differential amplifiers are DC amplifiers. Therefore, the DC voltage level at the output collector terminal of the second stage will be high. This DC voltage gets propagated to output port along with the AC voltage in normal amplifier chain. It is undesirable. Using DC voltage-level shifter circuit, necessary correction is made to feed it to the input stage of push–pull amplifier (last stage) or Darlington pair amplifier for normal amplifier operation with pure AC voltage at the output port.

Output Stage of Operational Amplifier

- It is push–pull complementary symmetry amplifier/Darlington pair amplifier.

- It has low output impedance Zout.

- It has large output swing and current carrying capability.

2.7 ANALYSIS OF IDEAL OPERATIONAL AMPLIFIER

Operational amplifier is an IC. The schematic circuit symbol of op amp is shown in Fig. 2.23. Op amp (μA 741) is mostly used in the industrial applications and the laboratories in the colleges. Therefore, its detailed representation is shown in Fig. 2.23.

Fig. 2.23 Schematic Symbol of Operational Amplifier

- The following concepts are clear from the internal blocks of op amp shown in Fig. 2.22.

- Op amp IC has two input terminals, one output terminal, and two supply voltage connection terminals for making circuit connections for applications. There will be some other pins depending upon the IC package.

- Non-inverting input terminal (pin-3). Voltage at this terminal can be named as V1.

- Inverting input terminal (pin-2). Voltage at this terminal can be named as V2.

- Output terminal (pin-6). Output voltage at this terminal can be named as Vout.

- (d) Positive supply voltage terminal (pin-7). Voltage = + VCC.

- (e) Negative supply voltage terminal (pin-4). Voltage = − VCC.

- The magnitude of supply voltages and the pin number details of IC are provided in the manufacturer’s data manuals of selected op amp. The selection of IC in any circuit used in commercial, military, and industrial applications will be decided by the circuit parameters and the circuit application specifications.

2.8 PIN CONFIGURATION OF OPERATIONAL AMPLIFIERS μA 741 IC

Dual-in-line plastic package and metal can package are shown in Fig. 2.24. Operational amplifiers use DC amplifiers and output power stage as seen in the previous sections (see Fig. 2.22). The DC amplifiers have very large gain operating with two input signal voltages V1 and V2 producing one output voltage Vout. Supply voltages are ± 5 V and ± 15 V.

Fig. 2.24 Op Amp 741 IC Pin Configuration 741 Op Amp Metal Can Package External Connections at Pins with Numbers

Pin-1: Offset null terminal.

Pin-2: Inverting (INV) input terminal. All input signals connected to this terminal on op amp will appear at the output terminal with 180° phase shift.

Pin-3: Non-inverting (N-INV) input terminal. All input signals applied to this terminal on op amp appears as it is in waveform (shape) at the output terminal. Changes occur only in levels of amplitudes at the output voltage.

Pin-4: Supply voltage − VCC (negative supply voltage terminal).

Pin-5: Offset null terminal.

Pin-6: Output terminal; output signal.

- Output signal will have 180° phase shift to input signals applied to inverting input terminal pin-2.

- Output signal will be in-phase to input signals applied to non-inverting input terminal pin-3.

- Output signal depends upon the voltage gain of operational amplifier.

Pin-7: supply voltage +VCC terminal (positive supply voltage terminal).

Pin-8: no connection.

Resistors, capacitors, and power supply terminals are connected externally to different pins of op amp so that operational amplifier can be used in different applications such as amplifier, oscillator, integrator, differentiator, and comparator.

- Operational amplifiers (μA 741) are manufactured by many electronic product companies. Its operational features are mostly suited to many scientific, commercial, and industrial applications. Therefore, the study and applications in electronic system design and manufacturing (ESDM) goes round operational amplifier μA 741.

- Different types of op amps: (a) μA 741 simple and popular type operational amplifier, (b) LT 1056 op amp gas JFET device at its input stage, (c) low power CMOS op amp IC is LMC 660, (d) medium power op amp IC is LM 675, (e) high power operational amplifier IC is LM 12, and (f) LT1220 and LT 1221 are high frequency op amps.

2.9 SCHEMATIC DIAGRAM OF OPERATIONAL AMPLIFIER

The schematic diagram of operational amplifier is shown in Fig. 2.25.

Fig. 2.25 Schematic Symbol of Operational Amplifier Showing Input and Output Voltages for Op Amp IC 741

- Outside connection from pin-3 is non-inverting (N-NIV) input terminal. V1 is the input voltage at pin-3.

- +sign at N-NIV terminal indicates that input voltage applied at pin-3 appears at output terminal (6) with zero phase shift.

- Terminal pin-2 is the inverting (INV) input terminal. V2 is the input voltage at pin-2. − Sign at INV terminal indicates that the input voltage applied at pin-2 appears at the output terminal (6) with 180° phase shift.

- Terminal 6 is output terminal (Vout is the output voltage at pin-6).

- [Vout = A (V1 − V2) = AVd], where A = open-loop gain of operational amplifier and Vd = net differential voltage at input port of op amp, differential input voltage should be such that the output voltage due to applied Vd should be less than the supply voltage.

- Terminal pin-7 is positive terminal of supply voltage + VCC to be connected here.

- Terminal 4 is negative terminal of supply voltage − VCC to be connected here.

- Common terminal for all input, output, and supply voltage connections.

- Power supply voltage = ± V (rated voltage) (dual power supply).

Differential input voltage: Input voltages V1 and V2 are known as single-ended voltages. All voltages in the operational amplifier are referred with respect to common terminal AC ground. Differential mode voltage VD is the difference between the two input voltages V1 and V2 Therefore, differential input voltage VD = (V1 − V2).

Output voltage: Vout = [A (V1 − V2)] = (AVd), where A = amplifier gain.

Common-mode voltage: Common-mode input voltage VC is the average value of two input voltages V1 and V2. Therefore, ![]() .

.

A very small gain occurs when common type signals are applied to the two input voltages (for common inputs).

![]()

Total (overall) voltage of the operational amplifier due to the presence of differential mode and common-mode input voltages.

2.10 CHARACTERISTIC FEATURES OF AN IDEAL OPERATIONAL AMPLIFIER

- 1. Infinite open-loop gain: If there is no feedback connection between the output and the input terminals of operational amplifier, it is considered to be in open-loop condition, as shown in Fig. 2.5. Therefore, the operational amplifier will have infinite open-loop gain.

- Operational amplifier with negative feedback configuration: Operational amplifier with negative feedback arrangement using two resistors RF and R1 is shown in Fig. 2.26.

Output voltage Vout is fed back to inverting input terminal through resistor RF. Two resistors R1 and RF decide the voltage gain of the amplifier according to the equation for closed-loop voltage gain

.

.Hence, voltage gain for operational amplifier with negative feedback is a finite value.

- 3. Very high input resistance: Resistance between the non-inverting and inverting input terminals of op amp is infinite for ideal operational amplifier. This feature is due to differential amplifiers at the input port of operational amplifier. However, in practical applications, the input resistance of op amp is of the order of 2 mΩ.

From Fig. 2.27, the input resistance of op amp

Output voltage Vout = -IF × RF.

Output voltage

Therefore, voltage gain

The voltage gain of operational amplifier with external resistors connected to provide negative feedback (closed-loop op amp configuration) is shown in Figs. 2.26 and 2.27. Voltage gain becomes finite. Output signal amplitudes also become finite with limitation to supply voltages to operational amplifier IC.

Fig. 2.26 Operational Amplifier with Negative Feedback

Fig. 2.27 Operational Amplifier with Negative Feedback

Example 2.4

For the operational amplifier circuit shown in Fig. 2.27, calculate input current, output voltage, and voltage gain for the given data in the circuit.

Solution: Input current ![]()

Total current passing through resistor R1 will flow through feedback resistor RF, because the current (I) through input port of op amp is zero. Inverting input terminal is at virtual ground. Therefore, the current drawn by op amp I = 0 mA.

Hence, I1 = IF = 1 mA.

Output voltage Vout = − IF × RF = 1 × 10−3 × 220 × 103 = 220 V

Output voltage ![]()

Therefore, voltage gain ![]()

- Very low output resistance: Output resistance Rout across the two output terminals is about 50 Ω. Output stage is a complementary symmetry power amplifier or Darlington pair. They have very low output resistance.

- Output voltage: It is independent of the current drawn by load resistance RL. Maximum swing in output voltage is limited to about 90% of the supply voltage VCC.

- 6. Zero input current drawn by op amp: Because of very high input resistance (Rin), input current is almost zero between the two input terminals. Virtual short circuit exits between the two input terminals.

- Voltage-controlled voltage source (VCVS): The input voltages control the nature of output voltages. Hence, operational amplifier is a VCVS.

- Bandwidth: Bandwidth is infinite under ideal conditions for op amp. However, in practice, Op Amp has finite bandwidth, when used with negative feedback for AC amplifier applications. Op amp configured as voltage follower has the large bandwidth.

- Gain bandwidth product: The gain of op amp decreases with increasing operational signal frequency. Gain bandwidth product is defined as bandwidth of op amp when the amplifier gain is unity. It is also known as unity gain bandwidth (UGB) and it is of the order of 1 mHz.

- Speed (Propagation delay).

- Supply voltage rejection ratio (SVRR): input offset voltage Vin (offset) undergoes changes due to variations in supply voltages to op amp. It is known as ‘supply voltage rejection ratio’ (SVRR).

- The unit for SVRR is given in microvolts per volt or in decibels.

- Some manufacturers call SVRR as ‘power supply rejection ratio’ (PSRR).

- Some manufacturers call SVRR as ‘power supply rejection’.

- Infinite common-mode rejection ratio (CMRR): Because of large values of CMRR, unwanted common-mode signals from noise inputs will contribute zero differential input voltage.

- When the input voltage is zero, output voltage of amplifier is zero.

- Output voltage response is instantaneous to input voltages.

- Differential input voltage Vd = (V1 − V2).

- Output voltage Vout = AVd = A (V1 − V2), where A = open-loop gain.

2.11 COMMON-MODE REJECTION RATIO (CMRR)

Undesired signal pickups from strong magnetic fields into a circuit form noise signals at the two input terminals of inside differential amplifier of op amp. The two noise signals Vn (1) and Vn (2) will be of equal magnitude. They will be cancelled or rejected to the maximum extent possible by differential amplifier. Therefore, the output voltage (Vout) will be free of noise signal pickups. The extent of noise signal rejection by the op amp is considered as CMRR of op amp.

Op amp output voltage depends upon the following two modes of voltages (see Fig. 2.28).

Fig. 2.28 Open-loop Differential Voltage Amplifier

Differential signal Vd of the two input voltages V1 and V2, where Vd = (V1 − V2).

Common-mode signal ![]() (average of the two input signal voltages).

(average of the two input signal voltages).

Fig. 2.28 shows op amp with two input signals V1 and V2, and output voltage Vout with voltage gain A. It is an open-loop differential voltage amplifier.

Output voltage VA = A (V1 − V2).

Output voltage Vout can also be expressed as in the following:

Vout = [A1V1 + A2V2], where (a) A1 is the voltage gain with voltage V1 and voltage V2 = 0 (which means grounded V2), as shown in Fig. 2.29 and (b) A2 is the voltage gain with voltage V2 and voltage V1 = 0 (which means grounded V1), as shown in Fig. 2.30.

Fig. 2.29 Operational Amplifier with Input Voltage V1 and V2 = 0 and Output Voltage Vout (1) and Gain A1

Fig. 2.30 Operational Amplifier with Input Voltages V2 and V1 = 0 Output Voltage Vout (2) and Gain A2

Open-loop non-inverting amplifier using operational amplifier is shown in Fig. 2.29. Input voltage V1 is applied to non-inverting input terminal of operational amplifier.

If inverting input terminal is connected to common terminal (ground), then V2 = 0 V.

- Output voltage Vout (1) = A1 × V1.

- It can be generally expressed as input voltage V1 = Vin and gain A1 = A.

- General representation is that output voltage Vout = A × Vin.

The expression for gain shows that the output and input voltages are in-phase and the output voltage is larger than the input voltage due to amplifier operation.

Open-loop non-inverting amplifier using operational amplifier is shown in Fig. 2.30.

- Input voltage V2 is applied to the inverting input terminal of operational amplifier.

- The non-inverting input terminal is connected to common terminal, ground. It means that V1 = 0 V.

- Output voltage Vout (2) = − A2 × V2.

- It can be generally expressed as input signal V2 = Vin and gain A2 = A.

- General representation is that output voltage Vout = −A × Vin. The negative sign for the output voltage means that the output voltage is 180° out-of-phase to input signal voltage. It shows that output is an inverted voltage to input voltage. The output voltage is larger than the input voltage.

From the previous equations, expressions for differential gain Ad and common-mode gain ACm can be derived as shown in the following:

Differential gain ![]()

Common-mode gain ACm = [A1 + A2]

Definition of CMRR

CMRR = ![]()

CMRR in dB = 20 log10 ![]()

Output voltage

- Common-mode voltage gain ACm will be in general a small value, whereas CMRR will be very large. Such behaviour can be seen from the following worked-out example.

- Identical behaviour can be observed between the two input terminals of an op amp, if the values for CMRR are very high. It automatically follows in reduced values for common-mode voltage gains.

Example 2.5

Operational amplifier has differential gain of 80 dB and CMRR of 100 dB. If V1 = 2 μV and V2 = 1.6 μV, then calculate output voltages for differential and common-mode input signal operations.

Solution: Differential gain in dB = 20 log10Ad = 80 dB.

Therefore, ![]()

CMRR in dB = 20 log10CMRR =100 dB.

Therefore, antilog ![]() . Hence, CMRR = 105

. Hence, CMRR = 105

Input voltage V1 = 2 μV and input voltage V2 = 1.6 μV.

Differential voltage Vd = (V1 − V2) = (2 − 1.6) × 10−6 V = 0.4 × 10−6 V

Common-mode voltage ![]() V.

V.

Output voltage

The performance of an operational amplifier depends upon the following important parameters.

2.12 INPUT BIAS AND OFFSET CURRENT

First (input) stage of op amp has very high input impedance, Zin. Therefore, the operational amplifier has very high input impedance. Under such condition, no current flows into the input port of op amp.

- The input stage of op amp consists of two transistors in differential amplifier stage. The two transistors need finite magnitudes of bias currents for the transistor operation.

- IB (1) is the base current of the first transistor in input differential stage amplifier.

- IB (2) is the base current of the second transistor in input differential stage amplifier.

- Thus, the input-side transistors have two input bias currents.

- Resulting output voltage and input bias currents are shown in Fig. 2.31.

- The two input currents are due to unequal biasing voltages to the two transistors of differential amplifier inside the operational amplifier IC.

- There are a number of unbalances in input resistors and transistors. They contribute to input bias offset voltage.

Fig. 2.31 Input Bias Current Ibias in Operational Amplifiers

Definition of Input Bias Current (Ibias)

Input bias current Ibias (Fig. 2.31) is the average of the two input currents IB (1) and IB (2) ![]() , when Vout = 0 V.

, when Vout = 0 V.

Bias currents will be of the order of a few hundred nano-amperes for BJT devices and few hundred pico-amperes when FET and MOSFET devices are used in op amps.

Contribution of Input Bias Current that Produce Output Offset Voltage

Output offset voltage contribution due to input bias current Ibias (Fig. 2.32) is given as follows:

Vout = (offset) = Ibias × R2 mV.

Fig. 2.32 Output Offset Voltage Contribution by Input Bias Current Ibias

Input Offset Voltage

Input offset voltage is due to the differences in forward biasing voltages VEE for the input transistors in the op amp. When no input signals are applied externally to the two input terminals, voltages V1 = 0 and V2 = 0.

The two input terminals are connected to ground terminal as shown in Fig. 2.33. The input currents are Iin (1) and Iin (2). Then, the voltage that appears between the two input terminals is known as ‘input offset voltage’ Vin (offset). It is abbreviated as Vin (0).

Fig. 2.33 Output Offset Voltage Contribution by Input Offset Voltage Vin (0)

Therefore, the amplifier amplifies this input offset voltage and considerable Ibias.

The magnitude of output voltage appears as the output offset voltage. Thus, the input offset voltage also contributes to output offset voltage.

Voltage gain  .

.

Output offset voltage Vout (0) = AV × Vin (0) V.

Example 2.6

Consider an operational amplifier with resistors R1 = 1 kΩ and Rf = 99 kΩ. When the two input terminals are grounded so that voltage V1 = 0 and V2 = 0. Calculate the output offset voltage Vout (0), if there is an input offset voltage Vin (0) = 2 mV.

Solution:

Voltage gain

Output offset voltage Vout (0) = AV × Vin (0) V = 100 × 2 mV = 200 mV = 0.2 V.

2.13 OUTPUT OFFSET VOLTAGE

Output offset voltage in non-inverting amplifier due to input offset voltage is shown in Fig. 2.34.

Fig. 2.34 Output Voltage Vout for Non-inverting Op Amp for an Input Voltage Vin

Whenever an input voltage Vin is applied to non-inverting operational amplifier, output voltage Vout can be calculated by the equation

If R1 = 1 kΩ and R2 = 9 kΩ, then

.

.

If input voltage Vin = 0.5 V, output voltage Vout = AV × Vin = 10 × 0.5 = 5 V.

Whenever there is a finite magnitude of input offset voltage Vin (0) across the two input terminals of the op amp, its presence can be considered in calculating the output offset voltage, as shown in Fig. 2.35 along with relevant equations.

Fig. 2.35 Output Voltage Vout for a Non-inverting Op Amp for an Input Voltage Vin and Input Offset Voltage Vin (0)

Output voltage Vout depends upon both Vin and Vin (0) inputs.

Output voltage

It can be understood that the output voltage Vout is a combination of ideal output voltage:

and Vin(0) × [1 + R2/R1]

and Vin(0) × [1 + R2/R1]

contributed by the input offset voltage Vin (0).

The difference in biasing voltages for VEE for the two input transistors in op amp produces input offset voltage of the order of few millivolts. It gets amplified by the amplifier and adds to the output voltage by its gain factor AV.

The output offset voltage in inverting amplifier contributed by the input offset voltage. Whenever an input voltage Vin is applied to inverting operational amplifier, output voltage Vout can be calculated by the equation  .

.

Further, if there is a finite magnitude of input offset voltage, Vin (0) across the two input terminals of op amp, the presence of input offset voltage is considered as shown in the circuit of Fig. 2.36.

Fig. 2.36 Output Voltage Vout for Inverting Op Amp for an Input Voltage Vin

Output voltage Vout depends upon both Vin (input voltage) and Vin (0) (input offset voltage) input voltages.

∴ Vout = AV (Vin + Vin (0)),

where voltage gain  for input voltage Vin.

for input voltage Vin.

Further, voltage gain  for input voltage Vin (0).

for input voltage Vin (0).

Therefore, total output voltage

It can be understood that Vout is a combination of ideal output voltage =  and

and  contributed by the input offset voltage.

contributed by the input offset voltage.

Fig. 2.37 shows the circuit for the following examples with different component values.

Fig. 2.37 Output Voltage Vout for Inverting Op Amp for an Input Voltage Vin and Input Offset Voltage Vin (0)

Example 2.7

- Calculate the voltage gain of an inverting op amp with R1 = 3.3 kΩ and resistor R2 = 33 kΩ.

- Calculate the output voltage when the input voltage = 0.5 V.

- Calculate the total output offset voltage for input offset voltage = 0.05 V.

Solution:

- Voltage gain of an inverting op amp

- Output voltage = Vout = AV × Vin = 10 × 0.5 = 5 V.

- Output voltage due to offset voltage Vout (0) = AV (Vin + Vin (0))

Vout (0) = 10 (0.5 + 0.05) = 5.5 V.

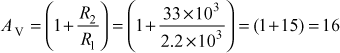

Example 2.8

- Calculate the voltage gain of non-inverting op amp if R1 = 2.2 kΩ and resistor R2 = 22 kΩ

- Calculate output voltage for input voltage of 0.2 V.

- Calculate the total offset voltage due to input offset voltage of 0.02 V.

Solution:

- Voltage gain of non-inverting op amp =

- Ideal output voltage with zero input offset voltage Vout = AV × Vin = 11 × 0.2 = 2.2 V.

- Output voltage with finite input offset voltage Vout (0) = AV (Vin +Vin (0))

Vout (0) = AV (Vin +Vin (0)) = 11 × (0.2 + 0.02) = 11 × 0.22 = 2.42 V.

Example 2.9

Calculate output offset voltage of inverting op amp with gain AV = 10 having resistors if R1 = 2.2 kΩ and R2 = 22 kΩ and input voltage Vin = 0.3 V. Input bias current is given as IB = 300 nA.

Solution: Ideal output voltage with zero input offset voltage Vout = AV × Vin = 10 × 0.3 = 3 V.

Output offset voltage due to bias current Vout (0) = IB × R2 = 300 × 10−9 × 22 × 103 = 6.6 mV

Example 2.10

An inverting op amp has R1 = 2.2 kΩ and R2 = 33 kΩ. Calculate the following:

- Ideal output voltage for an input signal of 5 mV.

- Output offset voltage for input offset current Ii (0) of value 300 nA. Output voltage for input bias current contribution of 400 mA.

Solution: Voltage gain of inverting op amp

- Ideal output voltage with zero input offset voltage Vout = AV × Vin = 16 × 5 × 10−3 = 80 mV.

- Output offset voltage with Vin = 5 mV and Ii (0) of value 300 nA.

= (16 × 5 × 10−3 + 33 × 103 × 300 × 10−9) = 89.9 mV.

= (16 × 5 × 10−3 + 33 × 103 × 300 × 10−9) = 89.9 mV.Therefore, V0 (0) = (80 mV + 9.9 mV) = 89.9 mV.

2.14 MINIMIZATION (ELIMINATION) OF OUTPUT OFFSET VOLTAGE

In operational amplifiers for offset null arrangement, two pins (terminals) (1) and (5) are provided for input offset voltage adjustment. Therefore, 10 kΩ potentiometer can be connected with its fixed terminal to pin-1 and pin-5 and sliding contact terminal −VEE (negative terminal of supply voltage at pin-4) in the op amp. The potentiometer (pot) is simply adjusted to cancel the input offset voltage so that its contribution to output voltage is simply zero.

Null-voltage Adjustment to Make Output Offset Voltage to Zero

Variable pot is used to balance or nullify the variable input offset voltages. The input offset voltages are present due to variations in DC bias VB to the two input transistors of differential amplifier used in op amps. Further, input offset voltages are due to the variations in device and ambient temperatures and the power supply voltages, etc (Fig. 2.38).

Fig. 2.38 Elimination of Output Offset Voltage Using Potentiometer at Pin-1, -4, and -5

The use of external potentiometer causes more resistance in parallel with one side and less resistance with the other part of differential amplifier circuit (depending upon the position of sliding contact on potentiometer). Such circuit balances out the input offset voltage conditions and reduces the output offset voltages to zero. Typical input offset voltages are of the order of ±15 mV for operational amplifiers.

2.15 MAXIMUM RATINGS OF OPERATIONAL AMPLIFIER

There will be deviations between the actual op amp parameters under ideal conditions and real life applications. The deviations are due to the variations in supply voltages, transistor biasing voltages, and device parameters. They vary with changes in ambient temperatures depending upon military and commercial (civil) applications.

For operational amplifiers, ideal and actual device parameters are as follows:

Ideal Characteristics of Operational Amplifier

Open-loop voltage gain: For ideal condition, open-loop voltage gain is infinity. The actual gain of op amp is limited by the values of the feedback resistor and input resistors. Further limitation is to the maximum power supply voltage swing and the input amplitudes.

Amplifier bandwidth: For ideal condition, bandwidth is infinity.

Input resistance: For ideal op amp, input resistance is infinity. In practice, input stage has very small resistance formed by forward-biased transistors of differential amplifiers of op amp at the input stage.

Output resistance: Zero output resistance for ideal op amp.

Fig. 2.39 Finite Gain of Op Amp due to Resistors R1 and R2

2.16 FREQUENCY RESPONSES OF OPERATIONAL AMPLIFIERS

Open-loop Frequency Response of Op Amp

Frequency response of an amplifier is a graph between frequency on X-axis (logarithm of frequency log10f) and gain or gain A, calculated in dB (decibels), which is 20 ![]() on Y-axis (see Fig. 2.40). The bandwidth of amplifier is taken as the frequency between the lower half-power frequency fL and higher half-power frequency FH. Further, the bandwidth of ideal op amp is infinity. However, the output capacitance across the op amp output port causes reduction in the bandwidth of the amplifier to a finite value.

on Y-axis (see Fig. 2.40). The bandwidth of amplifier is taken as the frequency between the lower half-power frequency fL and higher half-power frequency FH. Further, the bandwidth of ideal op amp is infinity. However, the output capacitance across the op amp output port causes reduction in the bandwidth of the amplifier to a finite value.

Fig. 2.40 Typical Frequency Response of Operational Amplifier

Closed-loop Frequency Response

From the typical frequency response characteristic, it can be observed that with the decrease in voltage gain A of op amp in decibel, the bandwidth is increasing (see Fig. 2.41). Therefore, an increase in the gain of op amp causes reduction in the bandwidth, gain × bandwidth maintains constant for an amplifier. The gain is unity at transition frequency fT, where the gain is 0 dB (20 log 101 = 0 dB). It shows the maximum bandwidth or useful frequency range of signals of op Amp as an amplifier. If fT = 2 mHz, signals having frequency range up to 2 mHz will be amplified by op amp.

Fig. 2.41 Typical Frequency Response of Operational Amplifier

2.17 EFFECT OF FINITE GBP ON INTEGRATED CIRCUITS

Gain-bandwidth product (GBP) of an amplifier: The maximum bandwidth of an amplifier occurs, when its voltage gain is unity. (Once, the amplifier gain is less than unity, it is not considered as an amplifier.) Unity gain occurs for emitter follower or source follower circuits. Maximum usable frequency fmax is considered as fT (transition frequency) or funity, when the op amp gain is unity.

Table 1.1 Snapshot of History of Processors and Their Transistor Count

. This is equal to the gain of common source FET amplifier (using single FET).

. This is equal to the gain of common source FET amplifier (using single FET).