Chapter 3

Behavioral Modeling and High-Level Simulation

The analysis of nonideal effects described in Chapter 2 allows us to derive precise equivalent circuits and models for the different ![]() M building blocks. This chapter shows how these models can be used for improving the accuracy and computational efficiency of system-level simulations. This constitutes an essential tool for the systematic design of

M building blocks. This chapter shows how these models can be used for improving the accuracy and computational efficiency of system-level simulations. This constitutes an essential tool for the systematic design of ![]() Ms as will be described in Chapter 4.

Ms as will be described in Chapter 4.

This chapter is organized as follows. Section 3.1 describes the systematic top-down/bottom-up synthesis methodology commonly followed to design ![]() Ms. Section 3.2 compares the different simulation approaches that can be used for the evaluation of

Ms. Section 3.2 compares the different simulation approaches that can be used for the evaluation of ![]() Ms, emphasizing on the benefits of behavioral simulation techniques. Section 3.3 focuses on the behavioral modeling technique and Section 3.4 shows an efficient way of implementing

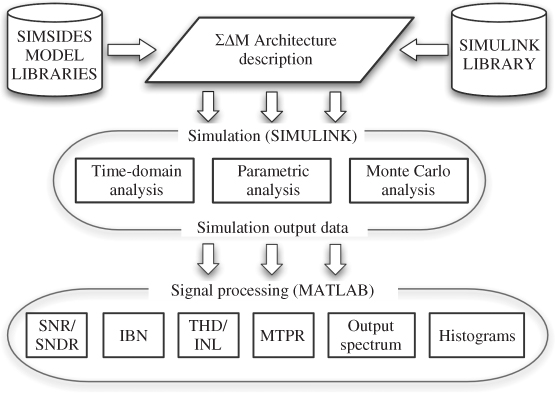

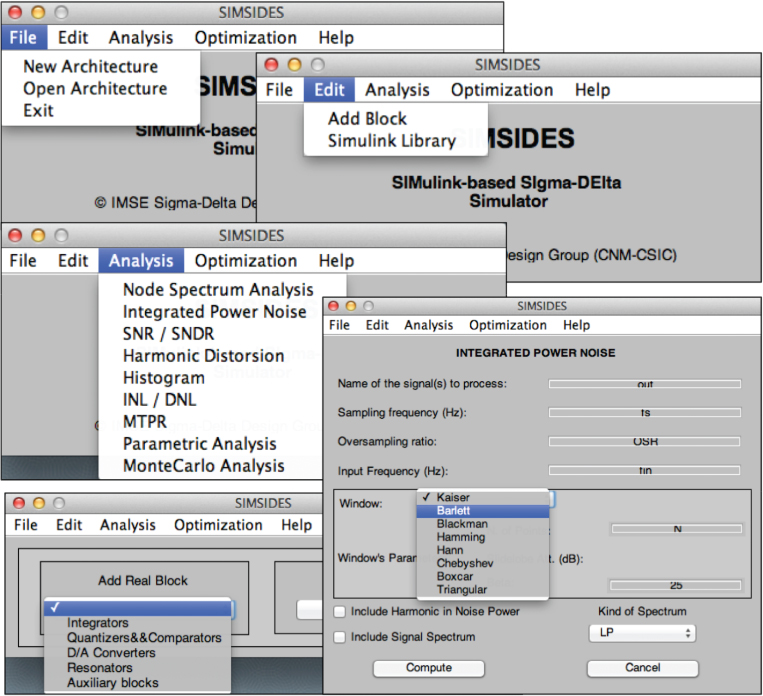

Ms, emphasizing on the benefits of behavioral simulation techniques. Section 3.3 focuses on the behavioral modeling technique and Section 3.4 shows an efficient way of implementing ![]() M block models in SIMULINK. Finally, Section 3.5 presents SIMSIDES, a time-domain behavioral simulator implemented in the MATLAB/SIMULINK environment that is based on the behavioral modeling techniques described in this chapter. Finally, two case studies are described in Section 3.6 to illustrate the use of SIMSIDES for the high-level sizing and simulation of

M block models in SIMULINK. Finally, Section 3.5 presents SIMSIDES, a time-domain behavioral simulator implemented in the MATLAB/SIMULINK environment that is based on the behavioral modeling techniques described in this chapter. Finally, two case studies are described in Section 3.6 to illustrate the use of SIMSIDES for the high-level sizing and simulation of ![]() Ms.

Ms.

3.1 Systematic Design Methodology of  Modulators

Modulators

One of the most common approaches used for the systematic design of high-performance ![]() Ms is based on the well-known top-down/bottom-up hierarchical synthesis methodology, conceptually illustrated in Figure 3.1a [1]. In this approach, a given system is divided into several hierarchical levels so that at each abstraction level of the system hierarchy, a design (or sizing) process takes place, thus transmitting (or mapping) the system specifications in a hierarchical way, from the top level to the bottom level. The reverse path in Figure 3.1a corresponds to the hierarchical bottom-up verification process of the system performance [2].

Ms is based on the well-known top-down/bottom-up hierarchical synthesis methodology, conceptually illustrated in Figure 3.1a [1]. In this approach, a given system is divided into several hierarchical levels so that at each abstraction level of the system hierarchy, a design (or sizing) process takes place, thus transmitting (or mapping) the system specifications in a hierarchical way, from the top level to the bottom level. The reverse path in Figure 3.1a corresponds to the hierarchical bottom-up verification process of the system performance [2].

Figure 3.1 Hierarchical synthesis methodology: (a) Conceptual block diagram and (b) system partitioning commonly used in ![]() Ms.

Ms.

3.1.1 System Partitioning and Abstraction Levels

Figure 3.1b depicts the hierarchical synthesis methodology that is usually adopted in the design of ![]() Ms. The system is partitioned in the following hierarchical levels [1–5]:

Ms. The system is partitioned in the following hierarchical levels [1–5]:

- Architecture or Topology Level: that is, single-loop or cascade

M, single-bit or multibit quantization, low-pass or band-pass, DT or CT implementation, etc.

M, single-bit or multibit quantization, low-pass or band-pass, DT or CT implementation, etc. - Subcircuit or Building-Block Level: that is, amplifiers, transconductors, comparators, capacitors, resistors, switches, etc.

- Cell Level: that is, the circuit topology of a given building block, for instance folded-cascode or telescopic cascode OTA, SC or current-steering DAC, nMOS or CMOS switches, etc.

- Physical Level: which covers from transistor-level schematics to the layout and chip implementation.

The design process of a ![]() M starts from the system-level specifications, that is, the effective resolution (ENOB) and the signal bandwidth (

M starts from the system-level specifications, that is, the effective resolution (ENOB) and the signal bandwidth (![]() ). The first goal is to find out the best modulator topology that fulfills these specifications with minimum power dissipation. To this purpose, initial ideal design equations of NTF and IBN—which are based on a linear model of the embedded quantizers as described in Chapter 1—are used for calculating approximate values for the main

). The first goal is to find out the best modulator topology that fulfills these specifications with minimum power dissipation. To this purpose, initial ideal design equations of NTF and IBN—which are based on a linear model of the embedded quantizers as described in Chapter 1—are used for calculating approximate values for the main ![]() M parameters, that is, OSR,

M parameters, that is, OSR, ![]() , and

, and ![]() . Once these parameters are known, the architecture topology can be synthesized using more accurate nonlinear model equations. To this purpose, Schreier's MATLAB Delta-Sigma toolbox [6, 7] is widely used in the

. Once these parameters are known, the architecture topology can be synthesized using more accurate nonlinear model equations. To this purpose, Schreier's MATLAB Delta-Sigma toolbox [6, 7] is widely used in the ![]() community. Usually, there are several topologies which are a priori good candidates to meet a given set of modulator specifications.

community. Usually, there are several topologies which are a priori good candidates to meet a given set of modulator specifications.

In order to determine the best ![]() M architecture, some analytical procedures are normally used for estimating the power consumption of the different

M architecture, some analytical procedures are normally used for estimating the power consumption of the different ![]() M topologies [8]. These procedures are based on compact expressions of the in-band noise power, similar to those derived in Chapter 2, which contemplate both architectural and technological features, and include the impact of some critical circuit errors such as thermal noise, finite OTA DC gain (or equivalent), and incomplete settling (GB and SR). Recent works demonstrate that nonlinearities can be efficiently incorporated in the Schreier's toolbox in order to fine tune this architectural exploration procedure [9].

M topologies [8]. These procedures are based on compact expressions of the in-band noise power, similar to those derived in Chapter 2, which contemplate both architectural and technological features, and include the impact of some critical circuit errors such as thermal noise, finite OTA DC gain (or equivalent), and incomplete settling (GB and SR). Recent works demonstrate that nonlinearities can be efficiently incorporated in the Schreier's toolbox in order to fine tune this architectural exploration procedure [9].

On the basis of the system-level estimation of the power consumption, a ranking of different candidate ![]() M architectures can be determined in order to decide the most suitable topology. Other important criteria at this step are the sensitivity to circuit element tolerances and mismatch (especially important in CT cascade topologies), the modulator loop-filter stability (particularly critical in high-order single-loop topologies), and/or the impact of the feedback DAC nonlinearity in multibit

M architectures can be determined in order to decide the most suitable topology. Other important criteria at this step are the sensitivity to circuit element tolerances and mismatch (especially important in CT cascade topologies), the modulator loop-filter stability (particularly critical in high-order single-loop topologies), and/or the impact of the feedback DAC nonlinearity in multibit ![]() Ms.

Ms.

3.1.2 Sizing Process

Once the modulator architecture has been selected, the next step consists of mapping the modulator-level specifications (ENOB and ![]() ) onto building-block specifications, that is, amplifier finite DC gain, output swing, GB, SR, etc. In this system-level design process—commonly referred to as high-level sizing—the design parameters are the electrical specifications of the different

) onto building-block specifications, that is, amplifier finite DC gain, output swing, GB, SR, etc. In this system-level design process—commonly referred to as high-level sizing—the design parameters are the electrical specifications of the different ![]() M subcircuits, namely, amplifiers, transconductors (in CT-

M subcircuits, namely, amplifiers, transconductors (in CT-![]() Ms), comparators, switches, and passive elements, that is, capacitors, resistors, and even inductors in the case of some BP-

Ms), comparators, switches, and passive elements, that is, capacitors, resistors, and even inductors in the case of some BP-![]() Ms [10]. The result of this multidimensional design space exploration constitutes the start point of the electrical or cell-level sizing process where, after selecting the appropriate topology for every

Ms [10]. The result of this multidimensional design space exploration constitutes the start point of the electrical or cell-level sizing process where, after selecting the appropriate topology for every ![]() M subcircuit, the corresponding transistor sizes and bias currents are obtained.

M subcircuit, the corresponding transistor sizes and bias currents are obtained.

Therefore, as shown in Figure 3.1b, the design methodology of ![]() Ms can be essentially divided into two main sizing processes: high-level sizing and cell-level sizing. Both of them are tasks that require a multitude of redesign iterations until the specifications at each level are met [11]. This procedure is conceptually depicted in Figure 3.2 [5]. At each iteration the performance of the circuit is evaluated at a given point of the design space, the design parameters are modified according to such an evaluation, and the procedure is repeated. Note that, although this procedure is the same in both high-level sizing and cell-level sizing, the design problem and its formulation is different in both cases. High-level sizing is a system-level synthesis process where the inputs variables are the system-level (modulator) specifications and the output variables are the building-block electrical specifications (design parameters). The latter specifications constitute the input variables for the cell-level sizing process.

Ms can be essentially divided into two main sizing processes: high-level sizing and cell-level sizing. Both of them are tasks that require a multitude of redesign iterations until the specifications at each level are met [11]. This procedure is conceptually depicted in Figure 3.2 [5]. At each iteration the performance of the circuit is evaluated at a given point of the design space, the design parameters are modified according to such an evaluation, and the procedure is repeated. Note that, although this procedure is the same in both high-level sizing and cell-level sizing, the design problem and its formulation is different in both cases. High-level sizing is a system-level synthesis process where the inputs variables are the system-level (modulator) specifications and the output variables are the building-block electrical specifications (design parameters). The latter specifications constitute the input variables for the cell-level sizing process.

Figure 3.2 Iterative procedure usually followed for high-level sizing and cell-level sizing.

The design parameter selection in Figure 3.2 can be carried out “manually,” that is, the entire design space is searched by considering all possible combinations of design parameters. In this case, once the whole design space has been completely explored and checked, the best design can be selected among those that meet the required specifications with the lowest (estimated) power dissipation and area. However, this “vast force” search approach is quite inefficient—and even unfeasible in many cases—in terms of computational resources and CPU time.1 Instead, an optimization engine is normally used for guiding the exploration of the design space. To this purpose, diverse algorithms such as simulated annealing [12] or genetic algorithms [4] may be used for the optimization. Usually, the same optimization methodology—normally based on the formulation and minimization of a design-oriented cost function—is used in both sizing tasks, that is, high-level sizing and cell-level sizing [3].

Different performance-evaluation strategies can be followed in Figure 3.2. Essentially, the cost function can be evaluated by means of equations or simulations [1]. Although the former is much faster than the latter, the accuracy of the results strongly depends on the topology, that is, the ![]() M architecture (for high-level sizing) and the circuit schematic (for cell-level sizing). For that reason, the most common approach followed by the

M architecture (for high-level sizing) and the circuit schematic (for cell-level sizing). For that reason, the most common approach followed by the ![]() M community has been based on using simulation as performance evaluation [3–5, 13–19]. However, in contrast to the optimization process—which is used in both sizing tasks—a different simulation approach is considered to evaluate the performance of either the entire (system-level) modulator or just a single building block, such as an amplifier or a comparator (cell-level). The latter can be analyzed using an electrical (SPICE-like) simulator with a high degree of accuracy and computational efficiency. On the contrary, the evaluation of the system-level (modulator) performance can be carried out following different simulation approaches discussed in the next section.

M community has been based on using simulation as performance evaluation [3–5, 13–19]. However, in contrast to the optimization process—which is used in both sizing tasks—a different simulation approach is considered to evaluate the performance of either the entire (system-level) modulator or just a single building block, such as an amplifier or a comparator (cell-level). The latter can be analyzed using an electrical (SPICE-like) simulator with a high degree of accuracy and computational efficiency. On the contrary, the evaluation of the system-level (modulator) performance can be carried out following different simulation approaches discussed in the next section.

3.2 Simulation Approaches for the High-Level Evaluation of  Ms

Ms

The high-level synthesis described above requires performing a large number of simulations. Depending on the design and required specifications, hundreds or even thousands of iterations may be needed. Therefore, in order to make this part of the design feasible, simulations should consume short CPU times. This is particularly critical in the case of ![]() Ms because of their nonlinear oversampled-data nature. For that reason, in order to compute the IBN power at the output of a

Ms because of their nonlinear oversampled-data nature. For that reason, in order to compute the IBN power at the output of a ![]() M with enough numerical accuracy, a transient simulation of at least

M with enough numerical accuracy, a transient simulation of at least ![]() clock cycles is usually required.2 Therefore, a transient analysis of a

clock cycles is usually required.2 Therefore, a transient analysis of a ![]() M using common transistor-level (SPICE-like) circuit simulation is too slow for allowing an efficient space exploration, regardless of whether it is performed by a manual parameter sweeps or guided by an optimizer. As an example, a

M using common transistor-level (SPICE-like) circuit simulation is too slow for allowing an efficient space exploration, regardless of whether it is performed by a manual parameter sweeps or guided by an optimizer. As an example, a ![]() -point transient analysis in HSPICE of a cascade 2-1 SC-

-point transient analysis in HSPICE of a cascade 2-1 SC-![]() M including the clock-phase generator and other auxiliary subcircuits takes over 85 h CPU time in a 2.2-GHz core with 4-GB RAM. This means that a synthesis process based on this performance-evaluation approach would take months or even years! Hence, transistor-level simulation is obviously computationally unfeasible for synthesis purposes, and it is normally used only for the final design verification, as will be discussed in Chapter 4 [19].

M including the clock-phase generator and other auxiliary subcircuits takes over 85 h CPU time in a 2.2-GHz core with 4-GB RAM. This means that a synthesis process based on this performance-evaluation approach would take months or even years! Hence, transistor-level simulation is obviously computationally unfeasible for synthesis purposes, and it is normally used only for the final design verification, as will be discussed in Chapter 4 [19].

In addition to the long CPU times required to simulate a ![]() M at transistor level, another practical issue associated with this simulation approach is related to the convergence problems that typically arise in electrical simulators such as HSPICE [21] or Spectre [22]. Moreover, transistor-level simulation is not a suited simulation method for the high-level sizing process because the design parameters—that is, device sizes and biasing—are hierarchically far from system-level specifications. Hence, it is quite difficult for a designer to get an insight into what is happening at the system level by running simulations based on transistor-level models, as the impact of a given transistor width or length has a direct impact on many different performance metrics of

M at transistor level, another practical issue associated with this simulation approach is related to the convergence problems that typically arise in electrical simulators such as HSPICE [21] or Spectre [22]. Moreover, transistor-level simulation is not a suited simulation method for the high-level sizing process because the design parameters—that is, device sizes and biasing—are hierarchically far from system-level specifications. Hence, it is quite difficult for a designer to get an insight into what is happening at the system level by running simulations based on transistor-level models, as the impact of a given transistor width or length has a direct impact on many different performance metrics of ![]() M building blocks. For instance, the size of the input differential-pair transistor of an OTA affects the values of finite DC gain, nonlinearity, input parasitic capacitance, GB, etc.

M building blocks. For instance, the size of the input differential-pair transistor of an OTA affects the values of finite DC gain, nonlinearity, input parasitic capacitance, GB, etc.

3.2.1 Alternatives to Transistor-Level Simulation

The above-mentioned reasons suggest that increasing the abstraction level of the simulation approach is mandatory to both speed up the simulations and work with design parameters that are closer to the system-level specifications. However, the price to pay for increasing the abstraction level (and consequently the simulation speed) is the loss of accuracy. This problem has motivated the exploration of different simulation approaches in order to optimize the trade-off between CPU time and precision—conceptually illustrated in Figure 3.3 [4].

Figure 3.3 Comparison of simulation approaches in terms of CPU time and accuracy.

An alternative to the transistor-level simulation approach that also runs on electrical simulators consists of using circuit macromodels. These macromodels are usually implemented as equivalent circuits based on ideal voltage- and current-controlled sources that allow to model the main nonideal effects. This approach has the advantage that it can be combined with transistor-level schematics using the same (electrical) simulator. Thus, critical parts of the system can be modeled at transistor level, whereas the remaining ones can be modeled less accurately with macromodels, leading to what is commonly known as a multilevel simulation

technique [2]. Obviously, the simulation CPU time will increase with the number of parts being modeled at transistor level. Therefore, in most practical cases, the use of this approach does not imply a significant improvement with respect to the full transistor-level simulation approach.3

As an example, Table 3.1 compares the CPU times required to simulate a fourth-order single-loop ![]() M in Cadence Spectre circuit simulator, considering

M in Cadence Spectre circuit simulator, considering ![]() -point transient analysis with moderate setting [22]. The modulator topology consists of a cascade of resonators with feed-forward summation (Figure 1.31b). This architecture requires five amplifiers to implement the four loop-filter integrators and the active adder. Simulations were carried out considering ideal macromodels for the switches and the digital blocks (including the clock-phase generator). It can be noted from Table 3.1 that the CPU time increases by approximately 30–40 min with every additional amplifier that is simulated considering a transistor-level implementation. The overall CPU time goes from 45 min required to simulate the entire system with macromodels to 4 h when all amplifiers are implemented at transistor level. These CPU times are more than doubled if conservative mode option is considered in the simulation; over 8 h are required to complete the simulation.

-point transient analysis with moderate setting [22]. The modulator topology consists of a cascade of resonators with feed-forward summation (Figure 1.31b). This architecture requires five amplifiers to implement the four loop-filter integrators and the active adder. Simulations were carried out considering ideal macromodels for the switches and the digital blocks (including the clock-phase generator). It can be noted from Table 3.1 that the CPU time increases by approximately 30–40 min with every additional amplifier that is simulated considering a transistor-level implementation. The overall CPU time goes from 45 min required to simulate the entire system with macromodels to 4 h when all amplifiers are implemented at transistor level. These CPU times are more than doubled if conservative mode option is considered in the simulation; over 8 h are required to complete the simulation.

Table 3.1 CPU time required to simulate a fourth-order single-loop ![]() M considering different situations in a multilevel approach

M considering different situations in a multilevel approach

| Simulation | CPU Time | CPU Time |

| Approach | (moderate mode) | (conservative mode) |

| All opamps macromodeled | 45 min | 2 h |

| One transistor-level opamp | 1 h, 20 min | 4 h |

| Two transistor-level opamps | 2 h | 5 h, 30 min |

| Five transistor-level opamps | 4 h | 8 h, 20 min |

Simulations were carried out in a SUN Fire X2200 M2 server with 4-GB RAM and a 2.2-GHz Dual Core AMD Opteron CPU, running a 64-bit Linux operating system.

As stated above, it is important to mention that the data in Table 3.1 does not account for the time consumed to simulate the digital part of the system—that is, feedback DAC, DEM, clock-phase generator, digital output buffers, etc.—that was considered ideal in these simulations. If transistor-level implementation is considered for those circuits, the overall CPU time for a conservative simulation mode is increased up to one day or even more. Under these conditions, a ![]() -point transient simulation would take over three days CPU time!

-point transient simulation would take over three days CPU time!

3.2.2 Event-Driven Behavioral Simulation Technique

As illustrated in Figure 3.3, the best trade-off between accuracy and speed is achieved by the so-called event-driven behavioral simulation technique [14]. In this approach—conceptually illustrated in Figure 3.4—the modulator is partitioned into a set of subcircuits—often called basic or building blocks—with independent functionality [1, 12]. In ![]() Ms, the most important building blocks are integrators and resonators,4 and the embedded quantizers, made up of an ADC and a DAC. The behavioral modeling technique thus consists in describing each of these building blocks by a model, often referred to as a behavioral model or behavioral law, that emulates their actual operation and takes into account the effect of the main nonideal circuit error mechanisms described in Chapter 2.

Ms, the most important building blocks are integrators and resonators,4 and the embedded quantizers, made up of an ADC and a DAC. The behavioral modeling technique thus consists in describing each of these building blocks by a model, often referred to as a behavioral model or behavioral law, that emulates their actual operation and takes into account the effect of the main nonideal circuit error mechanisms described in Chapter 2.

Figure 3.4 Conceptual block diagram of the behavioral modeling and simulation process.

Note that, strictly speaking, the definition given above for a behavioral model does not necessarily imply that the model is implemented by equations. Indeed, there is an alternative approach that consists of using the so-called table look-up models [23, 24]. The idea behind these models is based on extracting the input–output characteristics of a given building block from electrical simulations and then mapping the extracted information in the form of tables which are used for modeling the functionality of that building block. This way, those tables are used as an alternative to the original transistor-level circuits to accelerate the simulations with a high degree of accuracy. However, the price to pay is the loss of generality and of reusability of the models because they strongly depend on the circuit topology. Indeed, new tables have to be generated whenever the architecture itself or any circuit parameter is modified.

For the aforementioned reasons, table look-up methodologies are more suited for bottom-up verification than for high-level synthesis. Indeed, the most commonly used behavioral modeling approach is based on finite-difference equations. These equations describe the functionality of building blocks by expressing their output signals in terms of their internal state variables and their input signals. Therefore, the accuracy of the behavioral simulation strongly depends on how precisely those equations describe the actual behavior of the corresponding ![]() M subcircuit [5, 15, 19].

M subcircuit [5, 15, 19].

3.2.3 Programming Languages and Behavioral Modeling Platforms

Behavioral models and the corresponding simulation engine (Figure 3.4) can be codified and implemented in a number of platforms using different programming/modeling languages such as C. The latter is a general purpose and universal language that presents high flexibility in describing behavioral models and allowing implementation of behavioral simulation tools in many different operating systems and platforms. Early approaches for the behavioral-level simulation of ![]() Ms were completely compiled in C language, demonstrating to be very appropriate for fast simulation and high-level synthesis of

Ms were completely compiled in C language, demonstrating to be very appropriate for fast simulation and high-level synthesis of ![]() Ms [12].

Ms [12].

The main disadvantage of C-coded behavioral modeling and simulation is that it is restricted to a limited number of building-block models—that is, those included in the corresponding (previously programmed) libraries—thus reducing the kind of ![]() M architectures that can be simulated. From this point of view, this approach is not flexible because building-block models cannot be easily modified and the extension to new building blocks and architectures is constrained by the capabilities of the simulation engine, as well as by the designer skills on C programming language. This may explain why the majority of reported C-based behavioral simulators are intended to simulate SC-

M architectures that can be simulated. From this point of view, this approach is not flexible because building-block models cannot be easily modified and the extension to new building blocks and architectures is constrained by the capabilities of the simulation engine, as well as by the designer skills on C programming language. This may explain why the majority of reported C-based behavioral simulators are intended to simulate SC-![]() Ms [4, 12].

Ms [4, 12].

In order to overcome all these problems, several alternative approaches have been followed to implement behavioral models. One approach that has gained popularity with ![]() M designers is based on the use of standard hardware description languages (HDL), such as either VHDL [25] and its analog extensions [26] or Verilog and Verilog AMS [19]. As will be shown in Chapter 4, VHDL-based behavioral model descriptions can be combined with HDL models of other analog, digital, and mixed-signal circuits, and they can be integrated in the design flow of commercial design environments such as Cadence Design FrameWork II [27].

M designers is based on the use of standard hardware description languages (HDL), such as either VHDL [25] and its analog extensions [26] or Verilog and Verilog AMS [19]. As will be shown in Chapter 4, VHDL-based behavioral model descriptions can be combined with HDL models of other analog, digital, and mixed-signal circuits, and they can be integrated in the design flow of commercial design environments such as Cadence Design FrameWork II [27].

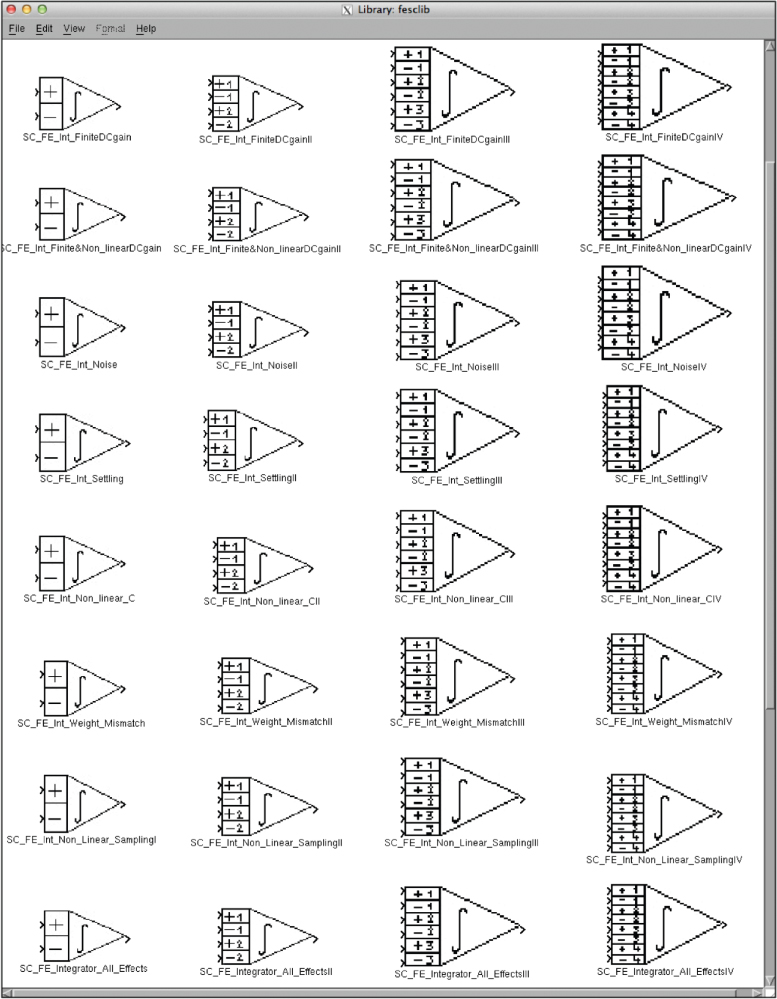

An alternative and widely used approach for the behavioral modeling and simulation of ![]() Ms consists of using the MATLAB/SIMULINK platform [28, 29]. This well-known mathematical software—which constitutes a standard CAD platform today in science and engineering—presents a number of advantages in terms of friendliness of the user interface: flexibility for the extension of building blocks library and for the simulation of either DT or CT systems, good trade-off between accuracy and simulation speed, and a direct access to very powerful tools for signal postprocessing [5, 15].

Ms consists of using the MATLAB/SIMULINK platform [28, 29]. This well-known mathematical software—which constitutes a standard CAD platform today in science and engineering—presents a number of advantages in terms of friendliness of the user interface: flexibility for the extension of building blocks library and for the simulation of either DT or CT systems, good trade-off between accuracy and simulation speed, and a direct access to very powerful tools for signal postprocessing [5, 15].

The rest of this chapter is devoted to the behavioral modeling and simulation of ![]() Ms in the MATLAB/SIMULINK environment, explaining the different approaches to model

Ms in the MATLAB/SIMULINK environment, explaining the different approaches to model ![]() M building blocks and how to use these models for the efficient simulation of

M building blocks and how to use these models for the efficient simulation of ![]() Ms.

Ms.

3.3 Implementing  M Behavioral Models

M Behavioral Models

The analysis of error mechanisms in ![]() Ms allows designers to obtain a set of closed-form expressions that shows the degradation caused by circuit-level electrical parameters at different levels of the modulator hierarchy. On the one hand, the analytical procedure described in Chapter 2 is used for propagating the effect of errors from the building-block (either integrator or resonator) transfer function to the modulator NTF, in order to obtain the

Ms allows designers to obtain a set of closed-form expressions that shows the degradation caused by circuit-level electrical parameters at different levels of the modulator hierarchy. On the one hand, the analytical procedure described in Chapter 2 is used for propagating the effect of errors from the building-block (either integrator or resonator) transfer function to the modulator NTF, in order to obtain the ![]() M performance metrics, that is, IBN and SNDR. As stated in Section 3.1, simplified versions of these equations relating architectural parameters (

M performance metrics, that is, IBN and SNDR. As stated in Section 3.1, simplified versions of these equations relating architectural parameters (![]() ,

, ![]() , and

, and ![]() ) to circuit-level errors are very appropriate for initial system-level estimations of the power consumption and preliminary architecture selection. On the other hand, precise equations describing the functionality of building blocks as a function of error parameters constitute the basis for building accurate behavioral models. To this end, those equations must be transformed into computational flowcharts that can be implemented by programming languages. This procedure is illustrated in the next section for two basic building blocks: an SC FE integrator and a Gm-C integrator. These two circuits are basic building blocks of SC- and CT-

) to circuit-level errors are very appropriate for initial system-level estimations of the power consumption and preliminary architecture selection. On the other hand, precise equations describing the functionality of building blocks as a function of error parameters constitute the basis for building accurate behavioral models. To this end, those equations must be transformed into computational flowcharts that can be implemented by programming languages. This procedure is illustrated in the next section for two basic building blocks: an SC FE integrator and a Gm-C integrator. These two circuits are basic building blocks of SC- and CT-![]() Ms, respectively.5

Ms, respectively.5

3.3.1 From Circuit Analysis to Computational Algorithms

Figure 3.5 shows the conceptual (single-ended) schematic of an SC FE integrator (Figure 3.5a) and a Gm-C integrator (Figure 3.5b). Considering ideal circuit elements, the output voltage ![]() of Figure 3.5a is given by the following finite-difference equation:

of Figure 3.5a is given by the following finite-difference equation:

where ![]() is the input voltage,

is the input voltage, ![]() and

and ![]() are, respectively, the sampling and integration capacitors, and

are, respectively, the sampling and integration capacitors, and ![]() stands for the

stands for the ![]() th sampling time instant, with

th sampling time instant, with ![]() being the sampling period.

being the sampling period.

Figure 3.5 Conceptual schematic of: (a) an SC FE integrator and (b) a Gm-C integrator.

Note that Equation 3.1 is easy to solve numerically because the value of the output voltage at a given time instant ![]() can be computed by adding the value of the output at the previous sampling period

can be computed by adding the value of the output at the previous sampling period ![]() and the value of the input voltage at

and the value of the input voltage at ![]() multiplied by

multiplied by ![]() . This operation is conceptually represented by the flowchart shown in Figure 3.6 and can be expressed in a computational model as follows:

. This operation is conceptually represented by the flowchart shown in Figure 3.6 and can be expressed in a computational model as follows:

vinit=0;

Cs=1e‐12;

Ci=1e‐12;

n=1;

nfinal=10;

vi(1:10)=1;

vo(1)=vinit;

while n<=nfinal

n=n+1;

vo(n)=vo(n‐1)+Cs/Ci*vi(n‐1);

end;

Figure 3.6 Flowchart used for computing behavioral Equation 3.1.

where vinit stands for the initial condition, nfinal stands for the final sampling instant, and ![]() pF has been assumed.6 A while statement has been considered, although other iterative statements such as if or for can be used as well.

pF has been assumed.6 A while statement has been considered, although other iterative statements such as if or for can be used as well.

The ideal functionality of Figure 3.5b can be mathematically expressed by the following differential equation:

where ![]() is the transconductance and

is the transconductance and ![]() is the integration capacitance. The above expression can be integrated by MATLAB/SIMULINK solvers very efficiently [28].

is the integration capacitance. The above expression can be integrated by MATLAB/SIMULINK solvers very efficiently [28].

The ideal models described for SC and CT integrators in the time domain can be implemented very easily in the frequency domain using SIMULINK elementary library blocks [29] as illustrated in Figure 3.7. The corresponding transfer functions can be obtained by applying a ![]() -transform and an

-transform and an ![]() -transform to Equations 3.1 and 3.2, respectively, giving

-transform to Equations 3.1 and 3.2, respectively, giving

where ![]() and

and ![]() stand for the

stand for the ![]() -transforms of

-transforms of ![]() and

and ![]() in Figure 3.5a and

in Figure 3.5a and ![]() and

and ![]() are the

are the ![]() -transforms of

-transforms of ![]() and

and ![]() in Figure 3.5b. Both models can be computed very efficiently using the discrete-time and continuous-time solvers provided in the SIMULINK software [29].

in Figure 3.5b. Both models can be computed very efficiently using the discrete-time and continuous-time solvers provided in the SIMULINK software [29].

Figure 3.7 Ideal SIMULINK models of the integrators shown in Figure 3.5.

3.3.2 Time-Domain versus Frequency-Domain Behavioral Models

The ideal behavioral models described can be either represented in the time domain by Equations 3.1 and 3.2 or in the frequency domain by Equation 3.3. There is an exact correspondence between both of them, giving rise to identical results. Indeed, provided that the ![]() M building blocks can be treated as LTI systems, the most convenient (and simplest) way of modeling their behavior is using frequency-domain transfer functions. However, this is not very useful in most practical situations because, as stated in Chapter 2, the performance of

M building blocks can be treated as LTI systems, the most convenient (and simplest) way of modeling their behavior is using frequency-domain transfer functions. However, this is not very useful in most practical situations because, as stated in Chapter 2, the performance of ![]() Ms is degraded by the effect of circuit-level errors. As shown in this chapter, the majority of circuit errors are modeled in a more accurate way if behavioral models are described in the time domain instead of in the frequency domain.

Ms is degraded by the effect of circuit-level errors. As shown in this chapter, the majority of circuit errors are modeled in a more accurate way if behavioral models are described in the time domain instead of in the frequency domain.

As an example, let us consider the effect of OTA finite DC gain on the integrators in Figure 3.5. This effect can be modeled as shown in Figure 3.8, where ![]() stands for the finite DC voltage gain of the opamp in the SC FE integrator and

stands for the finite DC voltage gain of the opamp in the SC FE integrator and ![]() is the finite output conductance of the transconductor in the Gm-C integrator, such that the finite DC gain is given by

is the finite output conductance of the transconductor in the Gm-C integrator, such that the finite DC gain is given by ![]() . The time-domain equations describing the behavior of the integrators in Figure 3.8 are given by

. The time-domain equations describing the behavior of the integrators in Figure 3.8 are given by

where ![]() and

and ![]() . Note that the behavioral model of the SC integrator with finite DC gain can be computed using a flowchart similar to the ideal one shown in Figure 3.6 by simply modifying the corresponding multiplication factors of

. Note that the behavioral model of the SC integrator with finite DC gain can be computed using a flowchart similar to the ideal one shown in Figure 3.6 by simply modifying the corresponding multiplication factors of ![]() and

and ![]() according to Equation 3.4. In the case of CT integrators, the corresponding differential equation can be numerically solved using either C or MATLAB code as programming language.7

according to Equation 3.4. In the case of CT integrators, the corresponding differential equation can be numerically solved using either C or MATLAB code as programming language.7

Figure 3.8 Modeling OTA finite DC gain in: (a) SC FE integrators and (b) Gm-C integrators.

Operating in a similar way as in the previous section, the (frequency-domain) transfer functions of both circuits in Figure 3.8 can be obtained yielding

The above-mentioned transfer functions can be easily modeled using elementary blocks of the SIMULINK library as shown in Figure 3.9. However, as stated above, frequency-domain models are not useful when several nonideal and nonlinear effects are considered.8 Instead, a time-domain model considering the operation during different clock phases is more accurate to include different circuit-level phenomena. In order to illustrate this, let us analyze the circuit in Figure 3.8a in both clock phases, ![]() and

and ![]() .

.

Figure 3.9 Modeling the effect of finite DC gain on the integrators transfer function in SIMULINK.

At the end of clock phase ![]() (sampling phase) of period

(sampling phase) of period ![]() the sampling capacitor

the sampling capacitor ![]() and the integration capacitor

and the integration capacitor ![]() are charged at the following voltages, respectively,

are charged at the following voltages, respectively,

where ![]() denotes the voltage at the output of the opamp in Figure 3.8a.

denotes the voltage at the output of the opamp in Figure 3.8a.

At the end of clock phase ![]() (integration phase) of period

(integration phase) of period ![]() the voltages across

the voltages across ![]() and

and ![]() are, respectively, given by

are, respectively, given by

The charge-balance equation at the negative input node of the opamp in Figure 3.8a can be written as

Replacing Equations 3.6 and 3.7 into Equation 3.8 gives

Taking into account that ![]() , the above expression transforms into the SC part of Equation 3.4, which after taking the

, the above expression transforms into the SC part of Equation 3.4, which after taking the ![]() -transform results in Equation 3.5.

-transform results in Equation 3.5.

Note that the charge-balance analysis described in Equations 3.8 is more complex than using ![]() -domain transfer functions to model simple phenomena, such as the ideal behavior of simple building blocks and/or the effect of linear errors, such as finite DC gain. However, as the model becomes more accurate including more nonideal circuit errors and/or nonlinearities, the charge-balance model is the most suitable approach to be implemented in a behavioral simulator. As an illustration, let us assume the voltage dependence of the finite DC gain in SC FE integrators.9 This nonlinear effect can be modeled by replacing the voltage linear gain

-domain transfer functions to model simple phenomena, such as the ideal behavior of simple building blocks and/or the effect of linear errors, such as finite DC gain. However, as the model becomes more accurate including more nonideal circuit errors and/or nonlinearities, the charge-balance model is the most suitable approach to be implemented in a behavioral simulator. As an illustration, let us assume the voltage dependence of the finite DC gain in SC FE integrators.9 This nonlinear effect can be modeled by replacing the voltage linear gain ![]() parameter in Figure 3.8a by a nonlinear function of the output voltage

parameter in Figure 3.8a by a nonlinear function of the output voltage ![]() , where

, where ![]() represents the

represents the ![]() th-order nonlinear voltage-gain coefficient [31]. Taking these nonlinear effects into account, the charge-balance equations transform into the following ones:

th-order nonlinear voltage-gain coefficient [31]. Taking these nonlinear effects into account, the charge-balance equations transform into the following ones:

where ![]() and

and ![]() .

.

From Equations 3.9 and 3.10, it can be shown that the nonlinear finite-difference equation describing the behavior of the integrator can be written as

Note that an iterative procedure is needed to compute the behavioral model in Equation 3.11, because the output voltage of the opamp ![]() depends on the amplifier nonlinear gain, which in turns changes with

depends on the amplifier nonlinear gain, which in turns changes with ![]() .

.

3.3.3 Implementing Time-Domain Behavioral Models in MATLAB

The behavioral model described by Equations 3.10 and 3.11 can be programmed using a so-called M-file [28] with the MATLAB code shown in Figure 3.10, where C1 and C2 are, respectively, the sampling capacitance (![]() ) and integration capacitance (

) and integration capacitance (![]() ), and count is a parameter that determines the clock phase, with count=0 corresponding to the sampling phase and count=1 to the integration phase. This way, as illustrated in Figure 3.11, the clock-phase scheme can be selected to be either the one shown in Figure 3.8a or the complementary one, that is, with the input switch being clocked at

), and count is a parameter that determines the clock phase, with count=0 corresponding to the sampling phase and count=1 to the integration phase. This way, as illustrated in Figure 3.11, the clock-phase scheme can be selected to be either the one shown in Figure 3.8a or the complementary one, that is, with the input switch being clocked at ![]() . The input signal is modeled by a matrix made up of two vectors, u(1) and u(2), while the output is stored in a variable named y, with yold modeling the output sample stored in the previous clock phase and ytemp being a temporal state variable used until convergence is achieved.

. The input signal is modeled by a matrix made up of two vectors, u(1) and u(2), while the output is stored in a variable named y, with yold modeling the output sample stored in the previous clock phase and ytemp being a temporal state variable used until convergence is achieved.

Figure 3.10 MATLAB code for the behavioral model of the SC FE integrator in Figure 3.8a including the effect of the amplifier gain nonlinearity.

Figure 3.11 Meaning of count in the behavioral model of an SC FE integrator, considering that the input switch clock phase is: (a) ![]() and (b)

and (b) ![]() .

.

Note that the convergence criterion used in the iterative procedure is AVVAR=abs[(AVOLD =AVNEW) /AVNEW] < thrs, where thrs models the threshold value selected for convergence (usually thrs=0.01), abs(x) stands for the absolute value of x, and AVOLD and AVNEW are, respectively, the old and new values of the parameter to be solved—![]() in this example. Following this criterion, convergence is normally reached in three or four iterations, which does not result in excessive CPU time [5].

in this example. Following this criterion, convergence is normally reached in three or four iterations, which does not result in excessive CPU time [5].

Figure 3.12 shows a SIMULINK model of the SC FE integrator in Figure 3.8a with nonlinear DC gain based on the MATLAB code described in Figure 3.10. Note that a MATLAB function block—named MATLAB Fcn block in SIMULINK [29]—is used for this purpose. Figure 3.12b shows the MATLAB Fcn used in this example, called intfescavnl, that applies the M-file shown in Figure 3.10 to the input of the block. The input arguments of the MATLAB functions (e.g., AV,AVNL1,AVNL2...C1,C2,PHI) are included in the Function Block Parameters dialogue window [29] illustrated in Figure 3.12c, which can be configured by the user. Note that two additional blocks in Figure 3.12b are used for properly sampling the output signal at the correct sampling instant. One of these blocks is a Unit Delay block that adds an extra delay of ![]() . The other block is a so-called SIMULINK S-function block, which will be explained in Section 3.4.

. The other block is a so-called SIMULINK S-function block, which will be explained in Section 3.4.

Figure 3.12 SIMULINK model of the SC FE integrator shown in Figure 3.8a: (a) SIMULINK mask, (b) SIMULINK block diagram including a MATLAB function, and (c) associated dialogue window.

One of the problems of using M-files is that the MATLAB interpreter is called at each time step, and this slows down the simulation [28]. This problem is aggravated as the model complexity increases. Let us consider, for instance, a cascade 2-1-1 SC-![]() M in which all building blocks are ideal except for the nonlinear DC gain—modeled by the M-file shown in Figure 3.10. Figure 3.13 shows the SIMULINK block diagram of the modulator, highlighting its main parts. A simulation of

M in which all building blocks are ideal except for the nonlinear DC gain—modeled by the M-file shown in Figure 3.10. Figure 3.13 shows the SIMULINK block diagram of the modulator, highlighting its main parts. A simulation of ![]() clock periods of this modulator takes 148 s in a 2.4-GHz core with 4-GB RAM.10

clock periods of this modulator takes 148 s in a 2.4-GHz core with 4-GB RAM.10

Figure 3.13 SIMULINK model of a cascade 2-1-1 SC-![]() M with nonlinear DC gain modeled using the M-file shown in Figure 3.10.

M with nonlinear DC gain modeled using the M-file shown in Figure 3.10.

An alternative approach to the simulation of ![]() Ms based on MATLAB functions was proposed in [15, 32]. The models included in this toolbox [33] are based on the interconnection of SIMULINK standard library blocks, being very intuitive and useful for system-level evaluation. However, the block library is limited to SC circuits and uses relatively simple models which do not take into account some limitations such as, for instance, the nonlinearities associated with the OTA DC gain and with capacitors. The models are very intuitive, although the implementation of each building block requires several sets of elementary SIMULINK blocks using MATLAB functions, with the subsequent penalty in computation time. This issue is very critical for an optimization-based synthesis process, as stated in previous sections. Moreover, most parts of the models are implemented in the

Ms based on MATLAB functions was proposed in [15, 32]. The models included in this toolbox [33] are based on the interconnection of SIMULINK standard library blocks, being very intuitive and useful for system-level evaluation. However, the block library is limited to SC circuits and uses relatively simple models which do not take into account some limitations such as, for instance, the nonlinearities associated with the OTA DC gain and with capacitors. The models are very intuitive, although the implementation of each building block requires several sets of elementary SIMULINK blocks using MATLAB functions, with the subsequent penalty in computation time. This issue is very critical for an optimization-based synthesis process, as stated in previous sections. Moreover, most parts of the models are implemented in the ![]() -domain, and hence, the circuit behavior during different clock phases is not taken into account. This may lead to a not very precise modeling of some errors associated with the integrator transient response, as discussed in Section 2.4.

-domain, and hence, the circuit behavior during different clock phases is not taken into account. This may lead to a not very precise modeling of some errors associated with the integrator transient response, as discussed in Section 2.4.

Figure 3.14 shows an exemplary SIMULINK block diagram of a cascade 2-1-1 SC-![]() M modeled with the SIMULINK toolbox developed by Brigatti [33]. The integrator behavioral models already include finite open-loop opamp DC gain, incomplete settling error, slew rate, mismatch capacitor ratio error, and thermal noise. In addition, the main nonlinear effects were added to the original model, namely nonlinear sampling switch on-resistance, nonlinear capacitors, and nonlinear open-loop opamp DC gain, the latter being modeled using the M-function given in Figure 3.10. The main parts of this block diagram, as well of those parameters required to simulate the modulator, are shown in Figure 3.14. A

M modeled with the SIMULINK toolbox developed by Brigatti [33]. The integrator behavioral models already include finite open-loop opamp DC gain, incomplete settling error, slew rate, mismatch capacitor ratio error, and thermal noise. In addition, the main nonlinear effects were added to the original model, namely nonlinear sampling switch on-resistance, nonlinear capacitors, and nonlinear open-loop opamp DC gain, the latter being modeled using the M-function given in Figure 3.10. The main parts of this block diagram, as well of those parameters required to simulate the modulator, are shown in Figure 3.14. A ![]() -point simulation in a 2.4-GHz core with 4-GB RAM takes 80 s. This CPU time can be reduced to 8 s if the

-point simulation in a 2.4-GHz core with 4-GB RAM takes 80 s. This CPU time can be reduced to 8 s if the ![]() M building-block behavioral modes are implemented in C-code using the so-called SIMULINK S-functions [34].

M building-block behavioral modes are implemented in C-code using the so-called SIMULINK S-functions [34].

Figure 3.14 SIMULINK model of a cascade 2-1-1 SC-![]() M using Brigatti's toolbox [33].

M using Brigatti's toolbox [33].

A System-function or S-function is a computer language description of a SIMULINK block that can be written in MATLAB code, Ada, Fortran, or C-code [34]. The latter are special-purpose source files that allow inclusion of computation algorithms written in C to SIMULINK models. This approach speeds up the simulations—up to 50 times faster in some cases—compared to the use of MATLAB functions or M-files to code the behavioral models, even when the accelerator mode is used [5]. In addition to the benefits in terms of CPU time, the use of S-functions for the behavioral simulation of ![]() Ms allows designers to model circuit-level error mechanisms in a more accurate way, as will be described in the rest of this chapter.

Ms allows designers to model circuit-level error mechanisms in a more accurate way, as will be described in the rest of this chapter.

3.3.4 Building Time-Domain Behavioral Models as SIMULINK C-MEX S-Functions

Figure 3.15a illustrates a step-by-step procedure to implement the behavioral model of a ![]() M building block in the SIMULINK environment using C-coded S-functions. The main steps are the following [5]:

M building block in the SIMULINK environment using C-coded S-functions. The main steps are the following [5]:

- Definition of a Computational Model. Given a

M building block that includes a set of nonidealities, a computational model that allows to calculate the output as a function of the input(s) and the internal states (if any) defined.

M building block that includes a set of nonidealities, a computational model that allows to calculate the output as a function of the input(s) and the internal states (if any) defined. - Generation of the C Code corresponding to the computational model defined in the previous step.

- Implementation of the Computational Model into a C-MEX S-Function. To this purpose, SIMULINK provides different S-function template files that can accommodate the C-coded computational model generated in the previous step. Both DT and CT building blocks can be modeled, as will be shown in next sections. S-function template files are composed of several subsections, named callback methods, which are routines that perform different tasks required at each simulation stage. Among others, these tasks include variable initialization, computation of output variables, update of state variables, etc [34].

- Compilation of the S-Function. This is done using the mex utility provided by MATLAB [34]. MEX utility can be run from the MATLAB command prompt window, by typing mex filename.c, where filename.c can be either a single C-coded S-function file or a combination of different source C files.11 The resulting object files are dynamically compiled and linked in SIMULINK when needed in a given simulation.

- Incorporation of the Model into the SIMULINK Environment. This can be done using the S-function block of the SIMULINK libraries [34]. A block diagram containing the S-function block is created including the input/output pins. The dialogue box is used for specifying the name of the underlying S-function. In addition, model parameters are also included in this box which can be used for modifying the parameter values.

As an example, Figure 3.15b illustrates how to apply the main steps listed to create the S-function of an SC FE integrator with finite and nonlinear DC gain such as that shown in Figure 3.8. Note that the computational model flow graph in Figure 3.15b shows only the iterative procedure used for computing the nonlinear DC gain, whose entire MATLAB code is listed in Figure 3.10. When more nonidealities are to be considered, a more complex computation model—that appropriately takes all nonidealities into account in the right sequence—is needed, as will be detailed in next sections. For the sake of simplicity, the example in Figure 3.15b only shows some significant sections of the S-function file associated with the SC integrator model and how this S-function is incorporated into the SIMULINK environment.

Figure 3.15 Procedure to incorporate a behavioral model into the MATLAB/SIMULINK environment using C-MEX S-functions: (a) conceptual step-by-step flow and (b) illustration of the process for an SC FE integrator with finite nonlinear DC gain.

Figure 3.16 shows the entire C-coded S-function file of an SC integrator with finite nonlinear DC gain, highlighting its main parts. Note that, in addition to the computational model itself (shown in Figure 3.17), an S-function includes other important functions that are required to simulate the behavioral model using SIMULINK. The majority of these functions and routines are included in the S-function template files provided by MATLAB. Therefore, the easiest way to model ![]() M building blocks is to modify those template files by including the corresponding model parameters, state variables, input/output signals, clock-phase diagram scheme, etc.12 MATLAB provides detailed documentation and a number of examples which are very useful to do this task [34].

M building blocks is to modify those template files by including the corresponding model parameters, state variables, input/output signals, clock-phase diagram scheme, etc.12 MATLAB provides detailed documentation and a number of examples which are very useful to do this task [34].

Figure 3.16 MATLAB C-coded S-function file of the integrator in Figure 3.10.

Figure 3.17 C-code included in the mdlOutputs section of the S-function file in Figure 3.16.

For instance, the S-function file shown in Figure 3.16 is made up of the following parts and functions:

- S-function name and definitions. This section of the S-function is used to define the name of the block model and its corresponding parameters. In the example of Figure 3.16, the model parameters are phi, ts, c1, c2, av, avnl, cp, opspos, and opsneg, the latter being the positive and negative limits of the amplifier output swing.

- mdlInitializeSizes, where the number of inputs, outputs, and internal states are specified. Note that building blocks used in SIMULINK may have a vector of inputs, a vector of outputs, and a vector of states. The dimensions of these vectors are also specified in this part of the S-function. In this example, two input ports, zero state variables, and one output are defined, the size of all of them being one. The number of sampling rates (or sampling times)—one in this case—is also specified in the mdlInitializeSizes function.

- mdlInitializeSampleTimes, where the sampling time and the clock-phase scheme is defined. This function is used to define the building block at single-rate, at multirate, or if it is a CT circuit. The number of clock phases, the on-time period of each of them as well as the delays—called offset

in the S-function—among them are also specified in this routine. For instance, in this example, a nonoverlapping two-phase clock with a 50

duty cycle is considered.

duty cycle is considered. - mdlStart. This routine performs the initialization of the S-function, setting up the required model parameters and the initial values of the internal variable states.

- mdlOutputs. This is the main part of the S-function because the C-code of the behavioral model is introduced in this section. The routine computes the model and stores the corresponding results in an output array.

- mdlTerminate is a routine that must be included in the S-function file in order to keep the required template structure because SIMULINK calls it at the end of the simulation. In the more general case, this function is used for performing any action required at the end of the simulation, such as freeing memory. In this example, this function is not used and hence it is empty.

As stated previously, once the C-coded S-function source file (intfesc1branchavnl.c) has been generated, it must be compiled to make it executable in MATLAB. In this example, the compilation is done by running the following sentence mex intfesc1branchavnl.c in the MATLAB command window. As a result, a compiled file—named MEX file—is generated. Indeed, the term MEX comes from MATLAB EXecutable [28].

The compiled MEX S-function is incorporated into a SIMULINK model using the S-function block available in the User-Defined Functions SIMULINK library. Figure 3.18 illustrates the SIMULINK block associated with the S-function of Figure 3.16 showing the main dialogue windows. The S-function name and the model parameters are entered into the Block Parameter dialogue box. It is very important that the block name, as well as the model parameters, are the same as those included in the source file of Figure 3.16. The input/output terminal ports are connected to the S-function block in the SIMULINK block diagram.

Figure 3.18 Illustrating the implementation of the S-function of Figure 3.16 in SIMULINK.

Note that an additional S-function block named FeIntSampling is included in the block diagram of Figure 3.18. This block—whose C-coded S-function source file is shown in Figure 3.16—is used for properly sampling the integrator output at the correct time instant. This additional S-function is combined with a Half Delay SIMULINK block to have a more precise control of the clock phase at which the integrator output is taken and to collect only one output sample per clock period.

In order to make the use of S-functions easy to use in more complex systems, a block mask can be created. A specific mask icon can be used instead of the SIMULINK subsystem's standard icon. This is very useful to identify different building blocks in a given system such as a ![]() M and this will be shown in the next sections. The mask also has a dialogue box where the designer can change the model parameters in a simple way. These model parameters are passed to the S-function and dynamically linked into SIMULINK when they are needed during a simulation.

M and this will be shown in the next sections. The mask also has a dialogue box where the designer can change the model parameters in a simple way. These model parameters are passed to the S-function and dynamically linked into SIMULINK when they are needed during a simulation.

The procedure described in this section must be followed in order to create the behavioral models of the different ![]() M building blocks. Next section explains in detail some of the most important building-block models, as well as their implementation in the MATLAB/SIMULINK environment using C-coded S-functions.

M building blocks. Next section explains in detail some of the most important building-block models, as well as their implementation in the MATLAB/SIMULINK environment using C-coded S-functions.

3.4 Efficient Behavioral Modeling of  M Building Blocks using C-MEX S-Functions

M Building Blocks using C-MEX S-Functions

All ![]() M building blocks can be modeled by C-MEX S-functions using the methodology described in the previous section. This way, any

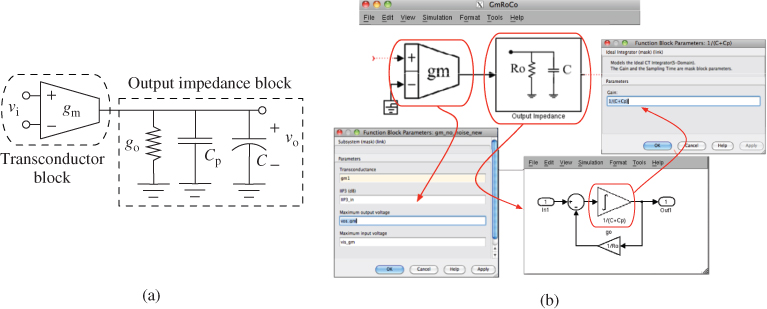

M building blocks can be modeled by C-MEX S-functions using the methodology described in the previous section. This way, any ![]() M architecture can be simulated at system level in an efficient way in terms of accuracy and CPU time. As an illustration, Figure 3.19 shows the SIMULINK block diagram of a second-order

M architecture can be simulated at system level in an efficient way in terms of accuracy and CPU time. As an illustration, Figure 3.19 shows the SIMULINK block diagram of a second-order ![]() M implemented using SC integrators (Figure 3.19a) and Gm-C integrators (Figure 3.19b). These block diagrams contain S-function blocks that model integrators, quantizers, and feedback DACs. Other auxiliary subcircuits, such as the output impedances of the Gm-C integrators (made up of

M implemented using SC integrators (Figure 3.19a) and Gm-C integrators (Figure 3.19b). These block diagrams contain S-function blocks that model integrators, quantizers, and feedback DACs. Other auxiliary subcircuits, such as the output impedances of the Gm-C integrators (made up of ![]() and

and ![]() ) and the digital latches are also included in the models.

) and the digital latches are also included in the models.

Figure 3.19 Illustrating the behavioral model of a second-order ![]() M using S-functions: (a) SC implementation and (b) Gm-C implementation.

M using S-functions: (a) SC implementation and (b) Gm-C implementation.

Each block in Figure 3.19 can be implemented using different circuit topologies which are affected by a number of circuit error mechanisms. A detailed explanation of all different ![]() M building-block behavioral models and their corresponding S-functions is beyond the scope of this book. Instead, this section describes the model of the most essential elements of

M building-block behavioral models and their corresponding S-functions is beyond the scope of this book. Instead, this section describes the model of the most essential elements of ![]() Ms—that is, integrators, quantizers, and DACs—taking into account the most important nonideal effects discussed in Chapter 2 and specially emphasizing on those aspects related to their implementation using C-MEX S-functions.

Ms—that is, integrators, quantizers, and DACs—taking into account the most important nonideal effects discussed in Chapter 2 and specially emphasizing on those aspects related to their implementation using C-MEX S-functions.

3.4.1 Modeling of SC Integrators using S-Functions

Let us consider again the conceptual schematic of an SC FE integrator shown in Figure 3.8a. Note that a single-ended schematic is shown for the sake of simplicity. However, the behavioral model described below takes into account a fully-differential topology.

Its ideal behavior is described by the finite-difference equation given in Equation 3.1. The impact of finite OTA DC gain was considered in Section 3.3, taking into account both linear and nonlinear effects. However, in practice, the performance of SC integrators is degraded by a number of error mechanisms, as described in Chapter 2. An accurate behavioral model must take into account the contribution of the main circuit errors, as well as the clock phases in which they affect the performance of the circuit to be modeled—an SC FE integrator in this case. To this purpose, the effect of all SC circuit nonidealities is computed by following the iterative procedure shown in the flow graph of Figure 3.20 [5].

Figure 3.20 Flowchart of the SC FE integrator computational model.

The model starts by loading the values of the required model parameters, the input signal, and the initial conditions—that is, the voltages at internal nodes of the integrator (including the values stored on the sampling and integration capacitor) stored in the previous clock period and which are usually set to zero at the beginning of a simulation. Before starting to compute the behavioral model, some initial calculations are done, namely, the equivalent input-referred noise, the actual value of the integrators weight due to capacitor mismatch, and the parasitic and load capacitances at different nodes of the integrator during sampling and integration clock phases.

The different integrator clock phases that correspond to the two main branches in Figure 3.20 are selected according to the value of the clock-phase counter count and the input switch phase—either ![]() or

or ![]() , as illustrated in Figure 3.11. At each clock phase, the effect of main SC circuit nonidealities is taken into account, namely, finite (linear and nonlinear) switch on-resistance, capacitor nonlinearity, thermal noise, incomplete settling, finite (linear and nonlinear) OTA DC gain (modeled as described in Section 3.3), and output swing limitation. The behavioral model of these errors is based on the nonideal equations explained in Chapter 2. These equations can be codified in C and incorporated in an S-function as illustrated in Figures 3.23.

, as illustrated in Figure 3.11. At each clock phase, the effect of main SC circuit nonidealities is taken into account, namely, finite (linear and nonlinear) switch on-resistance, capacitor nonlinearity, thermal noise, incomplete settling, finite (linear and nonlinear) OTA DC gain (modeled as described in Section 3.3), and output swing limitation. The behavioral model of these errors is based on the nonideal equations explained in Chapter 2. These equations can be codified in C and incorporated in an S-function as illustrated in Figures 3.23.

Figure 3.21 Excerpt of the MATLAB C-coded S-function file of an SC FE integrator considering all circuit errors: model parameters, definition of clock-phase timing, and calculation of integrator weight including mismatch (Part 1 of 3).

Figure 3.22 Excerpt of MATLAB C-coded S-function file of an SC FE integrator considering all circuit errors: calculation of equivalent load capacitances, input-referred thermal noise, capacitor nonlinearity, incomplete settling during sampling phase, nonlinear finite opamp DC gain, and output swing (Part 2 of 3).

Figure 3.23 Excerpt of MATLAB C-coded S-function file of an SC FE integrator considering all circuit errors: calculation of incomplete settling during integration phase, capacitor nonlinearity, nonlinear finite opamp DC gain, and output swing (Part 3 of 3).

Note that the S-function file follows the same structure as that shown in Figure 3.16, but adding more detailed pieces of information to incorporate the mentioned circuit errors into the behavioral model. For the sake of simplicity, Figures 3.23 show only the most important parts of the S-function file. Although additional comments have been included in the C-code, the following sections explain the main parts of the S-function by linking the C-code with the design equations described in Chapter 2 for the different SC circuit nonidealities.

Capacitor Mismatch and Nonlinearity

As discussed in Section 2.3, capacitor mismatch is modeled as a random deviation of the integrators weight from its nominal value ![]() . This random variation is included in the C-code [35] as a normal (or Gaussian) distribution with a mean value of

. This random variation is included in the C-code [35] as a normal (or Gaussian) distribution with a mean value of ![]() (denoted as MEAN in Figure 3.21) and a variance that is provided as a model parameter named VARIANCE.

(denoted as MEAN in Figure 3.21) and a variance that is provided as a model parameter named VARIANCE.

Another nonideal effect associated with the integrator capacitors is the nonlinear dependence of their capacitance on the voltage drop across them (![]() ), which is modeled as a polynomial function given by

), which is modeled as a polynomial function given by

3.12 ![]()

where ![]() are the nominal values of the sampling (

are the nominal values of the sampling (![]() ) or the integration capacitors (

) or the integration capacitors (![]() ) and

) and ![]() are, respectively, the first- and second-order nonlinear voltage coefficients represented in the model by CNL1,2 (Figure 3.22). This way, the charge stored in these capacitors is given by [36]

are, respectively, the first- and second-order nonlinear voltage coefficients represented in the model by CNL1,2 (Figure 3.22). This way, the charge stored in these capacitors is given by [36]

3.13

Note that the resulting expression can be viewed as the charge stored in a nominal linear capacitor ![]() with a voltage across it given by

with a voltage across it given by ![]() .

.

Input-Referred Thermal Noise

The circuit noise model takes into account the thermal noise generated in the switches and the opamp [31]. Flicker (or ![]() ) noise is not considered in the system-level behavioral model because it is assumed that it will be canceled out by a proper electrical design at transistor level. Other noise sources contributions, such as thermal and flicker noise sources associated with the

) noise is not considered in the system-level behavioral model because it is assumed that it will be canceled out by a proper electrical design at transistor level. Other noise sources contributions, such as thermal and flicker noise sources associated with the ![]() M reference voltages, are usually considered during the electrical (transistor-level) design. This way, based on the analysis described in Section 2.5, the rms value of the input-referred thermal noise included in the model (VNOISE in Figure 3.22) is approximated by

M reference voltages, are usually considered during the electrical (transistor-level) design. This way, based on the analysis described in Section 2.5, the rms value of the input-referred thermal noise included in the model (VNOISE in Figure 3.22) is approximated by

where UNOISE is a random number in the range of ![]() generated by the Uniform Random Number building block available in SIMULINK,

generated by the Uniform Random Number building block available in SIMULINK, ![]() represents the PSD of the thermal noise generated by the opamp, and

represents the PSD of the thermal noise generated by the opamp, and ![]() stands for the PSD of the thermal noise generated in the switches during clock phases

stands for the PSD of the thermal noise generated in the switches during clock phases ![]() . These PSD functions, respectively, denoted as SIN_OP, SIN_PHI1, SIN_PHI2 in the C-code of Figure 3.22 are calculated as a function of different electrical parameters involved in the thermal noise model analyzed in Section 2.5. These parameters include, among others, the switch on-resistance

. These PSD functions, respectively, denoted as SIN_OP, SIN_PHI1, SIN_PHI2 in the C-code of Figure 3.22 are calculated as a function of different electrical parameters involved in the thermal noise model analyzed in Section 2.5. These parameters include, among others, the switch on-resistance ![]() (denoted as RON in the C-code of Fig. 3.22), the equivalent noise bandwidth of noise sources associated with the switches during clock phase

(denoted as RON in the C-code of Fig. 3.22), the equivalent noise bandwidth of noise sources associated with the switches during clock phase ![]() (denoted as BWn_SPHI2 in Figure 3.22), and the equivalent bandwidth of the amplifier thermal noise (BWn_OP in Figure 3.22). Note that if ideal switches are assumed—that is,

(denoted as BWn_SPHI2 in Figure 3.22), and the equivalent bandwidth of the amplifier thermal noise (BWn_OP in Figure 3.22). Note that if ideal switches are assumed—that is, ![]() —only the amplifier contributes to the thermal noise model.

—only the amplifier contributes to the thermal noise model.

Switch On-Resistance Dynamics

The effect of finite switch on-resistance ![]() is considered in both clock phases. For instance, as shown in the C-code of Figures 3.23, the value of the voltage sampled on

is considered in both clock phases. For instance, as shown in the C-code of Figures 3.23, the value of the voltage sampled on ![]() taking into account the effect of capacitor nonlinearity, thermal noise, and the linear sampling process due to

taking into account the effect of capacitor nonlinearity, thermal noise, and the linear sampling process due to ![]() is given by

is given by

3.15 ![]()

where ![]() is the value of the input signal at the end of the sampling phase—denoted as U1 in the C-code.

is the value of the input signal at the end of the sampling phase—denoted as U1 in the C-code.

As stated in Section 2.7.2, switches are usually implemented as CMOS transmission gates and the value of ![]() strongly depends on the value of the voltage drop across the nodes of the switch. This nonlinear phenomenon causes harmonic distortion which, as will be shown in Chapter 4, increases with the ratio between the input frequency and the sampling frequency [37], thus being especially critical in broadband applications.

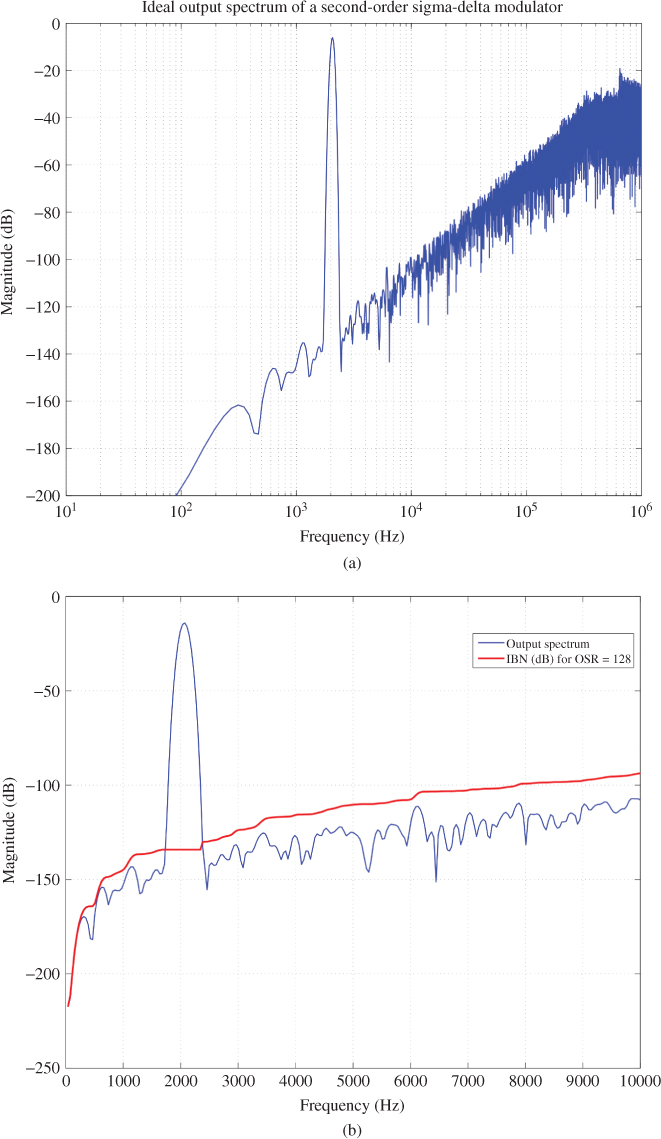

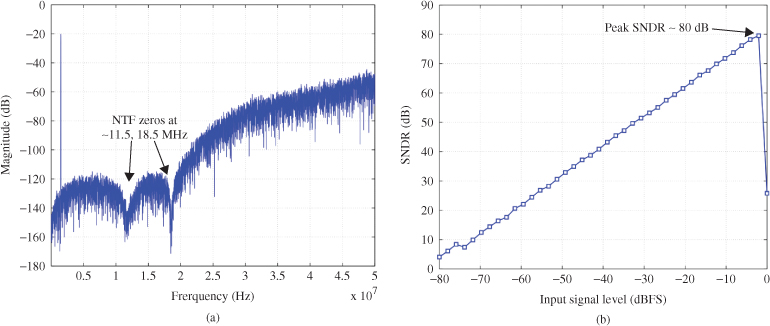

strongly depends on the value of the voltage drop across the nodes of the switch. This nonlinear phenomenon causes harmonic distortion which, as will be shown in Chapter 4, increases with the ratio between the input frequency and the sampling frequency [37], thus being especially critical in broadband applications.