Chapter 2

Circuits and Errors: Systematic Analysis and Practical Design Issues

As discussed in Chapter 1, ADCs based on ![]() modulation offer key advantages for their practical implementation in present-day CMOS processes compared with other data-conversion techniques. Unlike Nyquist-rate converters, which require high precision in their building blocks to achieve overall high accuracy, oversampling and quantization noise shaping allow to trade speed for accuracy. In this way, an operation that can be made relatively insensitive to imperfections on the analog circuit can be obtained at the cost of increased complexity and speed in the associated digital circuitry [1].

modulation offer key advantages for their practical implementation in present-day CMOS processes compared with other data-conversion techniques. Unlike Nyquist-rate converters, which require high precision in their building blocks to achieve overall high accuracy, oversampling and quantization noise shaping allow to trade speed for accuracy. In this way, an operation that can be made relatively insensitive to imperfections on the analog circuit can be obtained at the cost of increased complexity and speed in the associated digital circuitry [1].

The principles of ![]() modulation were presented in the previous chapter and alternative

modulation were presented in the previous chapter and alternative ![]() M topologies (single-loop and cascades) and implementation techniques (DT and CT) were presented. However, the achievable performance of different alternatives was mainly addressed taking only quantization error into account. Besides this error—which is inherent to any analog-to-digital conversion technique—only the effect of DAC errors was considered to compare the performance of single-bit and multibit

M topologies (single-loop and cascades) and implementation techniques (DT and CT) were presented. However, the achievable performance of different alternatives was mainly addressed taking only quantization error into account. Besides this error—which is inherent to any analog-to-digital conversion technique—only the effect of DAC errors was considered to compare the performance of single-bit and multibit ![]() Ms at the architectural level.

Ms at the architectural level.

This chapter analyzes the main nonideal mechanisms affecting the performance of both SC and CT ![]() Ms. Although it is commonly accepted that

Ms. Although it is commonly accepted that ![]() ADCs are less sensitive to nonidealities in the analog circuitry than other conversion techniques, their impact will be larger the more demanding the ADC specifications. Therefore, the influence of these errors on the modulator performance must be carefully considered during early design phases. However, this chapter is not intended to be an exhaustive description of all nonideal effects, but a practical description of the main ones. The aim is to provide sufficient insight on the problem and to present analytical procedures that can be applied to other error mechanisms.

ADCs are less sensitive to nonidealities in the analog circuitry than other conversion techniques, their impact will be larger the more demanding the ADC specifications. Therefore, the influence of these errors on the modulator performance must be carefully considered during early design phases. However, this chapter is not intended to be an exhaustive description of all nonideal effects, but a practical description of the main ones. The aim is to provide sufficient insight on the problem and to present analytical procedures that can be applied to other error mechanisms.

The first part of the chapter is devoted to circuit errors with large influence on the behavior of SC-![]() Ms, such as integrator leakage, capacitor mismatch, settling errors, and

Ms, such as integrator leakage, capacitor mismatch, settling errors, and ![]() noise. The second part of this chapter covers the dominant circuit errors in CT-

noise. The second part of this chapter covers the dominant circuit errors in CT-![]() Ms, especially clock jitter, excess loop delay, and time-constant errors. The main sources of distortion in both types of

Ms, especially clock jitter, excess loop delay, and time-constant errors. The main sources of distortion in both types of ![]() Ms are also discussed. System-level considerations, behavioral models, and closed-form expressions are obtained for the influence of each nonideality. From them, estimable guidelines for the design of

Ms are also discussed. System-level considerations, behavioral models, and closed-form expressions are obtained for the influence of each nonideality. From them, estimable guidelines for the design of ![]() Ms can be extracted. These are put into practice in a case study atthe end of this chapter.

Ms can be extracted. These are put into practice in a case study atthe end of this chapter.

2.1 Nonidealities in Switched-Capacitor  Modulators

Modulators

There are a number of circuit nonidealities and nonlinearities that degrade the performance of the analog modulator blocks. The way in which these nonidealities affect the performance of ![]() Ms depends on many different factors, among others: the nature of the error itself, the influence of the specific circuit, its effect on the modulator noise transfer function, etc.

Ms depends on many different factors, among others: the nature of the error itself, the influence of the specific circuit, its effect on the modulator noise transfer function, etc.

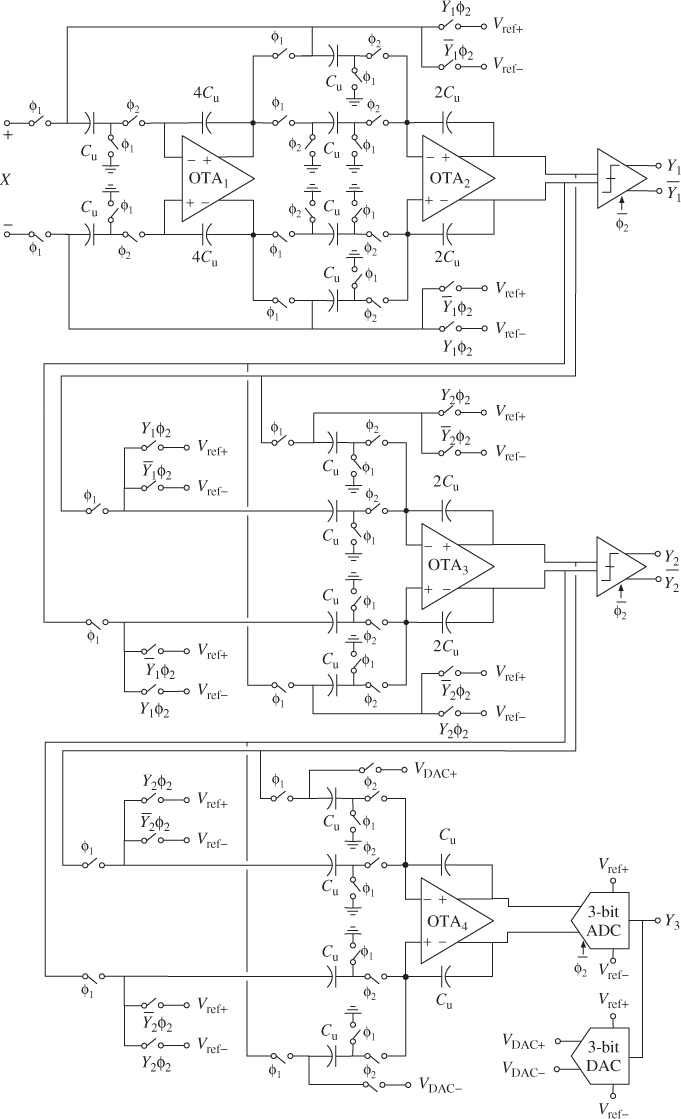

In the case of SC implementations, the main nonideal effects can be grouped as illustrated in Figure 2.1 according to the ![]() M circuit they affect as:

M circuit they affect as:

- Amplifiers: output swing, finite gain, dynamic limitations, and circuit noise.

- Switches: on-resistance, thermal noise, charge injection, and clock feedthrough.

- Capacitors: mismatch and nonlinearity.

- Multibit ADCs and DACs: offset, gain error, and nonlinearity.

- Clock: jitter.

Figure 2.1 Main nonidealities affecting the performance of switched-capacitor ![]() Ms.

Ms.

The influence of nonidealities on the performance of ![]() Ms strongly depends on the location of the corresponding noise source in the modulator. According to these criteria, the above errors can be classified into two main families:

Ms strongly depends on the location of the corresponding noise source in the modulator. According to these criteria, the above errors can be classified into two main families:

- Errors that modify the modulator NTF

such as the finite amplifier gain and gain-bandwidth product and capacitor mismatch. Their effect strongly depends on the modulator topology. For instance, cascade

Ms are more sensitive to capacitor mismatch and finite amplifier gain than single-loop architectures. The same applies for low-pass

Ms are more sensitive to capacitor mismatch and finite amplifier gain than single-loop architectures. The same applies for low-pass  Ms with optimized zeros and band-pass

Ms with optimized zeros and band-pass  Ms with local feedback.

Ms with local feedback. - Errors that can be modeled as additive noise sources at the modulator input and, hence, are not in-band attenuated by the noise shaping. Their effect is thus independent of the modulator topology. Among other, some errors belonging to this family are clock jitter, circuit noise, and distortion caused by circuit nonlinearities.

In the case of those nonideal effects affecting the modulator NTF, the procedure that is commonly used to analyze their impact on the modulator performance is [2, 3]:

- Obtaining an integrator equivalent circuit taking into account the nonideal effect under study.

- Analyzing the impact of the nonideality on the integrator transfer function

, such that

, such that  , with

, with  being the error vector including all nonideal parameters involved in the integrator circuit equivalent obtained in the previous step.

being the error vector including all nonideal parameters involved in the integrator circuit equivalent obtained in the previous step. - To compute the effect of

on a

on a  M, the integrator transfer functions are replaced with

M, the integrator transfer functions are replaced with  and a linear quantizer model is considered to obtain the nonideal

and a linear quantizer model is considered to obtain the nonideal  .

. - The nonideal NTF is integrated within the signal band to obtain the degraded in-band noise power

. Usually, some approximations are required to obtain closed-form expressions for

. Usually, some approximations are required to obtain closed-form expressions for  as a function of

as a function of  .

.

This procedure is applied to low-pass SC-![]() Ms throughout this section, although it can be easily generalized to band-pass SC-

Ms throughout this section, although it can be easily generalized to band-pass SC-![]() Ms—working on the resonator transfer functions

Ms—working on the resonator transfer functions ![]() —and to CT-

—and to CT-![]() Ms as well—working on

Ms as well—working on ![]() -domain.

-domain.

For the sake of exemplification, single-loop ![]() Ms with distributed feedback (see Section 1.4.2) and

Ms with distributed feedback (see Section 1.4.2) and ![]() cascades are considered (see Section 1.5). For these modulator topologies, optimal coefficients for second-, third-, and fourth-order

cascades are considered (see Section 1.5). For these modulator topologies, optimal coefficients for second-, third-, and fourth-order ![]() Ms can be found in [4] for the single-bit case and in [5] for the multibit case.

Ms can be found in [4] for the single-bit case and in [5] for the multibit case.

Wherever behavioral simulation results are presented throughout this section corresponding to single-bit single-loop implementations, the following modulator coefficients have been used for the distributed feedback topologies (Figure 1.18):

for the second-order

for the second-order  M (SL2 for short)

M (SL2 for short) for the third-order

for the third-order  M (SL3 for short)

M (SL3 for short) for the fourth-order

for the fourth-order  M (SL4 for short)

M (SL4 for short)

For single-bit cascade ![]() Ms, their performance is often exemplified throughout this section with behavioral simulation results on a 2-1-1

Ms, their performance is often exemplified throughout this section with behavioral simulation results on a 2-1-1 ![]() M (Figure 1.22), with the following coefficients:

M (Figure 1.22), with the following coefficients:

2.2 Finite Amplifier Gain in SC- Ms

Ms

In Chapter 1, the ideal performance of the different low-pass SC-![]() Ms presented was derived considering the ideal transfer function of an ideal SC FE integrator:

Ms presented was derived considering the ideal transfer function of an ideal SC FE integrator:

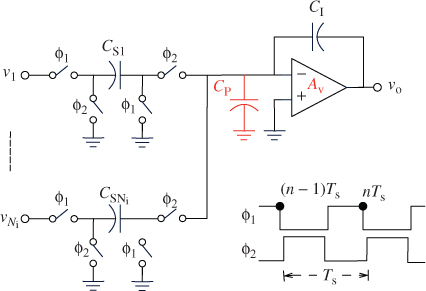

If the finite amplifier gain ![]() and the parasitic capacitor

and the parasitic capacitor ![]() at the amplifier summing node is accounted for in the charge transfer of an SC FE integrator, as shown in Figure 2.2, its difference equation can be written as [3]:

at the amplifier summing node is accounted for in the charge transfer of an SC FE integrator, as shown in Figure 2.2, its difference equation can be written as [3]:

Figure 2.2 SC FE integrator with ![]() input paths and finite amplifier gain

input paths and finite amplifier gain ![]() .

.

Transforming Equation 2.2 to the ![]() -domain and identifying terms as in the following expression,

-domain and identifying terms as in the following expression,

2.3

the transfer function of the integrator when affected by finite amplifier gain—that is, the transfer function of a leaky integrator—yields:

Therefore, when compared with the ideal case in Equation 2.1, amplifier finite gain introduces a gain error in the ITF and a shift of its pole from its ideal position at DC (![]() ). Neglecting the gain error and noting that

). Neglecting the gain error and noting that ![]() , Equation 2.4 can be approximated to a more handy expression as:

, Equation 2.4 can be approximated to a more handy expression as:

2.5

Let us exemplarily consider the effect of the modified ITF on the second-order DT-![]() M in Figure 1.15b. Assuming that

M in Figure 1.15b. Assuming that ![]() for the two integrators in the modulator, the NTF affected by finite amplifier gain can be easily derived [3]. Given that the poles of the ITFs become the zeros of the NTF, both zeros of NTF move away from DC as the amplifier gain decreases. Figure 2.3 depicts the PSD of quantization error that is obtained for several values of

for the two integrators in the modulator, the NTF affected by finite amplifier gain can be easily derived [3]. Given that the poles of the ITFs become the zeros of the NTF, both zeros of NTF move away from DC as the amplifier gain decreases. Figure 2.3 depicts the PSD of quantization error that is obtained for several values of ![]() and illustrates the degradation of the modulator noise shaping. The following approximated expression can be derived for the in-band noise when integrator leakage is accounted for [3]:

and illustrates the degradation of the modulator noise shaping. The following approximated expression can be derived for the in-band noise when integrator leakage is accounted for [3]:

Note that the DC gain of the amplifiers should be in the range of the oversampling ratio (![]() ) in order to keep every term in Equation 2.6 proportional to

) in order to keep every term in Equation 2.6 proportional to ![]() and retain the ideal noise shaping. For usual values of the oversampling ratio and the amplifier DC gain, this equation can be further simplified to:

and retain the ideal noise shaping. For usual values of the oversampling ratio and the amplifier DC gain, this equation can be further simplified to:

Figure 2.3 Degradation of the noise shaping of a second-order SC-![]() M with finite amplifier gain.

M with finite amplifier gain.

A similar procedure can be followed to derive the modified NTF of Lth-order loops affected by integrator leakage and thus calculate the increased in-band noise. For an Lth-order SC-![]() M with distributed feedback, the in-band noise can be obtained as follows [3],

M with distributed feedback, the in-band noise can be obtained as follows [3],

where again the amplifier DC gains must be in the range of the oversampling (![]() ) to keep every term in Equation 2.8 proportional to

) to keep every term in Equation 2.8 proportional to ![]() and retain the ideal Lth-order noise shaping. The expression above can usually be further simplified to [3]:

and retain the ideal Lth-order noise shaping. The expression above can usually be further simplified to [3]:

Integrator leakages can be foreseen to have a stronger impact on cascade ![]() Ms, as the degradation of the ITF filtering leads to a modification of the cascaded loop filters (in the analog side) that is not compensated for by the cancelation logic (DCL in the digital side)—see Figure 1.21. This imbalance will cause quantization errors of all the cascaded stages to appear at the modulator output.

Ms, as the degradation of the ITF filtering leads to a modification of the cascaded loop filters (in the analog side) that is not compensated for by the cancelation logic (DCL in the digital side)—see Figure 1.21. This imbalance will cause quantization errors of all the cascaded stages to appear at the modulator output.

For the particular case of a 2-1-1 DT cascade as that illustrated in Figure 1.22, the IBN when integrator leakage is accounted for can be obtained as [3]:

Note that the amplifier DC gain required to retain the ideal noise shaping increases while moving from the back-end to the front-end stages of the cascade. Therefore, for the third-stage amplifier ![]() is sufficient, but for the second-stage amplifier

is sufficient, but for the second-stage amplifier ![]() and for the first-stage amplifiers

and for the first-stage amplifiers ![]() . Note also that, in case multibit quantization of

. Note also that, in case multibit quantization of ![]() bits is employed in the last stage of the cascade, these requirements further increase by a factor

bits is employed in the last stage of the cascade, these requirements further increase by a factor ![]() .

.

A detailed analysis of the effect of integrator leakage on the IBN of generic cascade SC-![]() Ms can be found in [3], as well as of particular cascade configurations. For an Lth-order N-stage cascade DT-

Ms can be found in [3], as well as of particular cascade configurations. For an Lth-order N-stage cascade DT-![]() M as that illustrated in Figure 1.21, the IBN considering integrator leakages yields [3],

M as that illustrated in Figure 1.21, the IBN considering integrator leakages yields [3],

2.11

where ![]() corresponds to the order of the

corresponds to the order of the ![]() th stage in the cascade and the value of coefficients

th stage in the cascade and the value of coefficients ![]() depends on

depends on ![]() .

.

Figure 2.4 shows the effect of the finite DC gain of amplifiers on single-loop and cascade SC-![]() Ms, exemplarily illustrated for second-, third-, and fourth-order single-loops and for a 2-1-1 cascade. In all cases, the in-band noise is computed from the modulator NTF using the nonapproximated ITF in Equation 2.4, as well as from the approximated closed-form expressions in Equations 2.9 and 2.10. Note that both results are in good accordance. Note also that the larger sensitivity of cascade

Ms, exemplarily illustrated for second-, third-, and fourth-order single-loops and for a 2-1-1 cascade. In all cases, the in-band noise is computed from the modulator NTF using the nonapproximated ITF in Equation 2.4, as well as from the approximated closed-form expressions in Equations 2.9 and 2.10. Note that both results are in good accordance. Note also that the larger sensitivity of cascade ![]() Ms to integrator leakages is evident from Figure 2.4b.

Ms to integrator leakages is evident from Figure 2.4b.

Figure 2.4 Influence of finite amplifier gain on the in-band noise of SC-![]() Ms: (a) second- and third-order loops and (b) 2-1-1 cascade and fourth-order loop. Approximated results have been obtained from Equations 2.9 and 2.10.

Ms: (a) second- and third-order loops and (b) 2-1-1 cascade and fourth-order loop. Approximated results have been obtained from Equations 2.9 and 2.10.

2.3 Capacitor Mismatch in SC- Ms

Ms

As illustrated in Figure 1.17, in SC-![]() Ms integrator gain coefficients

Ms integrator gain coefficients ![]() are implemented as capacitor ratios

are implemented as capacitor ratios ![]() and the implemented values will thus deviate from the nominal ones due to variations in technological process parameters. For the case of a particular gain coefficient

and the implemented values will thus deviate from the nominal ones due to variations in technological process parameters. For the case of a particular gain coefficient ![]() that is implemented as the ratio of

that is implemented as the ratio of ![]() to

to ![]() unit capacitors

unit capacitors ![]() , the actual implemented coefficient

, the actual implemented coefficient ![]() will exhibit an error

will exhibit an error ![]() that can be estimated as [3],

that can be estimated as [3],

where the integrator gain error is estimated in the worst case as three times its relative standard deviation, which can itself be related to the relative standard deviation of the unit capacitor used—or ![]() for short. Note that the estimation for

for short. Note that the estimation for ![]() in Equation 2.12 should be divided by

in Equation 2.12 should be divided by ![]() in fully-differential SC integrators.

in fully-differential SC integrators.

Nowadays, SC-![]() Ms are mostly implemented in mixed-mode technological processes that include precise capacitor primitives, such as MiM or MoM capacitors, with a mismatch typically lower than 0.1%. This means that integrator gain errors in SC-

Ms are mostly implemented in mixed-mode technological processes that include precise capacitor primitives, such as MiM or MoM capacitors, with a mismatch typically lower than 0.1%. This means that integrator gain errors in SC-![]() Ms will normally be lower than 0.3%—or even less in case a large number of unit capacitors and common-centroid layout techniques are used for implementing the coefficients.

Ms will normally be lower than 0.3%—or even less in case a large number of unit capacitors and common-centroid layout techniques are used for implementing the coefficients.

These small deviations of the integrator coefficients due to capacitor mismatch can be foreseen to have little impact on the in-band noise of single-loop ![]() Ms, as the filtering provided by the integrators remains unchanged. Indeed, if integrator gain errors are accounted for, the IBN of an Lth-order SC-

Ms, as the filtering provided by the integrators remains unchanged. Indeed, if integrator gain errors are accounted for, the IBN of an Lth-order SC-![]() M with distributed feedback can be estimated as,

M with distributed feedback can be estimated as,

where ![]() refers to the gain error of the

refers to the gain error of the ![]() th integrator, which can be estimated in the worst case as

th integrator, which can be estimated in the worst case as ![]() . Note from Equation 2.13 that, for the IBN of second-order

. Note from Equation 2.13 that, for the IBN of second-order ![]() M to increase in 3 dB, integrator gain errors should be as large as 20%—too large indeed to be considered as an actual mismatch!

M to increase in 3 dB, integrator gain errors should be as large as 20%—too large indeed to be considered as an actual mismatch!

Conversely, capacitor mismatch has a strong impact on cascade ![]() Ms, as the deviation of the integrator gains is not compensated for by the digital coefficients of the DCL. Therefore, quantization errors of the cascaded stages will leak to the modulator output with low-order shapings, considerably increasing the modulator IBN.

Ms, as the deviation of the integrator gains is not compensated for by the digital coefficients of the DCL. Therefore, quantization errors of the cascaded stages will leak to the modulator output with low-order shapings, considerably increasing the modulator IBN.

For the general case of an Lth-order N-stage cascade SC-![]() M, the IBN if integrator gain errors are taken into account can be approximated to [3],

M, the IBN if integrator gain errors are taken into account can be approximated to [3],

2.14

whereas, for the particular case of a 2-1-1 cascade, the former equation yields [3]:

Note that similarly to what happened in Section 2.2 for the case of amplifier DC gain—the requirements on the integrator gain error for retaining the ideal noise shaping get more stringent as we move from the back-end to the front-end stages. Thus, for the integrator in the second stage of the cascade ![]() is sufficient, but for the first-stage integrators

is sufficient, but for the first-stage integrators ![]() . Note also that, in case multibit quantization of

. Note also that, in case multibit quantization of ![]() bits is employed in the last stage of the cascade, these requirements again increase by a factor

bits is employed in the last stage of the cascade, these requirements again increase by a factor ![]() .

.

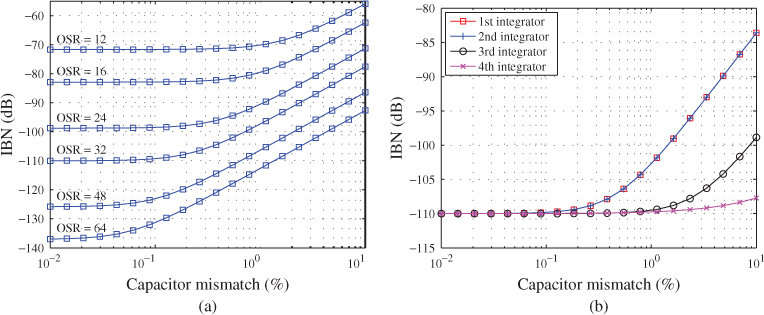

Figure 2.5 illustrates this increasing impact of capacitor mismatch with OSR and with the stage of the cascade being considered. Note that results displayed correspond to worst-case estimations of the IBN based on Equation 2.15 with ![]() . More accurate estimations would require Monte Carlo simulation of the modulator behavioral model considering the particular implementation of each integrator gain coefficient in terms of unit capacitors.

. More accurate estimations would require Monte Carlo simulation of the modulator behavioral model considering the particular implementation of each integrator gain coefficient in terms of unit capacitors.

Figure 2.5 Influence of capacitor mismatch on the in-band noise of a 2-1-1 SC-![]() M: (a) considering the same mismatch error in all integrators and (b) individual impact of the mismatch error in each integrator for OSR = 32. Worst-case estimations of IBN considering

M: (a) considering the same mismatch error in all integrators and (b) individual impact of the mismatch error in each integrator for OSR = 32. Worst-case estimations of IBN considering ![]() in Equation 2.15.

in Equation 2.15.

2.4 Integrator Settling Error in SC- Ms

Ms

Speed limitations in SC integrators due to the limited dynamic response of amplifiers cause errors in the charge transfer. The impact of the resulting error in the integrator output voltage settling error on the modulator performance will be higher, the higher the sampling frequency. As the clock frequency increases in SC-![]() Ms to cope with larger conversion bandwidths, integrator settling error becomes one of the bottlenecks for their practical implementation. On the one hand, the time slot for the integrator operation gets reduced; on the other hand, the amplifier dynamic requirements must be minimized to optimize the modulator power consumption. Therefore, an adequate understanding of the mechanisms degrading the settling of SC integrators and an accurate quantification of the generated errors become mandatory to obtain efficient

Ms to cope with larger conversion bandwidths, integrator settling error becomes one of the bottlenecks for their practical implementation. On the one hand, the time slot for the integrator operation gets reduced; on the other hand, the amplifier dynamic requirements must be minimized to optimize the modulator power consumption. Therefore, an adequate understanding of the mechanisms degrading the settling of SC integrators and an accurate quantification of the generated errors become mandatory to obtain efficient ![]() designs.

designs.

2.4.1 Behavioral Model for the Integrator Settling

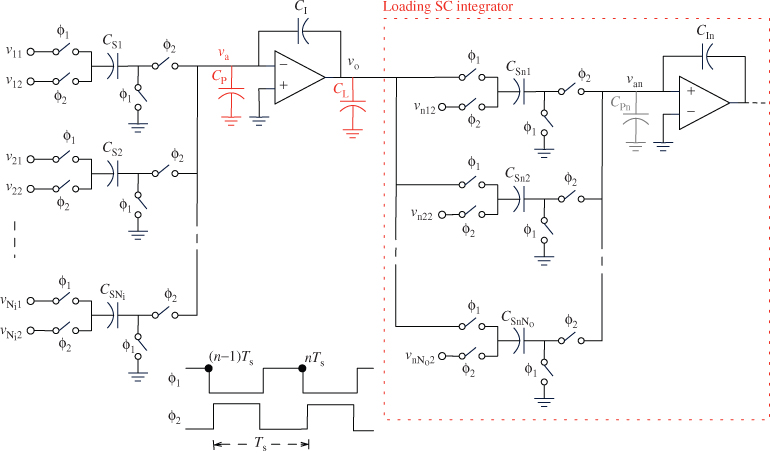

The behavioral model of the transient response for SC FE integrators included in this section is based on the analysis presented in [6]. The model includes the effect of the amplifier dynamic limitations, such as finite gain-bandwidth product (GB) and slew rate (SR), on the charge transfer during both the integration and sampling phases. Also, parasitic capacitors associated with amplifiers and switches, as well as the capacitor load at the integrator output—which changes from integration to sampling—are taken into account. To accurately describe the dynamic performance and determine the integrator output voltage, the equivalent circuit shown in Figure 2.6 is solved in the behavioral model. In the circuit scheme, the SC integrator under study is considered to have ![]() input branches and another SC integrator acting as a load—that is, the No

input branches and another SC integrator acting as a load—that is, the No

input branches of the latter are connected to the output of the former. On the other hand, the amplifier is modeled as shown in Figure 2.7, with a single-pole dynamic (to account for the finite bandwidth) and a nonlinear characteristic with maximum output current ![]() (to account for the limited SR).1

(to account for the limited SR).1

Figure 2.6 SC FE integrator under consideration followed by a loading SC integrator.

Figure 2.7 Amplifier single-pole model with limited output current.

The analysis of this model for the incomplete settling error begins with the computation of the equivalent capacitive load at the amplifier output node during both the sampling (![]() ) and integration (

) and integration (![]() ) phases, respectively given by,

) phases, respectively given by,

where ![]() represents the sampling capacitor of the

represents the sampling capacitor of the ![]() th SC input branch of the integrator under consideration,

th SC input branch of the integrator under consideration, ![]() is the sampling capacitor of the

is the sampling capacitor of the ![]() th SC input branch of the load integrator,

th SC input branch of the load integrator, ![]() is the parasitic capacitor at the summation node of the input SC branches, and

is the parasitic capacitor at the summation node of the input SC branches, and ![]() is the amplifier load capacitor.

is the amplifier load capacitor.

The settling model is analyzed during a complete clock cycle (during both clock phases) considering the different possibilities for the amplifier dynamic operation—that is, linearly or in slew—and keeping track of the voltage at both the integrator output ![]() and the amplifier summation node

and the amplifier summation node ![]() . Therefore, the error in the integrator output voltage at the end of one sampling-integration process can be accurately obtained.

. Therefore, the error in the integrator output voltage at the end of one sampling-integration process can be accurately obtained.

Let ![]() and

and ![]() be the respective amplifier input and output voltages at the end of a preceding integration phase, which will serve as initial conditions to derive of the integrator evolution during a complete clock cycle. The voltage at the amplifier summation node at the end of the next sampling phase—that is, at

be the respective amplifier input and output voltages at the end of a preceding integration phase, which will serve as initial conditions to derive of the integrator evolution during a complete clock cycle. The voltage at the amplifier summation node at the end of the next sampling phase—that is, at ![]() —, can be accurately obtained as [6],

—, can be accurately obtained as [6],

where ![]() is the duration of the SR-limited integrator settling (relative to

is the duration of the SR-limited integrator settling (relative to ![]() ) given by,

) given by,

sgn() is the sign function, and ![]() represents the value of

represents the value of ![]() at the beginning of the sampling phase, which can be computed as,

at the beginning of the sampling phase, which can be computed as,

2.19 ![]()

where ![]() is the voltage across capacitor

is the voltage across capacitor ![]() .2

.2

The integrator output voltage at the end of the sampling phase can be obtained as,

as opposed to the ideal situation in which ![]() .

.

Note from Equations 2.17 and 2.20 that, for the integrator model in Figure 2.6, the amplifier gain-bandwidth product and output SR during sampling are obtained as:

During the integration phase, the incomplete settling model is evaluated proceeding in a similar way as done for the sampling phase. Thus, at the end of the subsequent integration phase—that is, at ![]() —, the value of

—, the value of ![]() is given by [3],

is given by [3],

where ![]() is the duration of the SR-limited integrator settling (relative to

is the duration of the SR-limited integrator settling (relative to ![]() ), given by

), given by

2.23 ![]()

and ![]() represents the value of

represents the value of ![]() at the beginning of the integration phase. The latter can be computed as

at the beginning of the integration phase. The latter can be computed as

2.24

where ![]() are the voltages connected to the input of the

are the voltages connected to the input of the ![]() th SC branch during

th SC branch during ![]() , respectively, and

, respectively, and ![]() represents:

represents:

2.25 ![]()

The integrator output voltage at the end of the integration phase can be obtained as,

as opposed to the ideal integration process with no dynamic limitations, in which the last two terms in Equation 2.26 are null.

The amplifier gain-bandwidth product and output SR during this phase can be obtained similarly as for the sampling phase to be:

Figure 2.8 illustrates how the equations above can be concatenated to accurately keep track of the summation and output voltages of an SC integrator over the clock periods. They can be easily incorporated into CAD tools for the behavioral simulation of SC-![]() Ms—or SC circuits in general. Moreover, the previous model can be easily extrapolated to other operating conditions: integration and sampling phases with different durations, different switching loading conditions at the integrator output, to include the parasitic capacitance of the switches, etc.

Ms—or SC circuits in general. Moreover, the previous model can be easily extrapolated to other operating conditions: integration and sampling phases with different durations, different switching loading conditions at the integrator output, to include the parasitic capacitance of the switches, etc.

Figure 2.8 Illustration of the influence of switching load conditions on the transient response of an SC integrator: (a) loading SC branches are not considered and (b) one loading SC branch with a 0.5-pF capacitor is considered. (Vertical dashed lines indicate time positions ![]() where the integrator ends an SR-limited response and starts evolving linearly). Parameters used are (Figures 2.6 and 2.7):

where the integrator ends an SR-limited response and starts evolving linearly). Parameters used are (Figures 2.6 and 2.7): ![]() ,

, ![]() ,

, ![]() ,

, ![]() ,

, ![]() ,

, ![]() ,

, ![]() , and

, and ![]() for the SC integrator under consideration,

for the SC integrator under consideration, ![]() and

and ![]() for the loading SC integrator, and

for the loading SC integrator, and ![]() .

.

2.4.2 Linear Effect of Finite Amplifier Gain-Bandwidth Product

The model for the transient response of SC integrators described earlier can be easily incorporated into behavioral simulators for SC-![]() Ms to accurately quantify the influence of settling errors on the modulator performance—in terms of both the increased in-band noise and the generated distortion. Besides this behavioral model, it is often useful to work at the early design stages (high-level design) with closed-form expressions which, although being coarse approximations of the behavioral model, can help to gain insight of the influence of settling parameters on different modulator topologies. For this purpose, a linear transient response will be assumed for SC integrators in this section, as if settling error was determined only by the finite amplifier GB with no limitation on the SR.

Ms to accurately quantify the influence of settling errors on the modulator performance—in terms of both the increased in-band noise and the generated distortion. Besides this behavioral model, it is often useful to work at the early design stages (high-level design) with closed-form expressions which, although being coarse approximations of the behavioral model, can help to gain insight of the influence of settling parameters on different modulator topologies. For this purpose, a linear transient response will be assumed for SC integrators in this section, as if settling error was determined only by the finite amplifier GB with no limitation on the SR.

With these considerations in mind, the finite difference equation of an SC FE integrator can be obtained from Equations 2.17, 2.20, 2.22, and 2.26 to be,

where only one input branch is considered for simplicity. The settling error associated with the linearly limited transient response is represented by ![]() , which thus contains terms in

, which thus contains terms in ![]() and in

and in ![]() —with GB in rad s

—with GB in rad s![]() . If settling errors associated with integration dominate on the overall defective settling over those originated during sampling, the linear settling error can be simply reduced to:

. If settling errors associated with integration dominate on the overall defective settling over those originated during sampling, the linear settling error can be simply reduced to:

2.29 ![]()

Transforming Equation 2.28 to the ![]() -domain, the integrator output results in,

-domain, the integrator output results in,

2.30 ![]()

so that, under the assumptions earlier, settling error translates into a gain error in the ideal ITF, whose effect on the IBN of SC-![]() Ms can be computed in a similar way as formerly done for capacitor mismatch in Section 2.3. Therefore, Equations 2.13–2.14 still hold for quantifying the effect of linear defective settling to first order, just by replacing

Ms can be computed in a similar way as formerly done for capacitor mismatch in Section 2.3. Therefore, Equations 2.13–2.14 still hold for quantifying the effect of linear defective settling to first order, just by replacing ![]() with

with ![]() .

.

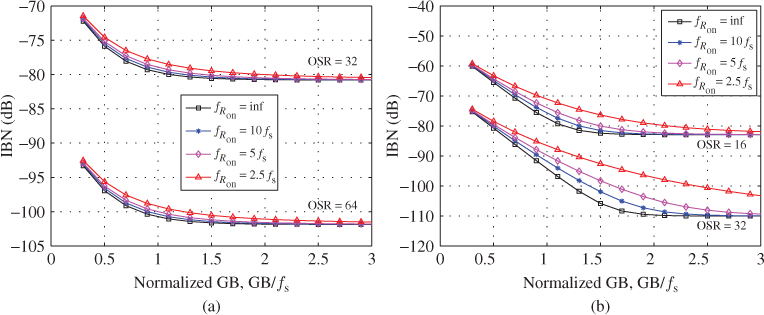

Figure 2.9 illustrates the effect of the finite amplifier GB on single-loop and cascade SC-![]() Ms. The in-band noise of second- and third-order single loops and of a 2-1-1 cascade is computed considering both the behavioral model for the integrator settling in Section 2.4.1 and the approximated closed-form expressions of the generated gain error. Large amplifier output currents have been used in behavioral simulations to make the influence of SR limitation negligible and thus consider linear errors only. Note that, as expected, cascades

Ms. The in-band noise of second- and third-order single loops and of a 2-1-1 cascade is computed considering both the behavioral model for the integrator settling in Section 2.4.1 and the approximated closed-form expressions of the generated gain error. Large amplifier output currents have been used in behavioral simulations to make the influence of SR limitation negligible and thus consider linear errors only. Note that, as expected, cascades ![]() Ms are more sensitive to GB limitations that single loops. Usually, an amplifier GB of 1–2

Ms are more sensitive to GB limitations that single loops. Usually, an amplifier GB of 1–2![]() is sufficient for single-loop modulators to achieve full performance, whereas the requirement increases to 3–10

is sufficient for single-loop modulators to achieve full performance, whereas the requirement increases to 3–10![]() for cascade

for cascade ![]() Ms as the oversampling ratio increases.

Ms as the oversampling ratio increases.

Figure 2.9 Simulation results for the influence of amplifier GB on the in-band noise of SC-![]() Ms: (a) second- and third-order loops and (b) 2-1-1 cascade. Approximated results have been obtained from Equations 2.13 and 2.15 with

Ms: (a) second- and third-order loops and (b) 2-1-1 cascade. Approximated results have been obtained from Equations 2.13 and 2.15 with ![]() .

.

2.4.3 Nonlinear Effect of Finite Amplifier Slew Rate

Contrary to errors arising from finite amplifier GB, finite amplifier SR caused by limited output current capability has a purely nonlinear effect on the performance of ![]() Ms, generating distortion and an increase in the noise floor.

Ms, generating distortion and an increase in the noise floor.

For the case of single-loop SC-![]() Ms, SR-limited integrator dynamics basically translate into distortion. Figure 2.10 illustrates the impact of amplifier SR on a single-bit third-order

Ms, SR-limited integrator dynamics basically translate into distortion. Figure 2.10 illustrates the impact of amplifier SR on a single-bit third-order ![]() M operating with an oversampling ratio of 64. An input tone with

M operating with an oversampling ratio of 64. An input tone with ![]() (

(![]() amplitude) and frequency equal to

amplitude) and frequency equal to ![]() is applied to the modulator in behavioral simulations. Note from the presented results that, depending on the amplifier GB, an SR of 4–8

is applied to the modulator in behavioral simulations. Note from the presented results that, depending on the amplifier GB, an SR of 4–8![]() is enough to reduce the power of generated distortion to a level that does not affect IBN.

is enough to reduce the power of generated distortion to a level that does not affect IBN.

Figure 2.10 Simulation results for a third-order SC-![]() M with

M with ![]() under the influence of finite amplifier slew rate: (a) effect on the in-band noise and (b) effect on the output spectrum for

under the influence of finite amplifier slew rate: (a) effect on the in-band noise and (b) effect on the output spectrum for ![]() . Input signal with

. Input signal with ![]() and

and ![]() . Generated distortion is included in the IBN computation.

. Generated distortion is included in the IBN computation.

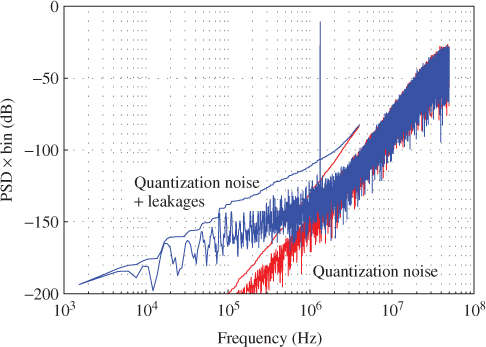

For the case of cascade SC-![]() Ms, finite amplifier SR generates distortion as well as an increase in the noise floor due to noise leakages, as shown in Figure 2.11. For that reason, SR requirements are larger than for single loops and usually range from 4 to

Ms, finite amplifier SR generates distortion as well as an increase in the noise floor due to noise leakages, as shown in Figure 2.11. For that reason, SR requirements are larger than for single loops and usually range from 4 to ![]() depending on the amplifier GB—the larger the GB, the lower the required SR.

depending on the amplifier GB—the larger the GB, the lower the required SR.

Figure 2.11 Simulation results for a 2-1-1 SC-![]() M with

M with ![]() under the influence of finite amplifier slew rate: (a) effect on the in-band noise and (b) effect on the output spectrum for

under the influence of finite amplifier slew rate: (a) effect on the in-band noise and (b) effect on the output spectrum for ![]() . Input signal with

. Input signal with ![]() and

and ![]() . Generated distortion is included in the IBN computation.

. Generated distortion is included in the IBN computation.

Finally, note that the SR-limited integrator dynamic is a nonlinear signal-dependent phenomenon whose occurrence frequency during the modulator operation is directly determined by the signal level at the integrators inputs. Therefore, the ultimate way to reduce SR requirements on an SC-![]() M is to resort to multibit internal quantization.

M is to resort to multibit internal quantization.

2.4.4 Effect of Finite Switch On-Resistance

Switches in the SC branches of ![]() Ms are implemented with MOSFETs—using either single nMOS or pMOS transistors, or CMOS transmission gates—that operate in the triode region when on and thus exhibit in practice a nonzero on-resistance.

Ms are implemented with MOSFETs—using either single nMOS or pMOS transistors, or CMOS transmission gates—that operate in the triode region when on and thus exhibit in practice a nonzero on-resistance.

If the on-resistance of the switches is the only nonideality accounted for in the operation of an SC integrator, it clearly leads to an incomplete charge transfer due to the ![]() time constant that is created in the SC branch. Considering for instance the scheme in Figure 2.12, the integrator output voltage can be obtained as [3],

time constant that is created in the SC branch. Considering for instance the scheme in Figure 2.12, the integrator output voltage can be obtained as [3],

Figure 2.12 SC FE integrator with a single input branch.

2.31

where ![]() represents the charging error in

represents the charging error in ![]() during

during ![]() related to the on-resistance of switches

related to the on-resistance of switches ![]() and

and ![]() and

and ![]() represents the error in the charge transfer from

represents the error in the charge transfer from ![]() to

to ![]() during

during ![]() related to the on-resistance of switches

related to the on-resistance of switches ![]() and

and ![]() . If

. If ![]() is the on-resistance of a single switch, assuming that all switches are of the same size and that both clock phases have the same duration leads to:

is the on-resistance of a single switch, assuming that all switches are of the same size and that both clock phases have the same duration leads to:

2.32 ![]()

Therefore, charge transfer error due to the on-resistance of the switches translates into a gain error in the ideal ITF, whose effect on the IBN of SC-![]() Ms can be computed in a similar way as formerly done in Sections 2.3 or 2.4.2. Therefore, finite switch on-resistance will have considerably lower impact on

Ms can be computed in a similar way as formerly done in Sections 2.3 or 2.4.2. Therefore, finite switch on-resistance will have considerably lower impact on ![]() single loops than on cascades.

single loops than on cascades.

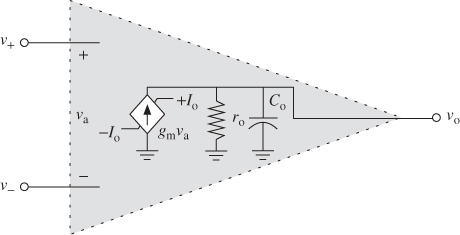

Besides the former discussion on how the switch on-resistance, as a stand-alone nonideality, affects an SC integrator, its effect is better accounted for in practice in combination with the limited amplifier dynamics. Figure 2.13 shows electrical simulation results to illustrate the influence of ![]() on the transient response of the same SC integrator formerly considered in Figure 2.8. Only one clock cycle is shown here to gain in visibility of the

on the transient response of the same SC integrator formerly considered in Figure 2.8. Only one clock cycle is shown here to gain in visibility of the ![]() effect. Note that the linear amplifier response is slowed down as the on-resistance increases, affecting the integrator settling during both the sampling and the integration phase. To incorporate this effect into behavioral simulations, the effective amplifier GB during both clock phases can be approximated to [3],

effect. Note that the linear amplifier response is slowed down as the on-resistance increases, affecting the integrator settling during both the sampling and the integration phase. To incorporate this effect into behavioral simulations, the effective amplifier GB during both clock phases can be approximated to [3],

2.33

where ![]() and

and ![]() represent the

represent the ![]() poles introduced by loading SC branch and by the input SC branch, respectively, and

poles introduced by loading SC branch and by the input SC branch, respectively, and ![]() and

and ![]() are respectively given by Equations 2.21 and 2.27.

are respectively given by Equations 2.21 and 2.27.

Figure 2.13 Illustration of the influence of the switch on-resistance on the transient response of an SC integrator with a loading SC branch. Simulation parameters used are same as those for Figure 2.8 for comparison purposes.

In addition, results presented in Section 2.4.2 for the linear effect of finite amplifier GB on the IBN of SC-![]() Ms can be easily refined to include the slow-down effect of the switches

Ms can be easily refined to include the slow-down effect of the switches ![]() . To that purpose, the following gain error

. To that purpose, the following gain error

2.34 ![]()

can be considered in Equations 2.13 and 2.14. Figure 2.14 illustrates the combined linear effect of the finite amplifier GB and finite switch on-resistance on a third-order single loop and on a 2-1-1 cascade SC-![]() M. The lower sensitivity of single loops to these errors is clear and a switch on-resistance such that

M. The lower sensitivity of single loops to these errors is clear and a switch on-resistance such that ![]() is 4–5

is 4–5![]() is sufficient, in combination with the limited amplifier GB, to achieve full performance. This requirement for the

is sufficient, in combination with the limited amplifier GB, to achieve full performance. This requirement for the ![]() usually increases to 10–20

usually increases to 10–20![]() for cascade

for cascade ![]() Ms as the oversampling increases.

Ms as the oversampling increases.

Figure 2.14 Influence of switch on-resistance on the in-band noise of SC-![]() Ms: (a) third-order loop and (b) 2-1-1 cascade. Approximated results have been obtained from Equations 2.13 and 2.15 with

Ms: (a) third-order loop and (b) 2-1-1 cascade. Approximated results have been obtained from Equations 2.13 and 2.15 with ![]() .

.

2.5 Circuit Noise in SC- Ms

Ms

Electronic noise generated in transistors and resistors is present in any circuit implementation and imposes an ultimate limit to the resolution of ADCs. However, its impact is more severe in DT-![]() Ms that employ SC-techniques due to the white spectrum of the main circuit noise sources. In an SC-

Ms that employ SC-techniques due to the white spectrum of the main circuit noise sources. In an SC-![]() M, these broadband noise components are sampled together with the input signal at the clock frequency, so that they fold over the modulator passband and may cause a considerable increase of the modulator in-band noise due to aliasing.

M, these broadband noise components are sampled together with the input signal at the clock frequency, so that they fold over the modulator passband and may cause a considerable increase of the modulator in-band noise due to aliasing.

As stated in Section 2.1, the influence of nonidealities on the IBN of ![]() Ms is mainly determined by the location of the corresponding noise source in the modulator. With respect to circuit noise, all SC integrators in a

Ms is mainly determined by the location of the corresponding noise source in the modulator. With respect to circuit noise, all SC integrators in a ![]() M add noise in the modulator passband, but the role of the front-end integrator is indeed dominant. When referred to the modulator input, noise power contributed by the remaining integrators is divided by the gain of preceding integrators within the modulator passband, so their influence strongly diminishes while moving from front-end to back-end integrators. Conversely, no shaping takes place at the modulator input and the first integrator has thus to fulfill the noise and linearity requirements of the complete

M add noise in the modulator passband, but the role of the front-end integrator is indeed dominant. When referred to the modulator input, noise power contributed by the remaining integrators is divided by the gain of preceding integrators within the modulator passband, so their influence strongly diminishes while moving from front-end to back-end integrators. Conversely, no shaping takes place at the modulator input and the first integrator has thus to fulfill the noise and linearity requirements of the complete ![]() M.

M.

Let us consider the SC integrator in Figure 2.15a to be the front-end integrator of an SC-![]() M. Two input SC branches are considered: the one including capacitor

M. Two input SC branches are considered: the one including capacitor ![]() is assumed to sample the modulator input signal (

is assumed to sample the modulator input signal (![]() ), whereas the one including capacitor

), whereas the one including capacitor ![]() samples the DAC feedback signal (

samples the DAC feedback signal (![]() ). The main sources of circuit noise in SC integrators have been incorporated into the equivalent models in Figures 2.15b and 2.15c during each of the clock phases, namely, thermal noise generated in the switches and noise generated in the amplifier—both thermal and flicker components to be considered.3

). The main sources of circuit noise in SC integrators have been incorporated into the equivalent models in Figures 2.15b and 2.15c during each of the clock phases, namely, thermal noise generated in the switches and noise generated in the amplifier—both thermal and flicker components to be considered.3

Figure 2.15 Circuit noise analysis in an SC integrator: (a) SC FE integrator with two input paths (single-ended version), (b) equivalent circuit model for sampling, with noise sources due to switches active during ![]() and (c) equivalent circuit model for integration, with noise sources due to switches active during

and (c) equivalent circuit model for integration, with noise sources due to switches active during ![]() and due to the amplifier.

and due to the amplifier.

Figure 2.15b shows the model for the thermal noise introduced by switches controlled by clock phase ![]() . For both SC branches, the two active switches are assumed to have the same on-resistance (

. For both SC branches, the two active switches are assumed to have the same on-resistance (![]() ) and they are in series with a noise voltage source

) and they are in series with a noise voltage source ![]() . The PSD of each of these noise sources in a single-sided frequency representation is thus

. The PSD of each of these noise sources in a single-sided frequency representation is thus ![]() , where

, where ![]() is Boltzmann's constant and

is Boltzmann's constant and ![]() is the absolute temperature. Each of the noise sources generates a sample-and-held noise component in the corresponding capacitor voltage given by the well-known

is the absolute temperature. Each of the noise sources generates a sample-and-held noise component in the corresponding capacitor voltage given by the well-known ![]() expression due to the foldover effect [7–9]:

expression due to the foldover effect [7–9]:

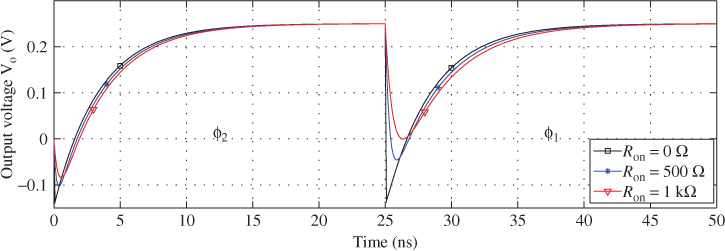

Figure 2.15c shows the model for the thermal noise introduced by switches controlled by clock phase ![]() and for the noise in the amplifier. These switches originate an additional noise component in the capacitor voltage of the corresponding SC branch, similarly given by Equation 2.35. On the other hand, a single-pole model is assumed for the amplifier and its equivalent input noise is modeled by a voltage source

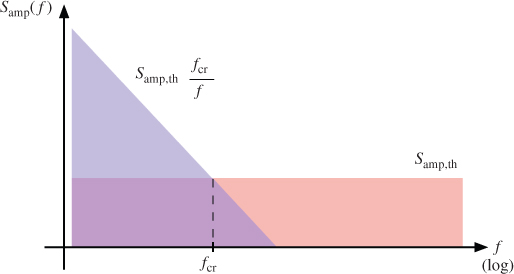

and for the noise in the amplifier. These switches originate an additional noise component in the capacitor voltage of the corresponding SC branch, similarly given by Equation 2.35. On the other hand, a single-pole model is assumed for the amplifier and its equivalent input noise is modeled by a voltage source ![]() at the positive input terminal. As illustrated in Figure 2.16, the amplifier noise is basically determined by a broadband thermal component and a narrowband flicker component, so that

at the positive input terminal. As illustrated in Figure 2.16, the amplifier noise is basically determined by a broadband thermal component and a narrowband flicker component, so that

Figure 2.16 Illustration of the PSD of the amplifier noise showing the contributions of ![]() and thermal noise.

and thermal noise.

where ![]() represents the amplifier thermal noise PSD referred to its input and

represents the amplifier thermal noise PSD referred to its input and ![]() represents the amplifier corner frequency—that is, the frequency at which

represents the amplifier corner frequency—that is, the frequency at which ![]() noise is equal to the thermal noise.4 The amplifier noise generates correlated sample-and-held noise components in the integrator sampling capacitors that can be obtained as

noise is equal to the thermal noise.4 The amplifier noise generates correlated sample-and-held noise components in the integrator sampling capacitors that can be obtained as

where the amplifier noise bandwidth ![]() is required to account for the foldover effect of thermal noise. As shown in [3], it can be estimated as

is required to account for the foldover effect of thermal noise. As shown in [3], it can be estimated as ![]() , with

, with ![]() given by Equation 2.27.

given by Equation 2.27.

Adding up the former circuit noise components in the SC integrator, the total input-referred5 noise PSD yields [3]

where the factor 2 multiplying ![]() accounts for the contributions of switches controlled by

accounts for the contributions of switches controlled by ![]() and

and ![]() , whereas the factor 2 before the brackets accounts for the actual fully-differential implementation of the SC integrator, in which the number of SC branches and thus of switches doubles in comparison to the single-ended scheme in Figure 2.15. Replacing Equations 2.35 and 2.37 in 2.38, the total input-referred noise PSD of the front-end integrator of an SC-

, whereas the factor 2 before the brackets accounts for the actual fully-differential implementation of the SC integrator, in which the number of SC branches and thus of switches doubles in comparison to the single-ended scheme in Figure 2.15. Replacing Equations 2.35 and 2.37 in 2.38, the total input-referred noise PSD of the front-end integrator of an SC-![]() M can thus be approximated to be

M can thus be approximated to be

2.39 ![]()

in which the approximation ![]() for

for ![]() has been used for simplicity.

has been used for simplicity.

The input-referred IBN of an SC-![]() M due to circuit noise can be easily obtained by integrating the former expression over the input signal bandwidth, so that

M due to circuit noise can be easily obtained by integrating the former expression over the input signal bandwidth, so that

in which the ![]() noise component has been integrated from a frequency

noise component has been integrated from a frequency ![]() to exclude DC due to its logarithmic nature.

to exclude DC due to its logarithmic nature.

For an SC-![]() M to achieve a given noise performance, the sum of all three components in Equation 2.40 have to meet the demanded noise floor. Note that:

M to achieve a given noise performance, the sum of all three components in Equation 2.40 have to meet the demanded noise floor. Note that:

- For a given OSR, to reduce the contribution of the switches' thermal noise, the size of the sampling capacitors at the modulator input must be increased, which results in larger speed requirements for the amplifier and thus in larger power consumption.

- For a given OSR, to reduce the contribution of the amplifier thermal noise, its GB must be reduced as much as the integrator settling requirements allow.

- To reduce the flicker contribution the amplifier corner frequency must be kept low. In low-bandwidth applications, cancelation techniques such as correlated double sampling (CDS) or chopper are often required for further reduction of the

component [10].

component [10].

2.6 Clock Jitter in SC- Ms

Ms

Discrete-time ![]() Ms are affected in practice by timing uncertainties6 in the clock phases that control the SC operation. However, they exhibit largertolerance to clock jitter than Nyquist converters, because jitter sensitivity is reduced by the modulator OSR [12].

Ms are affected in practice by timing uncertainties6 in the clock phases that control the SC operation. However, they exhibit largertolerance to clock jitter than Nyquist converters, because jitter sensitivity is reduced by the modulator OSR [12].

The effect of clock jitter in SC-![]() Ms is mainly limited to a sampling uncertainty of the modulator input signal. Timing uncertainties during the integration phase only cause an extra error to be added to the integrator settling error and their influence can be neglected in practice, whereas the contributions of other integrators than the front-end one will be reduced by the noise shaping. Therefore, different SC-

Ms is mainly limited to a sampling uncertainty of the modulator input signal. Timing uncertainties during the integration phase only cause an extra error to be added to the integrator settling error and their influence can be neglected in practice, whereas the contributions of other integrators than the front-end one will be reduced by the noise shaping. Therefore, different SC-![]() Ms exhibit similar sensitivity to clock jitter [13].

Ms exhibit similar sensitivity to clock jitter [13].

Sampling time uncertainty causes a nonuniform sampling of the modulator input signal that results in an increase of the in-band error power. The magnitude of this increase is usually estimated for SC-![]() Ms assuming random statistical properties for the clock jitter [12]. For a modulator input sinewave

Ms assuming random statistical properties for the clock jitter [12]. For a modulator input sinewave ![]() as shown in Figure 2.17, an uncertainty of

as shown in Figure 2.17, an uncertainty of ![]() in the sampling instant causes an error in the sampled signal given by:

in the sampling instant causes an error in the sampled signal given by:

Figure 2.17 Illustration of nonuniform sampling of a signal due to clock jitter. The gray shaded areas represent the timing uncertainties.

2.41 ![]()

Under the assumption of white jitter, the power of this modulated error distributes uniformly, so that only a fraction of it is located within the ![]() M passband. The in-band noise due to clock jitter can thus be easily obtained as

M passband. The in-band noise due to clock jitter can thus be easily obtained as

where ![]() represents the standard deviation of the timing uncertainty. Taking into account that

represents the standard deviation of the timing uncertainty. Taking into account that ![]() and

and ![]() , an upper bound can be calculated for Equation 2.42

, an upper bound can be calculated for Equation 2.42

showing that the sensitivity of SC-![]() Ms to clock jitter is reduced by

Ms to clock jitter is reduced by ![]() .

.

2.7 Sources of Distortion in SC- Ms

Ms

Analog devices used for the implementation of ![]() Ms exhibit in practice a certain nonlinearity. These nonlinearities generate distortion and thus limit the peak SNDR attainable for high input amplitudes. Nevertheless, deriving closed-form expressions for the distortion generated in a

Ms exhibit in practice a certain nonlinearity. These nonlinearities generate distortion and thus limit the peak SNDR attainable for high input amplitudes. Nevertheless, deriving closed-form expressions for the distortion generated in a ![]() M is in general much more awkward than analyzing the effect of linear errors. Therefore, several simplifications are often made to handle nonlinearities. First, only the sources of distortion associated with the front-end integrator in the

M is in general much more awkward than analyzing the effect of linear errors. Therefore, several simplifications are often made to handle nonlinearities. First, only the sources of distortion associated with the front-end integrator in the ![]() M are considered, as they directly add to the modulator signal with no attenuation and thus dominate the overall modulator nonlinearity. Distortion generated in subsequent integrators is suppressed by the increasing noise shaping when referred to the modulator input, so that their contributions can be considered negligible in practice. Second, each source of nonlinearity is conceived as a small deviation from the ideal linear behavior—that is, as a weak nonlinearity—that affects the modulator performance in an additive way.

M are considered, as they directly add to the modulator signal with no attenuation and thus dominate the overall modulator nonlinearity. Distortion generated in subsequent integrators is suppressed by the increasing noise shaping when referred to the modulator input, so that their contributions can be considered negligible in practice. Second, each source of nonlinearity is conceived as a small deviation from the ideal linear behavior—that is, as a weak nonlinearity—that affects the modulator performance in an additive way.

Figure 2.18 illustrates the main sources of distortion in an SC integrator, in which a fully-differential topology is assumed for the suppression of even-order harmonics. In SC-![]() Ms, linearity is basically limited by the voltage dependency of capacitors, of the switches on-resistance, and of the amplifier gain, as well as by the SR-limited integrator dynamics (already discussed in Section 2.4.3). Distortion arising from charge injection in the switches can be neglected if clock phases with delayed falling edges are employed [14]. Besides, given the highly linear capacitors that present mixed-mode technological processes offer—such as MiM and MoM capacitors—their effect will not be further considered here.7 The influence of the nonlinearity of the switches and of the amplifier gain will be discussed later.

Ms, linearity is basically limited by the voltage dependency of capacitors, of the switches on-resistance, and of the amplifier gain, as well as by the SR-limited integrator dynamics (already discussed in Section 2.4.3). Distortion arising from charge injection in the switches can be neglected if clock phases with delayed falling edges are employed [14]. Besides, given the highly linear capacitors that present mixed-mode technological processes offer—such as MiM and MoM capacitors—their effect will not be further considered here.7 The influence of the nonlinearity of the switches and of the amplifier gain will be discussed later.

Figure 2.18 Main sources of distortion in a fully-differential SC integrator.

2.7.1 Nonlinear Amplifier Gain

The DC gain of an amplifier exhibits in practice a voltage-dependent characteristic, because the output resistance of the amplifier output transistors decreases as the amplifier output voltage deviates from the quiescent point. Figure 2.19 illustrates this effect with electrical simulations results of a folded-cascode amplifier designed in a 2.5-V 0.25-![]() m CMOS process. Note that the amplifier DC gain is about 8500 (78.5 dB) at the common-mode output voltage, but it decreases for increasing output levels and drops abruptly near the amplifier saturation region.

m CMOS process. Note that the amplifier DC gain is about 8500 (78.5 dB) at the common-mode output voltage, but it decreases for increasing output levels and drops abruptly near the amplifier saturation region.

Figure 2.19 Illustration of the dependency of the amplifier gain on the output voltage level.

The influence of the amplifier gain nonlinearity can be easily incorporated into the leaky integrator model in Section 2.2, so that the difference equation in Equation 2.2 can be rewritten as [3]

2.44

where ![]() represents the effective amplifier gain at the output voltage corresponding to clock cycle

represents the effective amplifier gain at the output voltage corresponding to clock cycle ![]() and

and ![]() corresponds to that of clock cycle

corresponds to that of clock cycle ![]() . As will be shown in Section 3.3, solving this difference equation in an iterative way, together with a table look-up for the amplifier gain, allows for accurately accounting for the voltage dependency of the amplifier gain in transient behavioral simulations—in spite of the nonlinearity being weak or strong!

. As will be shown in Section 3.3, solving this difference equation in an iterative way, together with a table look-up for the amplifier gain, allows for accurately accounting for the voltage dependency of the amplifier gain in transient behavioral simulations—in spite of the nonlinearity being weak or strong!

For weak nonlinearities, a polynomial approximation can be used for modeling the voltage dependency near the quiescent point and for obtaining rough estimations of the generated distortion. Let us assume that the amplifier gain of the front-end integrator in an SC-![]() M, such as that shown in Figure 2.18, is expressed as

M, such as that shown in Figure 2.18, is expressed as

2.45 ![]()

where ![]() represents the

represents the ![]() th-order voltage-gain coefficient of the amplifier DC gain. If a sinewave with amplitude

th-order voltage-gain coefficient of the amplifier DC gain. If a sinewave with amplitude ![]() is applied at the modulator input, the input-referred distortion of the third-order harmonic can be estimated as [3, 15]

is applied at the modulator input, the input-referred distortion of the third-order harmonic can be estimated as [3, 15]

2.46

where ![]() is the parasitic capacitor at the amplifier input nodes. Note that decreasing the integrator gain coefficient clearly helps to reduce distortion. However, the most direct way to reduce the effect of the amplifier gain nonlinearity is increasing the value of the amplifier gain itself [3, 13].

is the parasitic capacitor at the amplifier input nodes. Note that decreasing the integrator gain coefficient clearly helps to reduce distortion. However, the most direct way to reduce the effect of the amplifier gain nonlinearity is increasing the value of the amplifier gain itself [3, 13].

2.7.2 Nonlinear Switch On-Resistance

Switches in SC-![]() Ms are usually implemented as CMOS transmission gates, so that, at least, either the nMOS or the pMOS transistors are on for a given voltage level to be transmitted. Figure 2.20a sketches the on-conductance of nMOS and pMOS switches, assuming that they exhibit a resistance in the triode region that can be approximated to [3, 16]

Ms are usually implemented as CMOS transmission gates, so that, at least, either the nMOS or the pMOS transistors are on for a given voltage level to be transmitted. Figure 2.20a sketches the on-conductance of nMOS and pMOS switches, assuming that they exhibit a resistance in the triode region that can be approximated to [3, 16]

where ![]() represents the switch input voltage—that is, the common-mode voltage of the drain and source terminals. The on-resistance of the CMOS transmission gate is thus obtained as

represents the switch input voltage—that is, the common-mode voltage of the drain and source terminals. The on-resistance of the CMOS transmission gate is thus obtained as ![]() , warranting a rail-to-rail operation of the switch as long as

, warranting a rail-to-rail operation of the switch as long as ![]() .8 Figure 2.20b shows electrical simulation results of a transmission gate in a 2.5-V 0.25-

.8 Figure 2.20b shows electrical simulation results of a transmission gate in a 2.5-V 0.25-![]() m CMOS process, in which the voltage dependency of the switch on-resistance is clearly visible.

m CMOS process, in which the voltage dependency of the switch on-resistance is clearly visible.

Figure 2.20 Illustration of a switch on-state performance: (a) sketch of the on-conductance versus input voltage and (b) simulation results of the on-resistance versus input voltage in a 2.5-V 0.25-![]() m CMOS process.

m CMOS process.

To analyze the relative influence of the different switches in the front-end integrator of an SC-![]() M on the generated distortion, let us consider the schematic in Figure 2.18. The modulator input signal is sampled on capacitors

M on the generated distortion, let us consider the schematic in Figure 2.18. The modulator input signal is sampled on capacitors ![]() through switches

through switches ![]() and

and ![]() during

during ![]() . As switches

. As switches ![]() are connected to the modulator input, their on-resistances directly depend on the modulator input level and are the dominant source of distortion. However, switches

are connected to the modulator input, their on-resistances directly depend on the modulator input level and are the dominant source of distortion. However, switches ![]() have one of their terminals connected to the common-mode voltage—that is, to a voltage that remains approximately constant over time—so that the voltage level of these switches is not expected to change much over the clock periods [5]. As a result, the distortion introduced by switches

have one of their terminals connected to the common-mode voltage—that is, to a voltage that remains approximately constant over time—so that the voltage level of these switches is not expected to change much over the clock periods [5]. As a result, the distortion introduced by switches ![]() will be considerably lower than that of switches

will be considerably lower than that of switches ![]() . The same reasoning can be applied to switches

. The same reasoning can be applied to switches ![]() and

and ![]() during

during ![]() : switches

: switches ![]() have one terminal connected to a fixed voltage—the common-mode voltage, as depicted in Figure 2.18, or the DAC feedback voltage—and switches

have one terminal connected to a fixed voltage—the common-mode voltage, as depicted in Figure 2.18, or the DAC feedback voltage—and switches ![]() are connected to the virtual ground of the amplifier. Their influence on the generated distortion can thus be neglected in practice.

are connected to the virtual ground of the amplifier. Their influence on the generated distortion can thus be neglected in practice.

Chapter 4 will demonstrate the distortion generated by nonlinear sampling in an SC-![]() M can be accurately evaluated through transistor-level electrical simulations of the equivalent circuit in Figure 2.21. A tone with large amplitude can be applied at the differential input and the differential voltage stored in capacitors

M can be accurately evaluated through transistor-level electrical simulations of the equivalent circuit in Figure 2.21. A tone with large amplitude can be applied at the differential input and the differential voltage stored in capacitors ![]() can be collected at the clock rate to compute the FFT and measure the THD.

can be collected at the clock rate to compute the FFT and measure the THD.

Figure 2.21 Equivalent circuit for evaluating distortion during sampling due to the switch nonlinearity.

Finally, Section 4.4.1 will demonstrate that the generated distortion can be reduced not only by keeping the switch as linear as possible, but also by reducing the value of the on-resistance itself. Figure 2.22 illustrates the switch on-resistance for different alternatives for the relative sizing of the switch transistors. If the sizes compensate the difference in the transconductance parameter of the nMOS and pMOS transistors—that is, ![]() , as used for instance in [3]—the nonlinearity of the on-resistance is low, but its average value is larger than for

, as used for instance in [3]—the nonlinearity of the on-resistance is low, but its average value is larger than for ![]() —as used in [5]. In the latter case, the switch area and its parasitic capacitors increase, but the slow-down effect of the switch

—as used in [5]. In the latter case, the switch area and its parasitic capacitors increase, but the slow-down effect of the switch ![]() on the integrator settling will decrease, as discussed in Section 2.4.4. Note that the design trade-offs above can be solved in opposite directions depending on the particular linearity and speed requirements of an SC-

on the integrator settling will decrease, as discussed in Section 2.4.4. Note that the design trade-offs above can be solved in opposite directions depending on the particular linearity and speed requirements of an SC-![]() M, as well as the modulator input range relative to the supply voltage.

M, as well as the modulator input range relative to the supply voltage.

Figure 2.22 Illustration of the switch on-resistance nonlinearity for different transistor sizings in a 2.5-V 0.25-![]() m CMOS process.

m CMOS process.

2.8 Nonidealities in Continuous-Time  Modulators

Modulators

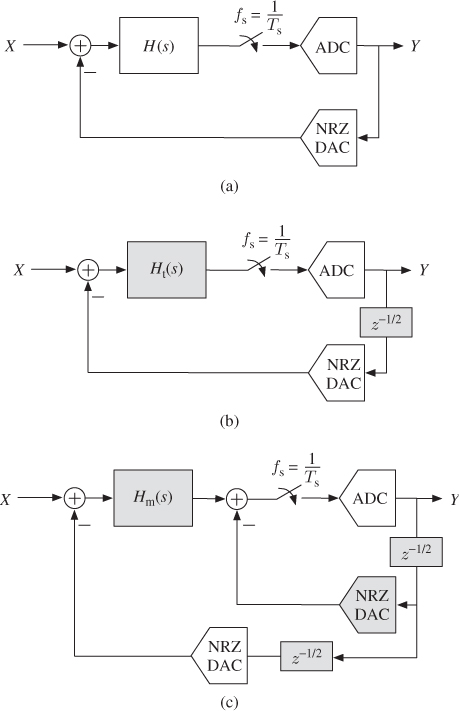

As illustrated in Figure 2.23, circuit errors in CT-![]() Ms can be divided into two main categories:

Ms can be divided into two main categories:

- Building-block errors, which are the nonideal effects derived from the modulator loop filter implementation—similar to the SC case—, such as finite amplifier gain (for active-RC implementations), integrator time-constant error, circuit noise, nonlinearities, etc.

- Architectural timing errors, namely: clock jitter, excess loop delay, and quantizer metastability.

Figure 2.23 Main nonidealities affecting the performance of continuous-time ![]() Ms.

Ms.

The former group of errors causes similar effects on the performance of CT-![]() Ms as in the case of their DT counterparts. Therefore, they can also be classified according to their degradation on the modulator performance: either causing a deviation in NTF or an additive noise component at the modulator input.

Ms as in the case of their DT counterparts. Therefore, they can also be classified according to their degradation on the modulator performance: either causing a deviation in NTF or an additive noise component at the modulator input.

As stated in Section 1.8, CT implementations are potentially faster than SC ones, leading to much more relaxed designs (in terms of power consumption) when high-speed operation is required. In addition, they do not suffer from ![]() noise. However, SC implementations have intrinsically lower parameter variations, as most circuit parameters are defined by capacitor ratios, instead of by absolute parameter values as in the case of CT-

noise. However, SC implementations have intrinsically lower parameter variations, as most circuit parameters are defined by capacitor ratios, instead of by absolute parameter values as in the case of CT-![]() Ms. In the following sections, main nonideal effects of CT-

Ms. In the following sections, main nonideal effects of CT-![]() Ms are described, putting emphasis on the most critical design issues.

Ms are described, putting emphasis on the most critical design issues.

2.9 Clock Jitter in CT- Ms

Ms

Continuous-time ![]() Ms are more severely affected by timing uncertainties than their DT counterparts. Conversely to DT-

Ms are more severely affected by timing uncertainties than their DT counterparts. Conversely to DT-![]() Ms, sampling time uncertainties occur at the quantizer input, where the jitter-induced error is strongly suppressed by the noise shaping and can thus be neglected in practice. However, errors resulting from timing uncertainties in the DAC feedback signal add directly to the modulator input with no suppression, hence being the dominant jitter effect and limiting the overall modulator performance.