Chapter 1

Introduction to ΣΔ Modulators: Basic Concepts and Fundamentals

This chapter is conceived as an introduction to ![]() analog-to-digital converters (ADCs). Their operation principle consists in combining oversampling, quantization error processing, and negative feedback for improving the effective resolution of a coarse quantizer. These basic concepts are presented in Section 1.1 and their effects on the performance of

analog-to-digital converters (ADCs). Their operation principle consists in combining oversampling, quantization error processing, and negative feedback for improving the effective resolution of a coarse quantizer. These basic concepts are presented in Section 1.1 and their effects on the performance of ![]() converters are compared with Nyquist-rate converters. Section 1.2 shows the basic architecture, ideal behavior, and performance metrics of

converters are compared with Nyquist-rate converters. Section 1.2 shows the basic architecture, ideal behavior, and performance metrics of ![]() converters, and sketches the architectural alternatives to enhance their resolution.

converters, and sketches the architectural alternatives to enhance their resolution.

Before presenting practical topologies for the implementation of ![]() modulation, the large variety of the existing

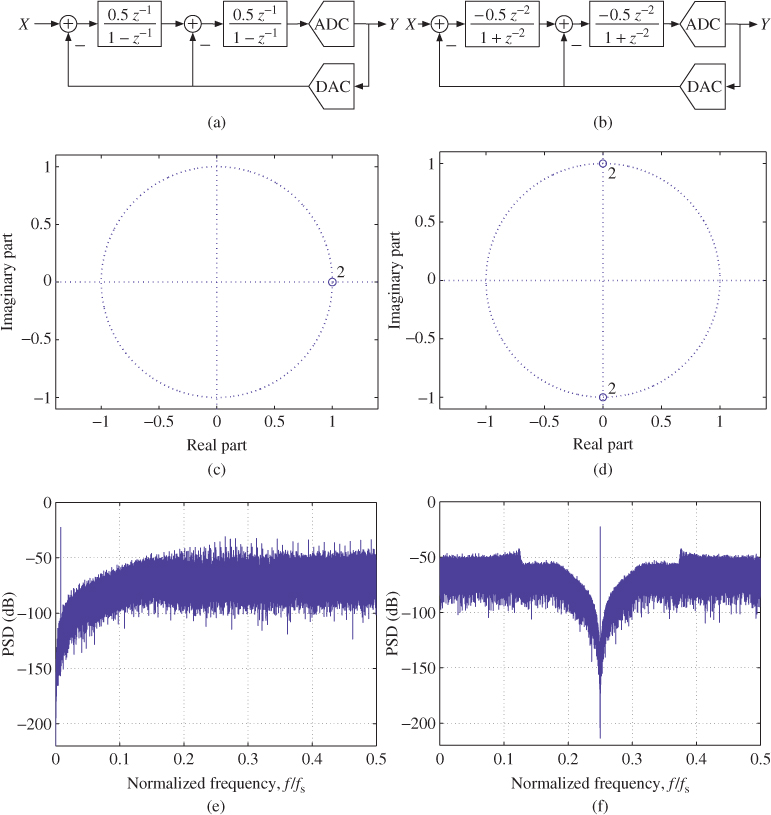

modulation, the large variety of the existing ![]() realizations is briefly classified in Section 1.3 according to the type of modulator architecture (single loops or cascades), the circuit techniques employed (discrete time (DT) or continuous time (CT)), and the nature of the signals being converted (low pass (LP) or band pass (BP)). Starting from the case of DT, LP, single-bit

realizations is briefly classified in Section 1.3 according to the type of modulator architecture (single loops or cascades), the circuit techniques employed (discrete time (DT) or continuous time (CT)), and the nature of the signals being converted (low pass (LP) or band pass (BP)). Starting from the case of DT, LP, single-bit ![]() modulators, the implications of these different alternatives are then presented in an incremental way.

modulators, the implications of these different alternatives are then presented in an incremental way.

Section 1.4 is dedicated to single-loop ![]() architectures. Second- and higher-order single-loops are considered, taking into account issues related to their practical implementation and problems not addressed by linear models, such as instabilities. Cascade

architectures. Second- and higher-order single-loops are considered, taking into account issues related to their practical implementation and problems not addressed by linear models, such as instabilities. Cascade ![]() topologies are covered in Section 1.5. In Section 1.6 the topological study is extended to

topologies are covered in Section 1.5. In Section 1.6 the topological study is extended to ![]() modulators using multibit embedded quantizers, analyzing their pros and cons. Techniques to circumvent the disadvantages, such as dynamic element matching (DEM) or dual quantization, are revised.

modulators using multibit embedded quantizers, analyzing their pros and cons. Techniques to circumvent the disadvantages, such as dynamic element matching (DEM) or dual quantization, are revised.

The conversion of BP signals is covered in Section 1.7, taking into account its typical application in digital radio receivers. The basic techniques for synthesizing DT, BP ![]() modulators are presented, together with practical aspects for their implementation. Finally, Section 1.8 addresses the realization of CT

modulators are presented, together with practical aspects for their implementation. Finally, Section 1.8 addresses the realization of CT ![]() modulators, discussing their advantages compared to DT ones and the existing alternatives for the loop filter and the feedback implementation.

modulators, discussing their advantages compared to DT ones and the existing alternatives for the loop filter and the feedback implementation.

1.1 Basics of A/D Conversion

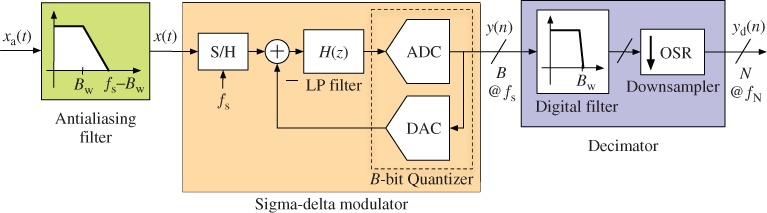

ADCs are electronic systems that perform the transformation of analog signals—which are continuous in time and in amplitude—into digital signals—which are discrete in both time and amplitude. Figure 1.1 illustrates the general block diagram of an ADC intended for the conversion of LP signals, which essentially consists of an antialiasing filter (AAF), a sampler, and a quantizer. First, the analog input signal ![]() of the ADC passes through the AAF, an LP analog filter than prevents out-of-band components from folding over the signal bandwidth

of the ADC passes through the AAF, an LP analog filter than prevents out-of-band components from folding over the signal bandwidth ![]() during the subsequent sampling, what would corrupt the signal information. The resulting band-limited signal

during the subsequent sampling, what would corrupt the signal information. The resulting band-limited signal ![]() is sampled at a rate

is sampled at a rate ![]() by the S/H circuit, thus yielding a DT signal

by the S/H circuit, thus yielding a DT signal ![]() , where

, where ![]() . Finally, the values of

. Finally, the values of ![]() are quantized using

are quantized using ![]() bits, so that each continuous-valued input sample is mapped onto the closer discrete-valued level out of the

bits, so that each continuous-valued input sample is mapped onto the closer discrete-valued level out of the ![]() that cover the input range, yielding the converter digital output

that cover the input range, yielding the converter digital output ![]() .

.

Figure 1.1 General block diagram of an A/D converter. A Nyquist-rate ADC is assumed.

As shown in Figure 1.1, the fundamental processes involved in the A/D conversion are sampling and quantization, whose implications are discussed in the following text.

1.1.1 Sampling

The sampling process performs the continuous-to-discrete transformation of the input signal in time and imposes a limit on the bandwidth of the analog input signal. According to the Nyquist theorem, to prevent information loss, ![]() must be sampled at a minimum rate of

must be sampled at a minimum rate of ![]() , often referred to as the Nyquist frequency. On the basis of this criterion, ADCs in which analog input signal is sampled at the minimum rate (

, often referred to as the Nyquist frequency. On the basis of this criterion, ADCs in which analog input signal is sampled at the minimum rate (![]() ) are called Nyquist-rate ADCs. Conversely, ADCs in which

) are called Nyquist-rate ADCs. Conversely, ADCs in which ![]() are called oversampling ADCs. How much faster than required the input signal is sampled is expressed in terms of the oversampling ratio (OSR), defined as

are called oversampling ADCs. How much faster than required the input signal is sampled is expressed in terms of the oversampling ratio (OSR), defined as

1.1 ![]()

Whether oversampling is used or not in an ADC has a noticeable influence on the requirements of its AAF. As in Nyquist-rate ADCs the input signal bandwidth ![]() coincides with

coincides with ![]() , aliasing will occur if

, aliasing will occur if ![]() in Figure 1.1 contains frequency components above

in Figure 1.1 contains frequency components above ![]() . High-order analog AAFs are thus required to implement sharp transition bands capable of removing out-of-band components with no significant attenuation of the signal band, as illustrated in Figure 1.2a for the LP case. Conversely, as

. High-order analog AAFs are thus required to implement sharp transition bands capable of removing out-of-band components with no significant attenuation of the signal band, as illustrated in Figure 1.2a for the LP case. Conversely, as ![]() in oversampling ADCs, the replicas of the input signal spectrum that are created by the sampling process are farther apart than in Nyquist-rate ADCs. As illustrated in Figure 1.2b, frequency components of the input signal in the range

in oversampling ADCs, the replicas of the input signal spectrum that are created by the sampling process are farther apart than in Nyquist-rate ADCs. As illustrated in Figure 1.2b, frequency components of the input signal in the range ![]() do not alias within the signal band, so that the filter transition band can be smoother, what greatly reduces the order required for the AAF and simplifies its design.

do not alias within the signal band, so that the filter transition band can be smoother, what greatly reduces the order required for the AAF and simplifies its design.

Figure 1.2 Antialiasing filter for (a) Nyquist-rate ADCs and (b) oversampling ADCs.

1.1.2 Quantization

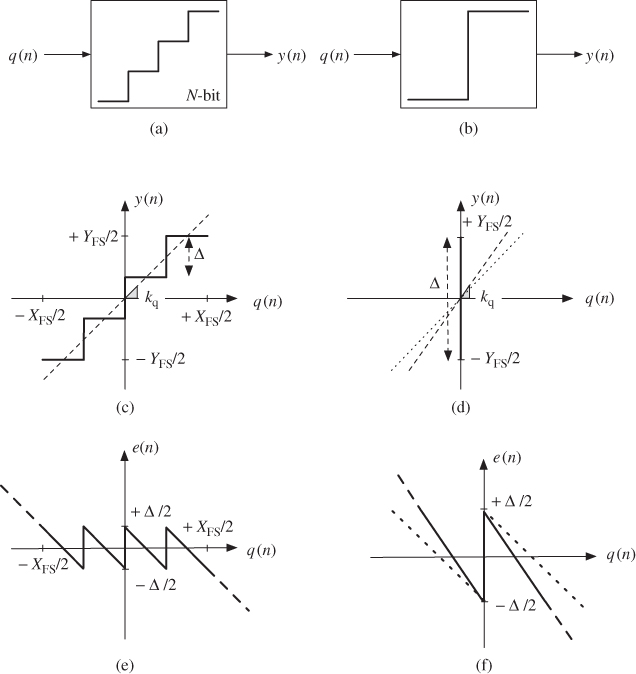

The quantization process also introduces a limitation on the performance of an ideal ADC, because an error is generated while performing the continuous-to-discrete transformation of the input signal in amplitude, commonly referred to as quantization error. The operation of quantizers is illustrated in Figure 1.3. As a matter of example, Figure 1.3c depicts the I/O characteristic of a quantizer with ![]() , although results apply to a generic

, although results apply to a generic ![]() -bit quantizer. Input amplitudes within the full-scale input range

-bit quantizer. Input amplitudes within the full-scale input range ![]() are rounded to 1 out of the

are rounded to 1 out of the ![]() different output levels, which are usually encoded into a binary digital representation. If these levels are equally spaced, the quantizer is said to be uniform and the separation between adjacent output levels is defined as the quantization step

different output levels, which are usually encoded into a binary digital representation. If these levels are equally spaced, the quantizer is said to be uniform and the separation between adjacent output levels is defined as the quantization step

where ![]() stands for the full-scale output range. As

stands for the full-scale output range. As ![]() and

and ![]() are not necessarily equal, the quantizer may exhibit a gain different from unity, as indicated in Figure 1.3c by the slope

are not necessarily equal, the quantizer may exhibit a gain different from unity, as indicated in Figure 1.3c by the slope ![]() . As shown in Figure 1.3e, the quantizer operation thus inherently generates a rounding error that is a nonlinear function of the input. Note that, if

. As shown in Figure 1.3e, the quantizer operation thus inherently generates a rounding error that is a nonlinear function of the input. Note that, if ![]() is kept within the range

is kept within the range ![]() , the quantization error

, the quantization error ![]() is bounded within

is bounded within ![]() . The former input range is known as the nonoverload region of the quantizer, as opposed to ranges with

. The former input range is known as the nonoverload region of the quantizer, as opposed to ranges with ![]() , for which the magnitude of

, for which the magnitude of ![]() grows monotonously.

grows monotonously.

Figure 1.3 Illustration of the quantization process: (a) multibit quantizer block, (b) single-bit quantizer block, (c) I/O characteristic of a multibit quantizer, (d) I/O characteristic of a single-bit quantizer, (e) multibit quantization error, and (f) single-bit quantization error.

Figure 1.3 also shows the operation of a single-bit quantizer (![]() ). Note from Figure 1.3d that, compared to the multibit case, the output of a single-bit quantizer is determined by the input sign only, regardless of its magnitude. Therefore, the gain

). Note from Figure 1.3d that, compared to the multibit case, the output of a single-bit quantizer is determined by the input sign only, regardless of its magnitude. Therefore, the gain ![]() is undefined and can be arbitrarily chosen.

is undefined and can be arbitrarily chosen.

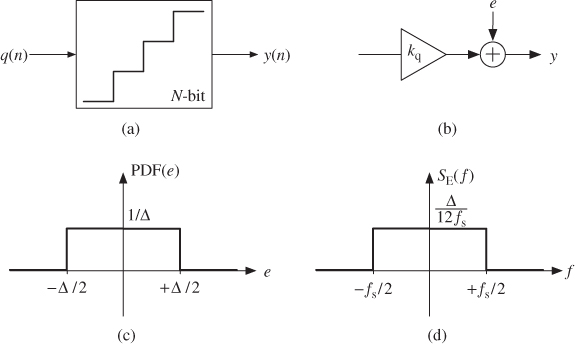

1.1.3 Quantization White Noise Model

In practice, an ideal quantizer as that shown in Figure 1.4a is often modeled using the linear scheme in Figure 1.4b if several assumptions are made on the statistical properties of the quantization error [1–3]. As already shown in Figure 1.3e, the quantization error ![]() is systematically determined by the quantizer input signal

is systematically determined by the quantizer input signal ![]() . Nevertheless, if

. Nevertheless, if ![]() is assumed to change randomly from sample to sample within the range

is assumed to change randomly from sample to sample within the range ![]() ,

, ![]() will also be uncorrelated from sample to sample. Under these requirements, the quantization error can be viewed as a random process with a uniform probability distribution in the range

will also be uncorrelated from sample to sample. Under these requirements, the quantization error can be viewed as a random process with a uniform probability distribution in the range ![]() , as illustrated in Figure 1.4c. The power associated to the quantization error can thus be computed as

, as illustrated in Figure 1.4c. The power associated to the quantization error can thus be computed as

1.3

The former assumption implies that, as illustrated in Figure 1.4d, the power of the quantization error will also be uniformly distributed in the range ![]() , yielding

, yielding

1.4

so that the power spectral density (PSD) of the quantization error in that range is

1.5 ![]()

These assumptions are collectively known as the additive white noise approximation

of the quantization error and allow the representation of a quantizer, which is deterministic and nonlinear, with the random linear model in Figure 1.4b, in which ![]() with

with ![]() being a quantization noise.1

being a quantization noise.1

Figure 1.4 Quantization noise: (a) multibit quantizer block, (b) equivalent linear model with additive white noise, (c) probability density function (PDF), and (d) power spectral density.

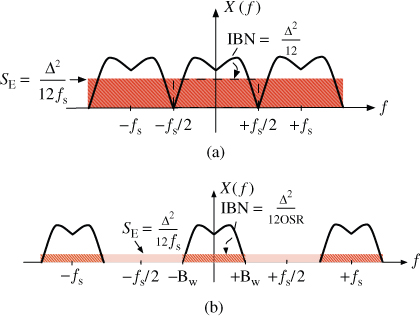

On the basis of this approximation of the quantization error to a white noise, the performance of ideal ADCs can be easily evaluated. For a Nyquist ADC, in which ![]() , all the quantization noise power falls inside the signal band and passes to the ADC output as a part of the input signal itself, as illustrated in Figure 1.5a. Conversely, if an oversampled signal is quantized, because

, all the quantization noise power falls inside the signal band and passes to the ADC output as a part of the input signal itself, as illustrated in Figure 1.5a. Conversely, if an oversampled signal is quantized, because ![]() , only a fraction of the total quantization noise power lies within the signal band, as illustrated in Figure 1.5b. The in-band noise power (IBN) caused by the quantization process in an ideal oversampling ADC is thus,

, only a fraction of the total quantization noise power lies within the signal band, as illustrated in Figure 1.5b. The in-band noise power (IBN) caused by the quantization process in an ideal oversampling ADC is thus,

so that the larger the OSR, the smaller the IBN.2

Figure 1.5 Quantization noise in (a) Nyquist-rate ADCs and (b) oversampling ADCs.

The dynamic range (DR) of an ideal ADC can be determined as the ratio of the output power at the frequency of an input sinusoid with maximum amplitude to the in-band quantization noise power:

1.7 ![]()

From Figure 1.3c, the maximum input amplitude in the nonoverload region of an ![]() -bit quantizer is

-bit quantizer is ![]() and its corresponding output power can be approximated to [5],

and its corresponding output power can be approximated to [5],

so that, using Equations 1.6 and 1.8, the DR of an ideal oversampling ADC yields

Note that, for a Nyquist ADC—that is, ![]() in Equation 1.9—each additional bit in the quantizer results in a DR increase of approximately

in Equation 1.9—each additional bit in the quantizer results in a DR increase of approximately ![]() . For an oversampling ADC, the DR further increases with the OSR by approximately

. For an oversampling ADC, the DR further increases with the OSR by approximately ![]() , so that using for instance an OSR of 4 is similar to having one extra bit in the

, so that using for instance an OSR of 4 is similar to having one extra bit in the ![]() -bit quantizer.

-bit quantizer.

1.1.4 Noise Shaping

An approach to further increase the accuracy of an oversampling ADC is shaping the quantization white noise in the frequency domain—that is, filtering it—in such a way that most of its power lies outside the signal band. This is illustrated in Figure 1.6a, where the quantization noise is conceptually obtained by subtracting the quantizer input signal ![]() from its output

from its output ![]() and then passes through a filter transfer function, usually called noise transfer function (NTF).

and then passes through a filter transfer function, usually called noise transfer function (NTF).

Figure 1.6 Quantization noise shaping: (a) conceptual block diagram and (b) effect on the in-band noise of an oversampling noise-shaping ADC.

For quantizers working on LP signals, the NTF is of high-pass type and can be easily obtained from a differentiator filter, with a ![]() -domain transfer function given by

-domain transfer function given by

where ![]() stands for the filter order. Taking into account that

stands for the filter order. Taking into account that ![]() , the magnitude of the pure-differentiator NTF in Equation 1.10 can be approximated for low frequencies to

, the magnitude of the pure-differentiator NTF in Equation 1.10 can be approximated for low frequencies to

so that the power due to the shaped quantization noise that lies within the signal band (Figure 1.6b) yields

Using Equations 1.8 and 1.12, the DR of an ideal oversampling noise-shaping ADC can be obtained as

Note that, in comparison with Equation 1.9, if oversampling is used in combination with noise shaping, the DR increases with OSR by approximately ![]() .

.

1.2 Basics of Sigma-Delta Modulators

Contrary to the ADCs discussed so far, which are open loop systems from a control perspective, Sigma-Delta (![]() ) ADCs rely on a feedback path to achieve a closed-loop control of the quantization error. The fundamentals on how the shaping of quantization noise is implemented in practice, as well as the basic architecture, performance metrics, and ideal behavior of oversampling noise-shaping ADCs is presented in the following sections.

) ADCs rely on a feedback path to achieve a closed-loop control of the quantization error. The fundamentals on how the shaping of quantization noise is implemented in practice, as well as the basic architecture, performance metrics, and ideal behavior of oversampling noise-shaping ADCs is presented in the following sections.

1.2.1 Topology of  ADCs

ADCs

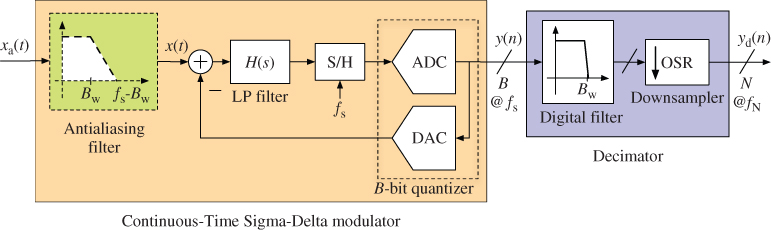

Figure 1.7 illustrates the basic block diagram of a ![]() ADC intended for the conversion of LP signals, which consists of the following:

ADC intended for the conversion of LP signals, which consists of the following:

- Antialiasing filter (AAF), which band limits the analog input signal to avoid aliasing during its subsequent sampling. As discussed in Section 1.1.1, oversampling considerably relaxes the attenuation requirements of the AAF, so that smooth transition bands are usually sufficient compared to Nyquist-rate ADCs.

- Sigma-Delta modulator (

M), in which the oversampling and quantization of the band-limited analog signal take place. The quantization noise of the embedded

M), in which the oversampling and quantization of the band-limited analog signal take place. The quantization noise of the embedded  -bit quantizer is shaped in the frequency domain by placing an appropriate loop filter

-bit quantizer is shaped in the frequency domain by placing an appropriate loop filter  before it and closing a negative feedback loop around them. Low-resolution quantizers, with

before it and closing a negative feedback loop around them. Low-resolution quantizers, with  typically in the range 1–5 bit, are sufficient for obtaining small IBN and high accuracy in the A/D conversion.

typically in the range 1–5 bit, are sufficient for obtaining small IBN and high accuracy in the A/D conversion. - Decimation filter, in which a high-selectivity digital filter sharply removes the out-of-band spectral content of the

M output and thus most of the shaped quantization noise. The decimator also reduces the data rate from

M output and thus most of the shaped quantization noise. The decimator also reduces the data rate from  down to the Nyquist frequency, while increasing the word length from

down to the Nyquist frequency, while increasing the word length from  to

to  bits to preserve resolution.

bits to preserve resolution.

Figure 1.7 General block diagram of a ![]() ADC. A low-pass discrete-time

ADC. A low-pass discrete-time ![]() M is assumed.

M is assumed.

The ![]() modulator is the block that has most influence on the performance of the ADC, basically because it is responsible for the sampling and quantization processes that ultimately limit the accuracy of the A/D conversion. We will focus on this block from now on, although it must be kept in mind that a

modulator is the block that has most influence on the performance of the ADC, basically because it is responsible for the sampling and quantization processes that ultimately limit the accuracy of the A/D conversion. We will focus on this block from now on, although it must be kept in mind that a ![]() ADC is more than a

ADC is more than a ![]() M!

M!

1.2.2 Signal Processing in  Ms

Ms

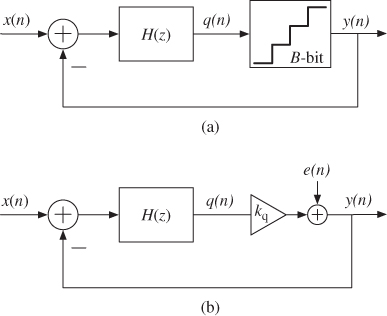

The basic scheme of a ![]() modulator consists of a loop filter

modulator consists of a loop filter ![]() and a

and a ![]() -bit quantizer in a feedback loop, as shown in Figure 1.8a [6]. Let us consider that the gain of the loop filter is large within the signal band and small outside it. Owing to the action of negative feedback, the analog input signal

-bit quantizer in a feedback loop, as shown in Figure 1.8a [6]. Let us consider that the gain of the loop filter is large within the signal band and small outside it. Owing to the action of negative feedback, the analog input signal ![]() and the analog version of the

and the analog version of the ![]() M output

M output ![]() will practically coincide within the signal band, so that the error signal

will practically coincide within the signal band, so that the error signal ![]() in this closed-loop system is very small within the signal band. As the

in this closed-loop system is very small within the signal band. As the ![]() -bit quantizer is uniform, mostof the differences between the input and the output of the

-bit quantizer is uniform, mostof the differences between the input and the output of the ![]() M will be placed at higher frequencies, so that the quantization noise is shaped in the frequency domain and most of its power is pushed outside the signal band.

M will be placed at higher frequencies, so that the quantization noise is shaped in the frequency domain and most of its power is pushed outside the signal band.

Figure 1.8 ![]() modulator: (a) block diagram and (b) ideal linear model.

modulator: (a) block diagram and (b) ideal linear model.

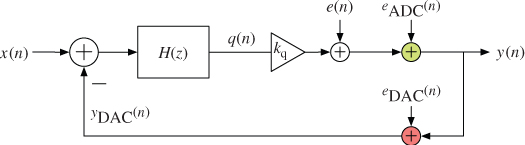

Using the linear additive white noise model in Figure 1.4b for the embedded quantizer, the ![]() M in Figure 1.8a can be modeled as the two-input (

M in Figure 1.8a can be modeled as the two-input (![]() and

and ![]() ) one-output (

) one-output (![]() ) linear system in Figure 1.8b, which is described in the

) linear system in Figure 1.8b, which is described in the ![]() -domain as

-domain as

1.14 ![]()

where STF and NTF stand for the signal and noise transfer functions, respectively given by

1.15 ![]()

Note that, if the loop filter is designed such that ![]() within the signal band, then

within the signal band, then ![]() and

and ![]() ; that is, the quantization noise is ideally canceled while the input signal is perfectly transferred to the output.

; that is, the quantization noise is ideally canceled while the input signal is perfectly transferred to the output.

For the conversion of LP signals, the simplest loop filter ![]() that exhibits the desired frequency performance is an integrator,

that exhibits the desired frequency performance is an integrator,

that, in combination with an embedded quantizer with ![]() , leads to a

, leads to a ![]() M whose output is given by

M whose output is given by

1.17 ![]()

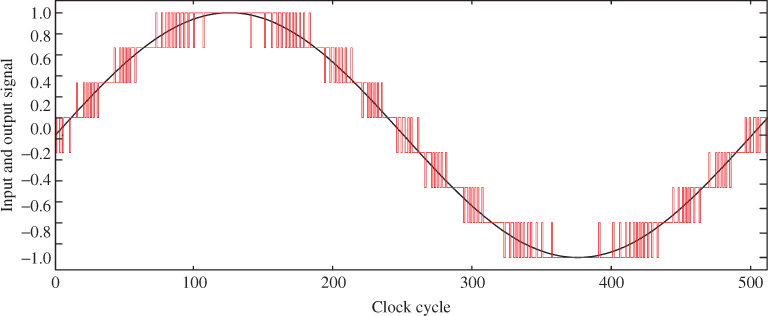

and builds up a first-order, high-pass shaping of the quantization noise—see Equation 1.10. For the sake of illustration, Figure 1.9 shows the output signal of a first-order ![]() M with a embedded 3-bit (8-level) quantizer for a sinusoidal input signal. Note that, due to the combined action of oversampling and negative feedback, the modulator output is a pulse-density modulated (PDM) signal whose local average tracks the input signal value within adjacent code transitions.

M with a embedded 3-bit (8-level) quantizer for a sinusoidal input signal. Note that, due to the combined action of oversampling and negative feedback, the modulator output is a pulse-density modulated (PDM) signal whose local average tracks the input signal value within adjacent code transitions.

Figure 1.9 PDM output signal of a first-order, ![]() modulator with an embedded 3-bit quantizer for an input sinusoid.

modulator with an embedded 3-bit quantizer for an input sinusoid.

1.2.3 Performance Metrics of  Ms

Ms

Contrary to Nyquist-rate ADCs, whose performance is mainly characterized by static performance metrics—that is, monotonicity, gain and offset errors, differential nonlinearity (DNL), and integral nonlinearity (INL) [5]—![]() ADCs' characteristics are typically measured using dynamic performance metrics, which are obtained from the frequency-domain representation of the time-domain digital output sequence. The latter thus requires the computation of the fast Fourier transform (FFT) of a finite-length output sequence with a specific windowing function, as will be discussed in Chapter 4. From that power spectrum representation of a

ADCs' characteristics are typically measured using dynamic performance metrics, which are obtained from the frequency-domain representation of the time-domain digital output sequence. The latter thus requires the computation of the fast Fourier transform (FFT) of a finite-length output sequence with a specific windowing function, as will be discussed in Chapter 4. From that power spectrum representation of a ![]() M output sequence, some spectral metrics are directly measured and other noise and power metrics are derived.

M output sequence, some spectral metrics are directly measured and other noise and power metrics are derived.

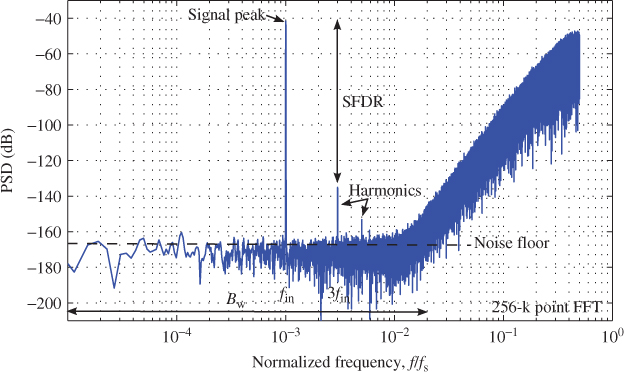

Figure 1.10 illustrates an exemplary spectrum of a ![]() M output sequence when a sinusoidal signal with frequency

M output sequence when a sinusoidal signal with frequency ![]() is applied at its input. The main characteristics of the spectrum are highlighted; for example, the length of the digital sequence from which the FFT has been computed, the output signal peak at the frequency

is applied at its input. The main characteristics of the spectrum are highlighted; for example, the length of the digital sequence from which the FFT has been computed, the output signal peak at the frequency ![]() corresponding to the converted signal, etc. As will be discussed in Chapter 2, nonidealities of the circuitry used for implementing the

corresponding to the converted signal, etc. As will be discussed in Chapter 2, nonidealities of the circuitry used for implementing the ![]() M deviate in practice the output spectrum from a purely shaped quantization noise. On the one hand, linear errors give rise to a noise floor, as well as to a degradation of the shaping order. On the other, nonlinear errors generate distortion, which is typically noticeable for large input amplitudes, but submerged under the noise floor for small input signal amplitudes. Spectral metrics such as the spurious-free dynamic range (SFDR)—that is, the ratio of the signal power to the strongest spectral tone [5]—can be directly measured from the output modulator spectrum, as shown in Figure 1.10.

M deviate in practice the output spectrum from a purely shaped quantization noise. On the one hand, linear errors give rise to a noise floor, as well as to a degradation of the shaping order. On the other, nonlinear errors generate distortion, which is typically noticeable for large input amplitudes, but submerged under the noise floor for small input signal amplitudes. Spectral metrics such as the spurious-free dynamic range (SFDR)—that is, the ratio of the signal power to the strongest spectral tone [5]—can be directly measured from the output modulator spectrum, as shown in Figure 1.10.

Figure 1.10 Illustration of a typical output spectrum of a ![]() modulator and its main characteristics. A low-pass

modulator and its main characteristics. A low-pass ![]() M is assumed.

M is assumed.

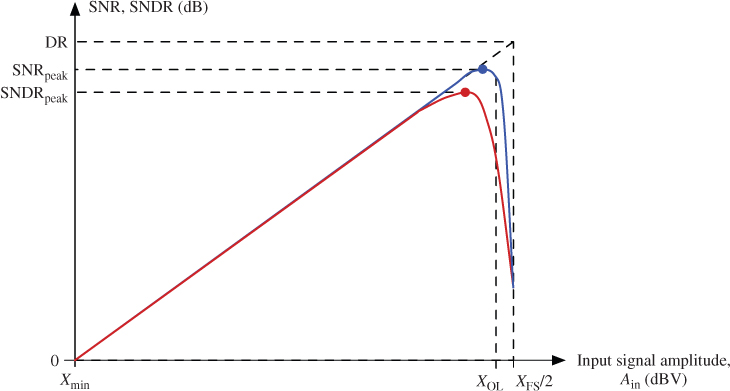

Noise and power metrics are derived from the ![]() M output spectra by integration over the signal bandwidth and are typically collected in a single plot as shown in Figure 1.11. These metrics are usually the most important measures and comprise the following:

M output spectra by integration over the signal bandwidth and are typically collected in a single plot as shown in Figure 1.11. These metrics are usually the most important measures and comprise the following:

- Signal-to-noise ratio (SNR), which is the ratio of the output power at the frequency of an input sinusoid to the uncorrelated IBN:

1.18

It accounts for the modulator linear performance only, so that the in-band power associated to harmonics of the input signal is not considered as part of the IBN for SNR computation.If an ideal

M is considered and only the in-band quantization noise is accounted for in the IBN computation, the term signal-to-quantization-noise ratio (SQNR) is often employed.

M is considered and only the in-band quantization noise is accounted for in the IBN computation, the term signal-to-quantization-noise ratio (SQNR) is often employed. - Signal-to-noise-plus-distortion ratio (SNDR), which is defined as the ratio of the output power at the frequency of an input sinusoid to the total IBN power, also accounting for possible harmonics at the

M output. As illustrated in Figure 1.11, this makes a typical SNDR curve to deviate from the SNR curve only for large input amplitudes, for which the generated distortion is noticeable. Therefore, the output spectra from which the SNDR curve is computed are typically obtained by applying an input signal at

M output. As illustrated in Figure 1.11, this makes a typical SNDR curve to deviate from the SNR curve only for large input amplitudes, for which the generated distortion is noticeable. Therefore, the output spectra from which the SNDR curve is computed are typically obtained by applying an input signal at  (for LP

(for LP  Ms), so that at least the second and third harmonics lie within the signal band.

Ms), so that at least the second and third harmonics lie within the signal band. - Dynamic range (DR), which can be defined as the ratio of the output power at the frequency of an input sinusoid with maximum amplitude to the output power for a small input amplitude for which

; that is, so it cannot be distinguished from the error. Ideally, a sinusoid with maximum amplitude at the modulator input will provide an output sinusoid sweeping the full-scale range

; that is, so it cannot be distinguished from the error. Ideally, a sinusoid with maximum amplitude at the modulator input will provide an output sinusoid sweeping the full-scale range  of the embedded quantizer, so that

of the embedded quantizer, so that

- Effective number of bits (ENOB): as the DR of an ideal

-bit Nyquist-rate converter is given by Equation 1.9 with

-bit Nyquist-rate converter is given by Equation 1.9 with  , a similar expression can be established for

, a similar expression can be established for  Ms

Ms

where ENOB can be defined as the number of bits needed for an ideal Nyquist-rate ADC to achieve the same DR as the

ADC. The performance of oversampled

ADC. The performance of oversampled  converters and Nyquist-rate ADCs can thus be compared in a simple way [7].Instead of the DR, the peak SNDR is also often used in Equation 1.20 to express the accuracy of the A/D in a

converters and Nyquist-rate ADCs can thus be compared in a simple way [7].Instead of the DR, the peak SNDR is also often used in Equation 1.20 to express the accuracy of the A/D in a  modulator in bits.

modulator in bits. - Overload Level (OL): as illustrated in Figure 1.11, the SNR of a

modulator increases monotonously with the input signal amplitude (

modulator increases monotonously with the input signal amplitude ( ), but sharply drops for input amplitudes close to half of the full-scale input range of the embedded quantizer (

), but sharply drops for input amplitudes close to half of the full-scale input range of the embedded quantizer ( ) due to its overload and the associated IBN increase. The overload level is considered to define the maximum input amplitude for which the

) due to its overload and the associated IBN increase. The overload level is considered to define the maximum input amplitude for which the  M still operates correctly and can almost be arbitrarily defined, but it is typically chosen as the amplitude for which the SNR drops

M still operates correctly and can almost be arbitrarily defined, but it is typically chosen as the amplitude for which the SNR drops  below the peak SNR [8].

below the peak SNR [8].

Figure 1.11 Illustration of the performance metrics of a ![]() modulator on a typical SNR curve.

modulator on a typical SNR curve.

1.2.4 Performance Enhancement of  Ms

Ms

The output of an ideal LP ![]() th-order

th-order ![]() modulator in the

modulator in the ![]() -domain can be considered to be

-domain can be considered to be

where ![]() and the NTF builds up an

and the NTF builds up an ![]() th-order high-pass shaping of the quantization noise of the embedded quantizer. If a

th-order high-pass shaping of the quantization noise of the embedded quantizer. If a ![]() -bit quantizer is employed, the DR of the

-bit quantizer is employed, the DR of the ![]() M can be obtained from Equations 1.12 and 1.19 to ideally yield

M can be obtained from Equations 1.12 and 1.19 to ideally yield

taking into account that ![]() —see Equation 1.2 —and considering quantization noise as the only contribution to the IBN.

—see Equation 1.2 —and considering quantization noise as the only contribution to the IBN.

Note from Equation 1.22 that the DR of a ![]() modulator is ideally determined by the values of

modulator is ideally determined by the values of ![]() , OSR, and

, OSR, and ![]() , which can thus be considered as the three key parameters that define the

, which can thus be considered as the three key parameters that define the ![]() M at the high level. The pros and cons of increasing the DR of a

M at the high level. The pros and cons of increasing the DR of a ![]() modulator by increasing each of these parameters are briefly discussed in the following:

modulator by increasing each of these parameters are briefly discussed in the following:

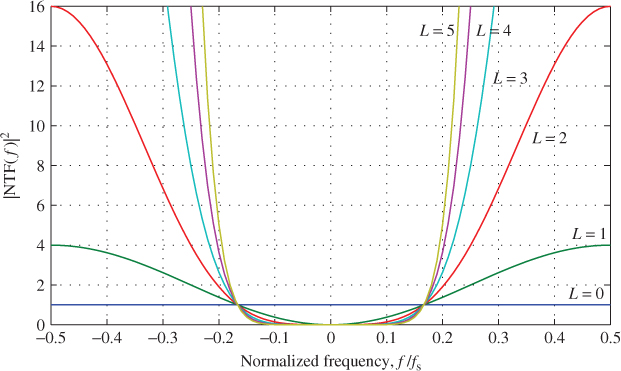

- High-order

modulators. The accuracy of the A/D conversion can be considerably improved by increasing the noise-shaping order, because a larger fraction of the total quantization noise power will be pushed out of the signal band. Figure 1.12 illustrates the ideal noise-shaping functions of orders ranging from 1 to 5. The case

modulators. The accuracy of the A/D conversion can be considerably improved by increasing the noise-shaping order, because a larger fraction of the total quantization noise power will be pushed out of the signal band. Figure 1.12 illustrates the ideal noise-shaping functions of orders ranging from 1 to 5. The case  —that is, no shaping—is also included for comparison purposes. The DR enhancement if

—that is, no shaping—is also included for comparison purposes. The DR enhancement if  is increased in one for a given OSR can be obtained from Equation 1.22 to be

is increased in one for a given OSR can be obtained from Equation 1.22 to be

1.23

This means that, for instance, the DR of a fourth-order

M with

M with  is ideally

is ideally  (

( ) larger than that of a third-order

) larger than that of a third-order  M. However, as will be discussed in Section 1.4.2, the use of high-order (

M. However, as will be discussed in Section 1.4.2, the use of high-order ( ) loop filters gives rise to stability problems in a

) loop filters gives rise to stability problems in a  M. Although these problems can be circumvented, the DR of a high-order

M. Although these problems can be circumvented, the DR of a high-order  M will in practice be smaller than predicted in Equation 1.22.

M will in practice be smaller than predicted in Equation 1.22. - High OSR

modulators. Figure 1.13 shows the ideal DR as a function of OSR for noise-shaping orders ranging from 0 (no shaping) to 5 and assuming a single-bit embedded quantizer (

modulators. Figure 1.13 shows the ideal DR as a function of OSR for noise-shaping orders ranging from 0 (no shaping) to 5 and assuming a single-bit embedded quantizer ( ). As illustrated, the combination of oversampling and noise-shaping considerably enhances the

). As illustrated, the combination of oversampling and noise-shaping considerably enhances the  M performance for

M performance for  . Note from Equation 1.22 that the DR of an ideal

. Note from Equation 1.22 that the DR of an ideal  th-order

th-order  modulator increases with OSR in

modulator increases with OSR in  . However, for a given conversion bandwidth

. However, for a given conversion bandwidth  , the OSR cannot be arbitrarily increased, because it leads to a higher sampling frequency

, the OSR cannot be arbitrarily increased, because it leads to a higher sampling frequency  for the operation of the

for the operation of the  circuitry. The latter, if achievable in practice for a given technological process, leads to larger power consumption.

circuitry. The latter, if achievable in practice for a given technological process, leads to larger power consumption. - Multibit

modulators. An increase in

modulators. An increase in  leads to a decrease of the quantization step

leads to a decrease of the quantization step  and thus to a reduction of the quantization noise power. Each additional bit in the embedded quantizer of a

and thus to a reduction of the quantization noise power. Each additional bit in the embedded quantizer of a  M is considered to typically yield a 6 dB (1 bit) improvement on the DR [9]. However, a multibit embedded quantizer requires a multilevel DAC to close the negative feedback loop in the

M is considered to typically yield a 6 dB (1 bit) improvement on the DR [9]. However, a multibit embedded quantizer requires a multilevel DAC to close the negative feedback loop in the  M. Contrary to a two-level feedback DAC (

M. Contrary to a two-level feedback DAC ( ), which is inherently linear, a multilevel DAC will in practice be nonlinear to some extent. As noticeable from Figure 1.14, the DAC nonlinearity will be directly added to the

), which is inherently linear, a multilevel DAC will in practice be nonlinear to some extent. As noticeable from Figure 1.14, the DAC nonlinearity will be directly added to the  M input and will thus appear at the output, as

M input and will thus appear at the output, as  within the signal band. Therefore, the linearity required in a multibit DAC equals in practice that wanted for the

within the signal band. Therefore, the linearity required in a multibit DAC equals in practice that wanted for the  modulator. This point will be further discussed in Section 1.6.

modulator. This point will be further discussed in Section 1.6.

Figure 1.12 Illustration of the shaping of quantization noise as a function of frequency in a ![]() M. NTF is given by Equation 1.10 and

M. NTF is given by Equation 1.10 and ![]() stands for the noise-shaping order.

stands for the noise-shaping order.

Figure 1.13 Ideal dynamic range of a ![]() M as a function of the oversampling ratio for different noise-shaping orders (

M as a function of the oversampling ratio for different noise-shaping orders (![]() ). A single-bit internal quantizer (

). A single-bit internal quantizer (![]() ) is assumed.

) is assumed.

Figure 1.14 Second-order ![]() modulator with unity STF.

modulator with unity STF.

1.3 Classification of  Modulators

Modulators

The strategies discussed in Section 1.2.4 for improving the DR of a ![]() M may be combined in many different ways, giving rise to the huge number of

M may be combined in many different ways, giving rise to the huge number of ![]() M topologies reported in literature, which can be grouped attending to different classification criteria [10]:

M topologies reported in literature, which can be grouped attending to different classification criteria [10]:

- Single-Loop versus Cascade

Ms (attending to the number of quantizers employed).

Ms (attending to the number of quantizers employed).  Ms employing only one quantizer are called single-loop

topologies, whereas those employing several quantizers are often named cascade or MASH

Ms employing only one quantizer are called single-loop

topologies, whereas those employing several quantizers are often named cascade or MASH  Ms. These topological alternatives will be discussed in Sections 1.4 and 1.5.

Ms. These topological alternatives will be discussed in Sections 1.4 and 1.5. - Single-Bit versus Multibit

Ms (attending to the number of bits in the embedded quantizer). Their pros and cons will be discussed in Section 1.6.

Ms (attending to the number of bits in the embedded quantizer). Their pros and cons will be discussed in Section 1.6. - Low-Pass versus Band-Pass

Ms (attending to the nature of the signals being converted). The A/D conversion of LP signals has been assumed in previous sections, but BP

Ms (attending to the nature of the signals being converted). The A/D conversion of LP signals has been assumed in previous sections, but BP  Ms can also be built, as will be discussed in Section 1.7.

Ms can also be built, as will be discussed in Section 1.7. - Discrete-Time versus Continuous-Time

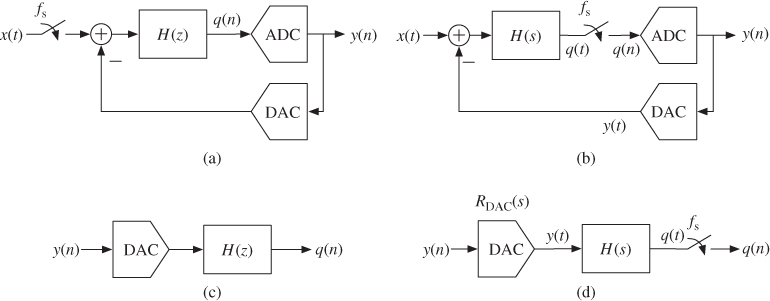

Ms (attending to the nature of loop filter dynamics). The use of a DT loop filter in the

Ms (attending to the nature of loop filter dynamics). The use of a DT loop filter in the  M has been assumed in previous sections. However, CT

M has been assumed in previous sections. However, CT  Ms can be also implemented in practice. According to this classification criteria, hybrid CT/DT

Ms can be also implemented in practice. According to this classification criteria, hybrid CT/DT  Ms take advantage of the benefits of both DT and CT implementations, which will be discussed in Section 1.8.

Ms take advantage of the benefits of both DT and CT implementations, which will be discussed in Section 1.8.

Describing all possible ![]() M architectures derived from previous classification criteria goes beyond the scope of this book. A detailed analysis of them can be found in the many papers and books devoted to the topic in the

M architectures derived from previous classification criteria goes beyond the scope of this book. A detailed analysis of them can be found in the many papers and books devoted to the topic in the ![]() literature [4, 9, 11–23]. Instead, we will hereafter focus on the most representative families of

literature [4, 9, 11–23]. Instead, we will hereafter focus on the most representative families of ![]() modulators.

modulators.

1.4 Single-Loop  Modulators

Modulators

![]() modulators that make use of only one embedded quantizer are usually referred to as single-loop topologies. To get familiar with these architectures, their performance, their circuit-level implementation, as well as some other practical aspects are first addressed considering the case of second-order

modulators that make use of only one embedded quantizer are usually referred to as single-loop topologies. To get familiar with these architectures, their performance, their circuit-level implementation, as well as some other practical aspects are first addressed considering the case of second-order ![]() Ms. Afterward, the problematics of stability in higher-order

Ms. Afterward, the problematics of stability in higher-order ![]() Ms is presented, together with architectural alternatives to circumvent it.

Ms is presented, together with architectural alternatives to circumvent it.

1.4.1 Second-Order  M

M

Figure 1.15a shows a second-order ![]() modulator built up by cascading two DT integrators [24], with each integrator receiving a weighted feedback path from the DAC. Coefficients

modulator built up by cascading two DT integrators [24], with each integrator receiving a weighted feedback path from the DAC. Coefficients ![]() are usually called integrator scalings or weights. Under linear analysis, the modulator output in the

are usually called integrator scalings or weights. Under linear analysis, the modulator output in the ![]() -domain yields

-domain yields

where ![]() stands for the gain of the quantizer. For a pure second-order shaping, Equation 1.24 needs to be simplified to

stands for the gain of the quantizer. For a pure second-order shaping, Equation 1.24 needs to be simplified to

1.25 ![]()

so that the following expressions for the integrator coefficients need to be fulfilled:

Figure 1.15 Block diagram of second-order ![]() Ms and different notations: (a) general representation of the DT-

Ms and different notations: (a) general representation of the DT-![]() M using the notation in [8, 9] and (b) alternative representation of the DT-

M using the notation in [8, 9] and (b) alternative representation of the DT-![]() M using the notation in [12, 19].

M using the notation in [12, 19].

Figure 1.15b shows an alternative representation of the second-order ![]() M according to the coefficients notation in [12, 19], which allows to allocate different weights in the forward and feedback paths of each integrator, using coefficients

M according to the coefficients notation in [12, 19], which allows to allocate different weights in the forward and feedback paths of each integrator, using coefficients ![]() and

and ![]() , respectively. As exemplary illustrated in Figure 1.16, the notations in Figure 1.15a and b can be easily connected with the equalities:

, respectively. As exemplary illustrated in Figure 1.16, the notations in Figure 1.15a and b can be easily connected with the equalities:

Figure 1.16 Illustration of the equivalence between the DT representations in Figure 1.15a and 1.14b.

Both nomenclatures for the integrator scaling coefficients of ![]() modulators will be used throughout this book. The notation in [8, 9] is closer to the modulator architectural level, whereas the notation in [12, 19] is closer to the actual circuit-level implementation, in which integrators with more than one SC input branch are usually employed. The latter is thus useful to accurately account for some nonidealities of the practical

modulators will be used throughout this book. The notation in [8, 9] is closer to the modulator architectural level, whereas the notation in [12, 19] is closer to the actual circuit-level implementation, in which integrators with more than one SC input branch are usually employed. The latter is thus useful to accurately account for some nonidealities of the practical ![]() M implementation, which will be covered in Chapter 2.

M implementation, which will be covered in Chapter 2.

For the sake of illustration, Figure 1.17 shows a possible implementation of the second-order ![]() M in Figure 1.15 using fully-differential SC circuitry and assuming single-bit quantization. The modulator differential input signal is denoted by

M in Figure 1.15 using fully-differential SC circuitry and assuming single-bit quantization. The modulator differential input signal is denoted by ![]() and the modulator digital output

and the modulator digital output ![]() , after the comparator, controls the feedback connection of reference voltages

, after the comparator, controls the feedback connection of reference voltages ![]() and

and ![]() to the integrators. The modulator full scale range

to the integrators. The modulator full scale range ![]() thus equals

thus equals ![]() , with

, with ![]() . Note from the first SC integrator in Figure 1.17 that both the modulator input signal and the DAC feedback signal are processed through the sampling capacitor

. Note from the first SC integrator in Figure 1.17 that both the modulator input signal and the DAC feedback signal are processed through the sampling capacitor ![]() . For the second integrator, the output of the first integrator is processed through both

. For the second integrator, the output of the first integrator is processed through both ![]() and

and ![]() , whereas the DAC feedback signal is processed only through

, whereas the DAC feedback signal is processed only through ![]() . The modulator scaling coefficients are thus implemented as the following capacitor ratios (Figure 1.15b)

. The modulator scaling coefficients are thus implemented as the following capacitor ratios (Figure 1.15b)

1.28

Figure 1.17 Fully-differential SC implementation of a second-order ![]() modulator.

modulator.

In practice, the value of the integrator weights are selected to fulfill the relations in Equation 1.26, also taking into account their implication in some aspects of the modulator performance, such as the following:

- Keeping the state variables (integrator outputs) bounded to ensure the modulator stability. The second-order

M is stable for inputs in the range

M is stable for inputs in the range  if

if  , regardless the quantizer gains

, regardless the quantizer gains  [24]. This condition is already met if

[24]. This condition is already met if  —see Equations 1.26 and 1.27.

—see Equations 1.26 and 1.27. - Keeping the modulator overload level as close as possible to the full scale to ensure a high-peak SNR—see Figure 1.11.

- Minimizing the required signal range at the integrators outputs; that is, the integrator output swing demands must be attainable with the intended voltage supply and as low as possible to reduce power consumption and to facilitate circuit design.

- Simplifying the practical implementation of the integrator weights as ratios of unit capacitors.

Generally speaking, the selection of the scaling coefficients of a ![]() modulator involves solving several trade-offs between architectural-, circuit-, and technological-level aspects of the practical implementation, so that the optimum selection for a given application may not apply in a different scenario. For the sake of illustration, Table 1.1 shows several sets of weights reported for the second-order, single-bit

modulator involves solving several trade-offs between architectural-, circuit-, and technological-level aspects of the practical implementation, so that the optimum selection for a given application may not apply in a different scenario. For the sake of illustration, Table 1.1 shows several sets of weights reported for the second-order, single-bit ![]() M in Figure 1.15. All sets exhibit an overload level

M in Figure 1.15. All sets exhibit an overload level ![]() (i.e.,

(i.e., ![]() below the full-scale amplitude

below the full-scale amplitude ![]() ). The required integrator output swing and the minimum number of unit capacitors are also included. Capacitor sharing between weights in the same integrator has been considered.

). The required integrator output swing and the minimum number of unit capacitors are also included. Capacitor sharing between weights in the same integrator has been considered.

Table 1.1 Comparison of some sets of coefficients reported for the second-order single-bit ![]() M

M

Second-Order  M with Unity STF

M with Unity STF

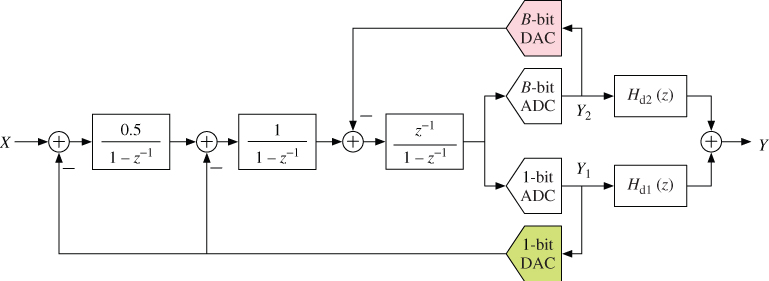

Figure 1.14 shows an alternative second-order ![]() M topology that makes use of feed-forward paths to implement a so-called unity STF [28, 29]. Under linear analysis, the modulator output in the

M topology that makes use of feed-forward paths to implement a so-called unity STF [28, 29]. Under linear analysis, the modulator output in the ![]() -domain yields

-domain yields

1.29 ![]()

so that ![]() —that is, the signal transfer function equals 1 at all frequencies—whereas NTF is unaffected.

—that is, the signal transfer function equals 1 at all frequencies—whereas NTF is unaffected.

One of the most appealing features of the unity-STF ![]() M in Figure 1.14 is that ideally there is no input signal trace processed by the integrators. Indeed, the integrator inputs in

M in Figure 1.14 is that ideally there is no input signal trace processed by the integrators. Indeed, the integrator inputs in ![]() -domain can be obtained as

-domain can be obtained as

1.30 ![]()

showing that they depend only on the quantization error. In practice, there will be some residual component of the modulator input signal at the integrator inputs, but it is normally negligible. This means that, if nonlinearities of the circuit implementation are accounted for, the generated distortion will be considerably lower for the unity-STF ![]() M in Figure 1.14 compared to the one traditional

M in Figure 1.14 compared to the one traditional ![]() M in Figure 1.15. Moreover, the technique is effective for any OSR, which makes unity-STF

M in Figure 1.15. Moreover, the technique is effective for any OSR, which makes unity-STF ![]() Ms especially suited for lowering the sensitivity to circuit imperfections in wideband applications, in which low OSR values are required.

Ms especially suited for lowering the sensitivity to circuit imperfections in wideband applications, in which low OSR values are required.

The described concept of unity STF can be extended to a noise shaping of any order. The only requirement is to ideally make ![]() , without changing the modulator NTF. In recent years, it has been often applied in

, without changing the modulator NTF. In recent years, it has been often applied in ![]() Ms for wideband and multimode applications [30–34].

Ms for wideband and multimode applications [30–34].

1.4.2 High-Order  Ms

Ms

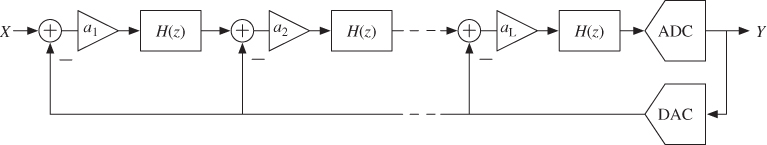

The simplest way to extend a ![]() M to an arbitrary

M to an arbitrary ![]() th-order shaping consists of including

th-order shaping consists of including ![]() integrators before the quantizer. Extending the second-order

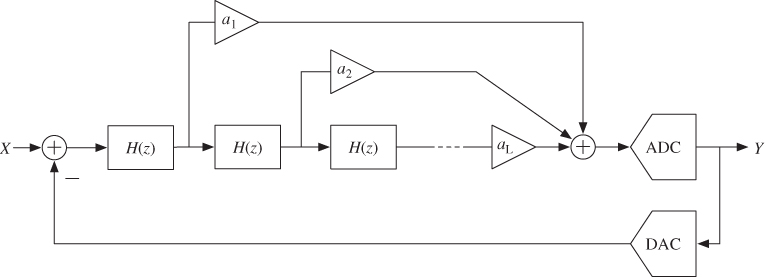

integrators before the quantizer. Extending the second-order ![]() M in Figure 1.15a, the topology in Figure 1.18 is obtained, which is known as an

M in Figure 1.15a, the topology in Figure 1.18 is obtained, which is known as an ![]() th-order single-loop

th-order single-loop ![]() M with distributed feedback [35].3 Ideally, its NTF can be derived from linear analysis and equated to Equation 1.10 to derive a set of relations between the integrator scaling coefficients to be fulfilled for obtaining a pure-differentiator noise shaping—similarly as done in Equation 1.26 for the second-order

M with distributed feedback [35].3 Ideally, its NTF can be derived from linear analysis and equated to Equation 1.10 to derive a set of relations between the integrator scaling coefficients to be fulfilled for obtaining a pure-differentiator noise shaping—similarly as done in Equation 1.26 for the second-order ![]() M. The in-band quantization noise and the modulator DR would thus be ideally given by Equations 1.12 and 1.13, respectively.

M. The in-band quantization noise and the modulator DR would thus be ideally given by Equations 1.12 and 1.13, respectively.

Figure 1.18 High-order single-loop ![]() M with distributed feedback.

M with distributed feedback.

However, this modulator performance cannot be met in practice because ![]() Ms with pure-differentiator FIR NTFs are prone to instability if

Ms with pure-differentiator FIR NTFs are prone to instability if ![]() , exhibiting unbounded states and poor SNR compared to that predicted by linear analysis. In general, instability appears at the modulator output as a large-amplitude, low-frequency oscillation, leading to long bitstreams of alternating

, exhibiting unbounded states and poor SNR compared to that predicted by linear analysis. In general, instability appears at the modulator output as a large-amplitude, low-frequency oscillation, leading to long bitstreams of alternating ![]() s and

s and ![]() s. This tendency to instability can be explained as follows [36]. For a

s. This tendency to instability can be explained as follows [36]. For a ![]() M to be stable, the quantizer input must not be allowed to become too large. As the quantizer input is obtained as (Figure 1.18)

M to be stable, the quantizer input must not be allowed to become too large. As the quantizer input is obtained as (Figure 1.18)

1.31 ![]()

the gain of ![]() , or simply

, or simply ![]() , must not be too large. However, as clearly visible from Figure 1.12, the out-of-band gain of FIR NTFs of the form

, must not be too large. However, as clearly visible from Figure 1.12, the out-of-band gain of FIR NTFs of the form ![]() rapidly increases for

rapidly increases for ![]() , yielding

, yielding ![]() at

at ![]() . Consequently, it starts to overload the quantizer, which yields a significant decrease of the modulator SNR.

. Consequently, it starts to overload the quantizer, which yields a significant decrease of the modulator SNR.

This problem can be circumvented by resorting to single-loop ![]() Ms with IIR NTFs of the form

Ms with IIR NTFs of the form ![]() , with

, with ![]() being a polynomial determined by the modulator scaling coefficients that helps to limit the out-of-band gain of NTF.4 However, unlike second-order

being a polynomial determined by the modulator scaling coefficients that helps to limit the out-of-band gain of NTF.4 However, unlike second-order ![]() Ms, for which a stability condition has been extracted [24], determining exact conditions that guarantee the stability of higher-order, single-loop

Ms, for which a stability condition has been extracted [24], determining exact conditions that guarantee the stability of higher-order, single-loop ![]() Ms is still an open question. In [8, 37], it is shown, using behavioral simulations, that high-order

Ms is still an open question. In [8, 37], it is shown, using behavioral simulations, that high-order ![]() Ms are conditionally stable; that is, with proper selection of the scaling coefficients, a stable operation can be obtained for inputs restricted within a certain range and for certain initial conditions of the state variables. However, despite the absence of general stability conditions, high-order

Ms are conditionally stable; that is, with proper selection of the scaling coefficients, a stable operation can be obtained for inputs restricted within a certain range and for certain initial conditions of the state variables. However, despite the absence of general stability conditions, high-order ![]() Ms have been successfully designed since the late 1980s [38]. Indeed, the topology in Figure 1.18 has been widely used and optimal coefficients for it have been presented in [8].

Ms have been successfully designed since the late 1980s [38]. Indeed, the topology in Figure 1.18 has been widely used and optimal coefficients for it have been presented in [8].

Its STF and NTF can be calculated under linear analysis as5

because of its simplicity and its good agreement with simulation results.

If integrators described by Equation 1.16 are used as filters—![]() —the NTF can be approximated for low frequencies to [8]

—the NTF can be approximated for low frequencies to [8]

1.35 ![]()

in which the complete scaling of the outermost feedback branch of the ![]() M dominates the noise-shaping behavior. Similarly as done Equations 1.11 and 1.12, the IBN of an

M dominates the noise-shaping behavior. Similarly as done Equations 1.11 and 1.12, the IBN of an ![]() th-order, single-loop

th-order, single-loop ![]() M with distributed feedback thus yields

M with distributed feedback thus yields

so that the IBN increases by a factor ![]() compared to an ideal

compared to an ideal ![]() M.

M.

A major drawback of this loop filter implementation in Figure 1.18 is that the integrator outputs contain a significant amount of the input signal [41], so that the integrators require significant swing capabilities and/or the scaling coefficients need to be low. This can be circumvented using the loop filter topology in Figure 1.19, which is a chain of integrators with feed-forward summation [42]. Under linear analysis, the corresponding STF and NTF can be calculated as

Note that NTF structure is the same as in Equation 1.34; therefore, the IBN of this ![]() M topology yields an expression similar to that in Equation 1.36.

M topology yields an expression similar to that in Equation 1.36.

Figure 1.19 High-order single-loop ![]() M with feed-forward summation.

M with feed-forward summation.

However, for the case of the distributed feedback topology in Figure 1.18 and the feed-forward summation topology in Figure 1.19, the loop filter for the STF and the NTF are essentially identical—compare Equation 1.33 with 1.34 and Equation 1.37 with 1.38. This means that, if the NTF is designed for the desired noise-shaping behavior, both topologies also fix the STF function, as ![]() [41].6

[41].6

If a certain degree of freedom is desired in designing both the modulator NTF and STF, the topology in Figure 1.20 can be used, which is a chain of integrators with distributed feedback and distributed feed-forward input paths [43]. In this architecture, the zeros of STF can be fixed with coefficients ![]() without affecting the pole placement, so both STF and NTF can be separately optimized to some extent [41].7

without affecting the pole placement, so both STF and NTF can be separately optimized to some extent [41].7

Figure 1.20 High-order single-loop ![]() M with distributed feedback and distributed feed-forward input paths.

M with distributed feedback and distributed feed-forward input paths.

1.5 Cascade  Modulators

Modulators

As discussed in Section 1.4.2, stability problems arising from implementing a high-order NTF with a single-loop ![]() M can be circumvented with adequate scaling coefficients, but they result in a significant decrease of the DR compared with an ideal

M can be circumvented with adequate scaling coefficients, but they result in a significant decrease of the DR compared with an ideal ![]() M. An alternative approach to obtain a high-order noise shaping while avoiding instabilities is found in the so-called cascade

M. An alternative approach to obtain a high-order noise shaping while avoiding instabilities is found in the so-called cascade ![]() Ms, also known as multiloop

Ms, also known as multiloop ![]() Ms or multistage noise shaping (MASH)

Ms or multistage noise shaping (MASH) ![]() Ms [45–48]. Their architecture is illustrated in Figure 1.21 and consists of

Ms [45–48]. Their architecture is illustrated in Figure 1.21 and consists of ![]() stages of

stages of ![]() modulators, in which each stage remodulates a scaled version of the quantization error generated in the preceding one. The outputs of the cascaded stages

modulators, in which each stage remodulates a scaled version of the quantization error generated in the preceding one. The outputs of the cascaded stages ![]() are conveniently processed in digital domain to cancel out at the overall

are conveniently processed in digital domain to cancel out at the overall ![]() M output

M output ![]() all the quantization errors, but that of the back-end stage. In addition, the latter quantization error appears at the cascade output shaped with an order

all the quantization errors, but that of the back-end stage. In addition, the latter quantization error appears at the cascade output shaped with an order ![]() equal to the summation of those of the cascaded stages (

equal to the summation of those of the cascaded stages (![]() ). Unconditionally, stable high-order shaping can thus be obtained if only first- and second-order

). Unconditionally, stable high-order shaping can thus be obtained if only first- and second-order ![]() Ms are cascaded (

Ms are cascaded (![]() ), because all feedback loops are local to the low-order

), because all feedback loops are local to the low-order ![]() stages and there is no interstage feedback. Therefore, the performance of a multistage

stages and there is no interstage feedback. Therefore, the performance of a multistage ![]() M is similar to that of an ideal high-order, single-loop with no stability issues.8

M is similar to that of an ideal high-order, single-loop with no stability issues.8

Figure 1.21 General topology of an ![]() -stage cascade

-stage cascade ![]() modulator.

modulator.

The operation principle of cascade ![]() Ms can be easily understood considering an exemplary two-stage cascade. Using linear analysis, the stages output can be expressed in the

Ms can be easily understood considering an exemplary two-stage cascade. Using linear analysis, the stages output can be expressed in the ![]() -domain as

-domain as

1.39 ![]()

where the input of the ![]() stages are given by

stages are given by ![]() and

and ![]() , and

, and ![]() and

and ![]() stand for the quantization error of the respective stage. The overall modulator output after the digital cancelation logic (DCL) can thus be obtained from the expressions above as

stand for the quantization error of the respective stage. The overall modulator output after the digital cancelation logic (DCL) can thus be obtained from the expressions above as

1.40 ![]()

where ![]() ,

, ![]() , and

, and ![]() stand for the overall cascade transfer functions for the input signal and the quantization errors, respectively

stand for the overall cascade transfer functions for the input signal and the quantization errors, respectively

Note that, if the signal processing in the DCL matches part of the signal processing in the analog side, Equation 1.41 yields

1.42

so that the first-stage quantization error is canceled at the overall output and that of the second stage is attenuated with an order equal to the summation of both stages' orders (![]() ).

).

For the generic ![]() -stage cascade

-stage cascade ![]() M in Figure 1.21, assuming

M in Figure 1.21, assuming ![]() and

and ![]() in the individual stages, the overall modulator output thus yields

in the individual stages, the overall modulator output thus yields

under the required matching between the analog processing in the ![]() stages and the DCL. The in-band quantization noise of the cascade is then given by

stages and the DCL. The in-band quantization noise of the cascade is then given by

where ![]() stands for the quantization step employed in the last

stands for the quantization step employed in the last ![]() stage. Note from Equation 1.44 that only the interstage scaling coefficients

stage. Note from Equation 1.44 that only the interstage scaling coefficients ![]() , which prevent a premature overload of the subsequent stages, decrease the performance below that of an ideal

, which prevent a premature overload of the subsequent stages, decrease the performance below that of an ideal ![]() th order

th order ![]() M. Typical values of

M. Typical values of ![]() are between 2 and 4 if single-bit quantization is employed, which lead to a reduction in the ideally attainable DR of only 6–12 dB (1–2 bit). These performance losses are inherent to cascade

are between 2 and 4 if single-bit quantization is employed, which lead to a reduction in the ideally attainable DR of only 6–12 dB (1–2 bit). These performance losses are inherent to cascade ![]() Ms, but they are significantly smaller than those resulting from optimized high-order single loops. In addition, they are independent of OSR.

Ms, but they are significantly smaller than those resulting from optimized high-order single loops. In addition, they are independent of OSR.

The aforementioned benefits of cascade ![]() Ms have favored the development of a large number of different topologies:

Ms have favored the development of a large number of different topologies:

- 2-1

M, which stands for a third-order two-stage

M, which stands for a third-order two-stage  M built up with a second-order stage followed by a first-order one [46]. It is also known as a SOFO cascade—for second-order first-order.

M built up with a second-order stage followed by a first-order one [46]. It is also known as a SOFO cascade—for second-order first-order. - 2-2

M, which represents a fourth-order cascade built up with two second-order stages [49, 50].

M, which represents a fourth-order cascade built up with two second-order stages [49, 50]. - 2-1-1

M, which stands for a fourth-order, third-stage cascade [25].

M, which stands for a fourth-order, third-stage cascade [25]. - 2-2-1

M [51].

M [51]. - 2-1-1-1

M [52].

M [52]. - 2-2-2

M [53].

M [53]. - etc.

Note from the cascade topologies above that the first stage is usually a second-order ![]() M and that first-order

M and that first-order ![]() Ms are avoided at the front end [48]. The reason for that is twofold. First, the quantization error from the first stage would be only first-order shaped and noise leakages would be larger. Second, the tonal behavior of a first-order, first stage would menace the performance of the cascade. In addition, although low-order

Ms are avoided at the front end [48]. The reason for that is twofold. First, the quantization error from the first stage would be only first-order shaped and noise leakages would be larger. Second, the tonal behavior of a first-order, first stage would menace the performance of the cascade. In addition, although low-order ![]() stages are most frequently cascaded, 3-1 and 3-2

stages are most frequently cascaded, 3-1 and 3-2 ![]() Ms have also been reported [54, 55].

Ms have also been reported [54, 55].

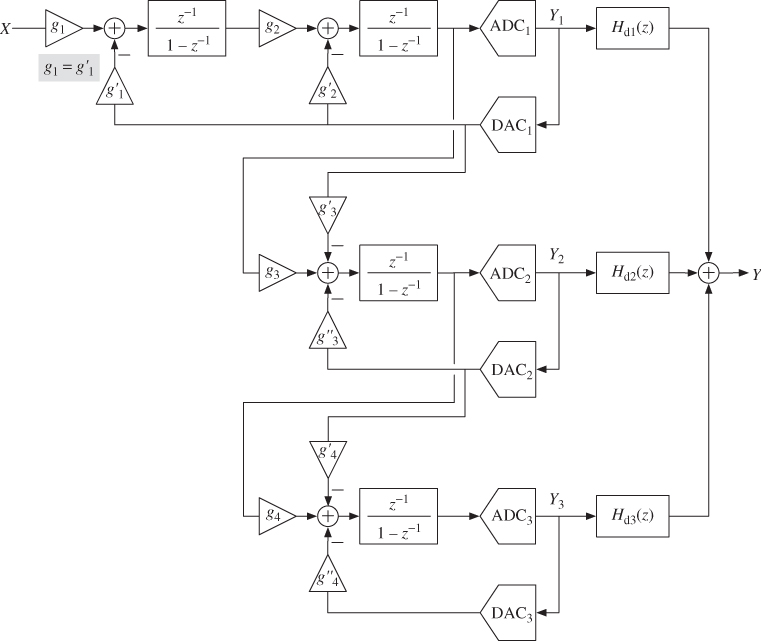

Figure 1.22 illustrates the block diagram of a 2-1-1 cascade, in which coefficients ![]() represent the in-loop integrator scaling factors, whereas coefficients

represent the in-loop integrator scaling factors, whereas coefficients ![]() and

and ![]() determine the interstage scaling factors. The first stage performs as an ideal second-order

determine the interstage scaling factors. The first stage performs as an ideal second-order ![]() M and the second and third stages as an ideal first-order

M and the second and third stages as an ideal first-order ![]() M under the assumptions

M under the assumptions

where ![]() stands for the gain of the quantizer in the

stands for the gain of the quantizer in the ![]() th

th ![]() stage. The matching required between the signal processing in the

stage. The matching required between the signal processing in the ![]() stages and the digital processing in the DCL leads to

stages and the digital processing in the DCL leads to

for a complete cancelation of the first- and second-stage quantization errors at the cascade output. For the sake of completeness, Figure 1.23 shows an alternative representation of the 2-1-1 ![]() M according to the notation in [12, 19]. Proceeding in a similar way as done in Figure 1.16 for the second-order

M according to the notation in [12, 19]. Proceeding in a similar way as done in Figure 1.16 for the second-order ![]() M, both notations can be easily connected with the equalities:

M, both notations can be easily connected with the equalities:

1.47

Figure 1.22 Block diagram of a 2-1-1 cascade ![]() modulator using the notation in [8, 9]. The relations in Equations 1.45 and 1.46 must be fulfilled for the correct operation of the cascade.

modulator using the notation in [8, 9]. The relations in Equations 1.45 and 1.46 must be fulfilled for the correct operation of the cascade.

Figure 1.23 Alternative representation of the 2-1-1 ![]() M in Figure 1.22 using the notation in [12, 19]. Modulator coefficients

M in Figure 1.22 using the notation in [12, 19]. Modulator coefficients ![]() are mapped onto integrator input coefficients

are mapped onto integrator input coefficients ![]() , which are closer to the circuit-level implementation.

, which are closer to the circuit-level implementation.

The value of the analog coefficients in the 2-1-1 ![]() M need to be selected to fulfill the relations in Equation 1.45, but many different sets of values can do the work. On top of that, extra considerations are in practice taken into account, such as the following:

M need to be selected to fulfill the relations in Equation 1.45, but many different sets of values can do the work. On top of that, extra considerations are in practice taken into account, such as the following:

- Minimizing the resulting loss of performance in comparison to an ideal

M.

M. - Maximizing the modulator overload level to achieve a high-peak SNR.

- Simplifying the circuit-level implementation of the set of analog coefficients. For SC-

Ms, this means taking into account practical capacitor ratios using unit elements, enabling capacitor sharing within the integrators, reducing the total number of unit capacitors for area saving, etc.

Ms, this means taking into account practical capacitor ratios using unit elements, enabling capacitor sharing within the integrators, reducing the total number of unit capacitors for area saving, etc. - Minimizing the integrator output swing requirements, especially in case of a low-voltage supply.

- Simplifying the implementation of the DCL. To that purpose, power of two coefficients are often preferred for

,

,  ,

,  , and

, and  —see Equation 1.46 —in order to use shift registers only.

—see Equation 1.46 —in order to use shift registers only.

Table 1.2 illustrates some sets of analog coefficients reported for the 2-1-1 single-bit ![]() M, together with their main resulting features. Optimized coefficients for some other cascade topologies can be found in [8].

M, together with their main resulting features. Optimized coefficients for some other cascade topologies can be found in [8].

Table 1.2 Comparison of some sets of coefficients reported for the 2-1-1 single-bit ![]() M

M

1.6 Multibit  Modulators

Modulators

As discussed in Section 1.2.4, the DR of a ![]() M can be enhanced if the resolution of the embedded quantizer is increased. The main advantages of resorting to multibit

M can be enhanced if the resolution of the embedded quantizer is increased. The main advantages of resorting to multibit ![]() modulators are as follows:

modulators are as follows:

- The in-band quantization noise power is roughly reduced 6 dB per additional bit in the embedded quantizer, thanks to the smaller quantization step

.

. - Internal nonlinearities are weaker in multibit

Ms than in their single-bit counterparts. The quantizer operation better fits the additive white noise model in Section 1.1.3 and the phenomena caused by nonlinear dynamics are less evident.

Ms than in their single-bit counterparts. The quantizer operation better fits the additive white noise model in Section 1.1.3 and the phenomena caused by nonlinear dynamics are less evident. - For a given order in the loop filter, the stability properties of multibit

Ms are better than for single-bit

Ms are better than for single-bit  Ms [57].

Ms [57].

These benefits suggest that, for a targeted performance of the ![]() M, multibit quantization can be traded for noise shaping and/or oversampling. Indeed, multibit

M, multibit quantization can be traded for noise shaping and/or oversampling. Indeed, multibit ![]() Ms are often employed in broadband applications to compensate for the limited OSR. Nevertheless, multibit quantizers also have important drawbacks that may counter the former advantages:

Ms are often employed in broadband applications to compensate for the limited OSR. Nevertheless, multibit quantizers also have important drawbacks that may counter the former advantages:

- They require more analog circuitry and are more difficult to design than single-bit ones.

- Contrary to 1-bit quantizers, which are intrinsically

linear because only two levels are used for quantization, multibit quantizers exhibit in practice some nonlinearities in their transfer characteristic, mostly due to device mismatching, which significantly influence the

M performance.

M performance.

1.6.1 Influence of Multibit DAC Errors