Chapter 4

Circuit-Level Design, Implementation, and Verification

The behavioral modeling and simulation techniques described in Chapter 3 can be used for the high-level synthesis and verification of ![]() Ms so that the modulator-level specifications are efficiently mapped onto building-block (circuit-level) specifications. Thus, at this stage of the design cycle, the modulator is still modeled at system level, but the electrical performance parameters of all

Ms so that the modulator-level specifications are efficiently mapped onto building-block (circuit-level) specifications. Thus, at this stage of the design cycle, the modulator is still modeled at system level, but the electrical performance parameters of all ![]() M circuit elements (switches, capacitors, amplifiers, transconductors, comparators, etc.) have been already derived from the high-level sizing process. Those parameters are in turn the circuit-level specifications, which constitute the start point for the electrical (transistor-level) and physical design process of the modulator. This process—conceptually illustrated in Figure 4.1—comprises a number of successive steps in which the initial behavioral-model diagram of the modulator is transformed into a circuit schematic—initially implemented with macromodels and finally with transistors—afterward into a layout, and finally into a chip implementation for experimental verification in a laboratory.

M circuit elements (switches, capacitors, amplifiers, transconductors, comparators, etc.) have been already derived from the high-level sizing process. Those parameters are in turn the circuit-level specifications, which constitute the start point for the electrical (transistor-level) and physical design process of the modulator. This process—conceptually illustrated in Figure 4.1—comprises a number of successive steps in which the initial behavioral-model diagram of the modulator is transformed into a circuit schematic—initially implemented with macromodels and finally with transistors—afterward into a layout, and finally into a chip implementation for experimental verification in a laboratory.

Figure 4.1 Conceptual step-by-step design flow of ![]() Ms.

Ms.

This chapter gives some design issues and practical recipes to complete the design flow illustrated in Figure 4.1. Section 4.1 deals with macromodel implementation of ![]() Ms as an essential design stage to relate behavioral-level models with circuit-level description. Section 4.2 describes how to include circuit noise in electrical-level simulations of

Ms as an essential design stage to relate behavioral-level models with circuit-level description. Section 4.2 describes how to include circuit noise in electrical-level simulations of ![]() Ms and Section 4.3 shows how to process the modulator output data extracted from electrical simulations in SPICE-like simulators, in order to characterize the performance of

Ms and Section 4.3 shows how to process the modulator output data extracted from electrical simulations in SPICE-like simulators, in order to characterize the performance of ![]() Ms. Section 4.4 moves down to the transistor-level implementation, giving a number of practical design guidelines and describing diverse simulation test benches to properly design and characterize the performance of basic

Ms. Section 4.4 moves down to the transistor-level implementation, giving a number of practical design guidelines and describing diverse simulation test benches to properly design and characterize the performance of basic ![]() M building blocks. Other auxiliary circuits needed to implement

M building blocks. Other auxiliary circuits needed to implement ![]() Ms are discussed in Section 4.5. Finally, Sections 4.6 and 4.7 deal with some of the most important design issues related to the layout, prototyping, and testing of high-performance

Ms are discussed in Section 4.5. Finally, Sections 4.6 and 4.7 deal with some of the most important design issues related to the layout, prototyping, and testing of high-performance ![]() Ms.

Ms.

4.1 Macromodeling  Ms

Ms

The transformation from a behavioral-level description into a circuit schematic as conceptually depicted in Figure 4.1 is carried out in several steps. Thus, at the early stages of the design cycle, hardware description languages (HDL), such as Verilog-A [1], and macromodels are used for representing different modulator building blocks. These models include main circuit error limitations derived from system-level behavioral models, for instance implemented in SIMSIDES. These models are progressively replaced by transistor-level implementations as the different ![]() M blocks are designed. This way, the performance of the modulator is analyzed and checked at different stages of the design cycle by combining the impact of those subcircuits which have been designed at the transistor level with those ones which have not been sized yet.

M blocks are designed. This way, the performance of the modulator is analyzed and checked at different stages of the design cycle by combining the impact of those subcircuits which have been designed at the transistor level with those ones which have not been sized yet.

This section explains how to use macromodels to implement ![]() Ms at the circuit level in electrical simulators. Most important building-block equivalent circuits are derived and some examples are shown to illustrate their use.

Ms at the circuit level in electrical simulators. Most important building-block equivalent circuits are derived and some examples are shown to illustrate their use.

4.1.1 SC Integrator Macromodel

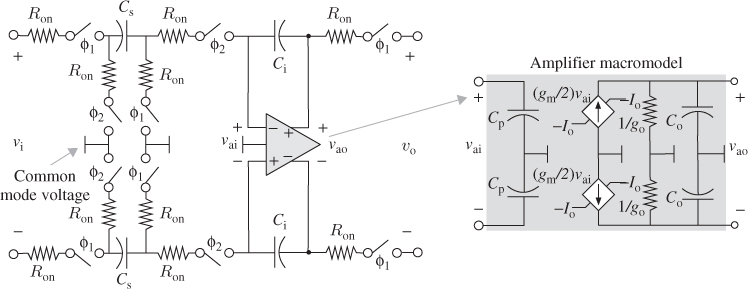

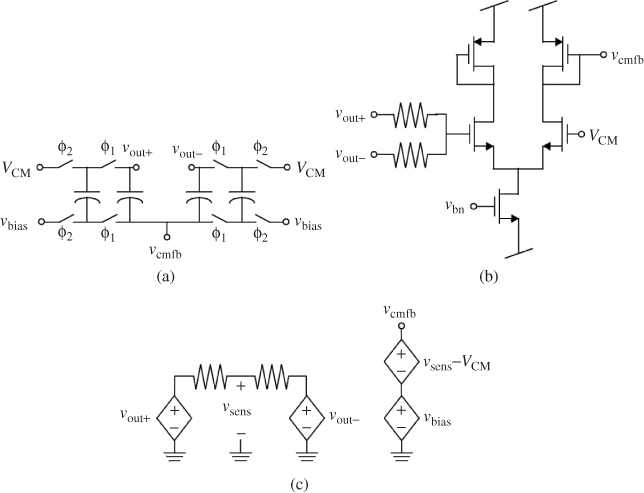

Figure 4.2 shows a single-ended equivalent circuit frequently used for simulating FE SC integrators with macromodels. The corresponding macromodel for a fully-differential implementation is shown in Figure 4.3 [2]. Both equivalent circuits use ideal capacitors, whereas the switches and the OTA include nonideal circuit effects as discussed subsequently.

Figure 4.2 Macromodel of a single-ended FE SC integrator.

Figure 4.3 Macromodel of a fully-differential FE SC integrator.

Switch Macromodel

As illustrated in Figure 4.2, switches are usually modeled as a linear switch on-resistance ![]() in series with an ideal switch, which is controlled by the corresponding clock phase, either

in series with an ideal switch, which is controlled by the corresponding clock phase, either ![]() or

or ![]() . Note that the switch model in SPICE-like simulators consists of a highly nonlinear resistor whose resistance depends on the control clock-phase voltage

. Note that the switch model in SPICE-like simulators consists of a highly nonlinear resistor whose resistance depends on the control clock-phase voltage ![]() as follows:

as follows:

4.1

where ![]() stands for the switch off-resistance that is ideally

stands for the switch off-resistance that is ideally ![]() , and

, and ![]() stands for a threshold voltage that determines if the switch is either closed (on) or open (off). In practice, an almost ideal switch can be modeled in electrical simulators by setting

stands for a threshold voltage that determines if the switch is either closed (on) or open (off). In practice, an almost ideal switch can be modeled in electrical simulators by setting ![]() and

and ![]() just high/low enough to be negligible with respect to other circuit elements [3]. For instance, typical values of

just high/low enough to be negligible with respect to other circuit elements [3]. For instance, typical values of ![]() are chosen to be in the order of

are chosen to be in the order of ![]() , while a very high value of

, while a very high value of ![]() is considered, typically in the order of

is considered, typically in the order of ![]() .1

.1

Instead of using this simple model, a macromodel that is closer to the transistor-level topology implementation can be used. For instance, let us consider a CMOS switch similar to those shown in the sampling circuit of Figure 2.21. This switch is made up of a pMOS switch and an nMOS switch connected in parallel. Figure 4.4 shows an equivalent circuit that takes into account the on-resistance of both MOST switches as well as their associated parasitic capacitances, denoted as ![]() . Note that this macromodel keeps the symmetry of the original MOST-based circuit.

. Note that this macromodel keeps the symmetry of the original MOST-based circuit.

Figure 4.4 Macromodel of a CMOS switch.

OTA Macromodel

The OTA circuit is modeled by a well-known single-pole amplifier where ![]() ,

, ![]() , and

, and ![]() denote, respectively, the transconductance, output conductance, and output capacitance. In addition, the voltage-controlled current source used for modeling the OTA transconductance has two saturation limits,

denote, respectively, the transconductance, output conductance, and output capacitance. In addition, the voltage-controlled current source used for modeling the OTA transconductance has two saturation limits, ![]() . These limits model the minimum and maximum output currents provided by the OTA. This way, this equivalent circuit takes into account the finite DC gain, GB, and SR limitations of the OTA, respectively given by

. These limits model the minimum and maximum output currents provided by the OTA. This way, this equivalent circuit takes into account the finite DC gain, GB, and SR limitations of the OTA, respectively given by

4.2 ![]()

Note that real values of GB and SR deviate in practice from the above expressions because of the effect caused by bottom-plate parasitic capacitances, denoted as ![]() in Figure 4.3, as well as the capacitive load due to the SC network connected at the output of the integrator.

in Figure 4.3, as well as the capacitive load due to the SC network connected at the output of the integrator.

4.1.2 CT Integrator Macromodel

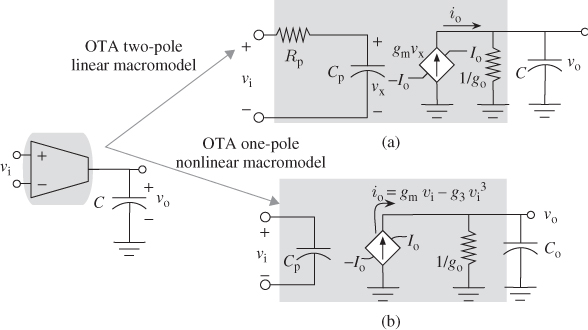

The equivalent circuit normally used for the macromodel of CT integrators is based on a one-pole (or two-pole) OTA model together with the additional circuit elements that are required to implement the integrator topology, that is, Gm-C, active-RC, etc. [5].

Active-RC Integrators

Figure 4.5 shows a simple macromodel circuit commonly used for active-RC implementations. In this example, a one-pole OTA model similar to that shown in Figures 4.2 and 4.3 is used, although higher dynamics can be implemented if necessary. In a similar way to SC integrators, parasitic and load capacitances of the OTA can also be considered.

Figure 4.5 Active-RC integrator macromodel: (a) single-ended schematic and (b) fully-differential schematic.

Gm-C Integrators

On the basis of the same OTA macromodel circuit, Gm-C integrators can be modeled by the equivalent circuit shown in Figure 4.6a, which includes a second pole modeled by the time constant ![]() . In this case, the

. In this case, the ![]() -domain transfer function of the integrator is given by

-domain transfer function of the integrator is given by

4.3 ![]()

Figure 4.6 Gm-C integrator macromodel: (a) two-pole linear model and (b) one-pole weakly nonlinear model.

4.1.3 Nonlinear OTA Transconductor

The OTA macromodel considered in previous sections assumed a linear model for the transconductance ![]() and an output current saturation

and an output current saturation ![]() . In practice, the transconductor of the OTA is assumed to be weakly nonlinear, such that its static output current

. In practice, the transconductor of the OTA is assumed to be weakly nonlinear, such that its static output current ![]() is related to the OTA input voltage

is related to the OTA input voltage ![]() as follows [6]:

as follows [6]:

where ![]() denotes the sign function of

denotes the sign function of ![]() ,

, ![]() is the third-order nonlinear coefficient of the transconductor, IIP3 stands for the input-referred third-order intercept point, and

is the third-order nonlinear coefficient of the transconductor, IIP3 stands for the input-referred third-order intercept point, and ![]() is the maximum output current provided by the transconductor. It can be shown from Equation 4.4 that IIP3 and

is the maximum output current provided by the transconductor. It can be shown from Equation 4.4 that IIP3 and ![]() are related to

are related to ![]() and

and ![]() as follows:

as follows:

4.5 ![]()

4.6 ![]()

Figure 4.6b shows an equivalent circuit for the OTA macromodel that includes the weakly nonlinear transconductance element. Note that this equivalent circuit can be easily modeled in SPICE-like simulators using nonlinear voltage-controlled current sources [3]. Moreover, other sources of nonlinearities associated with the voltage dependency of integrated resistors and capacitors can also be included in the integrator macromodels using signal-dependent voltage/current sources. However, this kind of nonlinear effects are more accurately considered in the simulation when the circuit is modeled at device level, that is, taking into account the device models provided by the foundry, such as unsalicided polysilicon resistors or MiM capacitors.

4.1.4 Embedded Flash ADC Macromodel

Multibit/multilevel ADCs required to implement the quantizers embedded in ![]() Ms are typically implemented using a well-known flash architecture. This kind of ADCs is made up of a bank of comparators that compare the quantizer input signal (i.e., the output of the integrator connected to the quantizer) with a set of reference voltages generated in a resistor ladder [7]. These reference voltages correspond to the transition points between the different adjacent quantization intervals [8].

Ms are typically implemented using a well-known flash architecture. This kind of ADCs is made up of a bank of comparators that compare the quantizer input signal (i.e., the output of the integrator connected to the quantizer) with a set of reference voltages generated in a resistor ladder [7]. These reference voltages correspond to the transition points between the different adjacent quantization intervals [8].

As an illustration, Figure 4.7a shows the fully-differential schematic of a trilevel flash ADC, which is made up of two comparators and a resistive divider. The latter is made up of four unit resistors ![]() , which are connected in series between the negative reference voltage

, which are connected in series between the negative reference voltage ![]() and the positive reference voltage

and the positive reference voltage ![]() . In this example, there are two transition points,

. In this example, there are two transition points, ![]() and

and ![]() , in the quantizer differential characteristic illustrated in Figure 4.7b, which correspond to the differential tabs of the resistor ladder in Figure 4.7a. Thus, the quantizer input

, in the quantizer differential characteristic illustrated in Figure 4.7b, which correspond to the differential tabs of the resistor ladder in Figure 4.7a. Thus, the quantizer input ![]() is compared with

is compared with ![]() and

and ![]() , in the first and the second comparator, respectively. The thermometer code generated at the comparators outputs is converted into a 1-of-3 code (

, in the first and the second comparator, respectively. The thermometer code generated at the comparators outputs is converted into a 1-of-3 code (![]() ) using three AND gates.

) using three AND gates.

Figure 4.7 Macromodeling multilevel flash ADCs: (a) conceptual schematic of a trilevel flash ADC and (b) static differential transfer characteristic.

Figure 4.8 Verilog-A code used for simulating comparators in quantizer macromodels [10, 11].

The circuit shown in Figure 4.7a can be used for simulating ![]() Ms with macromodels. To this end, resistors are considered ideal circuit elements,2 while comparators and AND gates are modeled using Verilog-A. As an illustration, Figure 4.8 shows the Verilog-A code used for modeling the comparators in Figure 4.7. The model—based on the Open Verilog International (OVI) language reference manual [10, 11]—is quite simple and includes the input offset. The comparison only takes place when the clock signal named enable is in the high state. The static input–output transfer characteristic is computed by using an hyperbolic tangent function (tanh), which is scaled by a parameter named comp_slope. The latter determines the static resolution of the comparator by modifying the voltage gain around the input offset voltage, modeled by sigin_offset parameter.

Ms with macromodels. To this end, resistors are considered ideal circuit elements,2 while comparators and AND gates are modeled using Verilog-A. As an illustration, Figure 4.8 shows the Verilog-A code used for modeling the comparators in Figure 4.7. The model—based on the Open Verilog International (OVI) language reference manual [10, 11]—is quite simple and includes the input offset. The comparison only takes place when the clock signal named enable is in the high state. The static input–output transfer characteristic is computed by using an hyperbolic tangent function (tanh), which is scaled by a parameter named comp_slope. The latter determines the static resolution of the comparator by modifying the voltage gain around the input offset voltage, modeled by sigin_offset parameter.

4.1.5 Feedback DAC Macromodel

There are essentially two types of feedback DAC circuits used in ![]() Ms, namely SC DACs and current mode, also named current-steering (CS) DACs [12]. The former are mainly used in SC-

Ms, namely SC DACs and current mode, also named current-steering (CS) DACs [12]. The former are mainly used in SC-![]() Ms, although they are used also in some CT-

Ms, although they are used also in some CT-![]() Ms, specifically those implemented with active-RC integrators intended for low-frequency applications [13]. In contrast, switched-current3 or current-steering feedback DACs are commonly used in wideband CT-

Ms, specifically those implemented with active-RC integrators intended for low-frequency applications [13]. In contrast, switched-current3 or current-steering feedback DACs are commonly used in wideband CT-![]() Ms, particularly—but not only—those based on Gm-C loop-filter implementations.

Ms, particularly—but not only—those based on Gm-C loop-filter implementations.

As an example of SC DACs, let us consider again the trilevel ADC shown in Figure 4.7a. The 1-of-3 coded digital output ![]() is fed back to the

is fed back to the ![]() M loop-filter SC integrators by using three AND gates as illustrated in Figure 4.9. In this case, the macromodel of the DAC is simply based on the Verilog-A models of the AND gates as well as the macromodel circuits used for the switches described in Section 4.1.1.

M loop-filter SC integrators by using three AND gates as illustrated in Figure 4.9. In this case, the macromodel of the DAC is simply based on the Verilog-A models of the AND gates as well as the macromodel circuits used for the switches described in Section 4.1.1.

Figure 4.9 Macromodel of a trilevel SC DAC connected to an SC FE integrator within a ![]() M loop filter. Note that different SC branches, using two different sampling capacitors

M loop filter. Note that different SC branches, using two different sampling capacitors ![]() and

and ![]() , are used in this model. However, there are many situations in practice where a single SC branch is shared by both the input signal and the feedback DAC as will be shown later in this chapter.

, are used in this model. However, there are many situations in practice where a single SC branch is shared by both the input signal and the feedback DAC as will be shown later in this chapter.

Figure 4.10 Illustrating the macromodel of a trilevel current-steering DAC connected to a Gm-C integrator within a ![]() M loop filter.

M loop filter.

Following the same philosophy, a macromodel circuit that can be used for current-steering DACs is based on simple macromodels of current sources and switches.4 As an illustration, Figure 4.10 shows the macromodel of a fully-differential trilevel current-steering NRZ DAC. It consists of a set of current sources controlled, through switches, by a 1-of-3 coded digital data (![]() ). As will be discussed later in this chapter, the ideal operation of the current sources, and consequently the current-steering DAC, is degraded in practice by mismatch errors, finite output impedance (of the current sources), thermal gradients, etc. The majority of these errors, such as mismatch and technology-related errors, require doing a large number of simulations in order to evaluate their impact on the performance of the modulator. For that reason, these errors are usually considered at system-level behavioral models, for instance implemented in MATLAB/SIMULINK as described in Chapter 3. Some other nonidealities, such as output impedance of current sources, which also affect the dynamic operation of the modulator loop filter, can be easily macromodeled by simply including an output resistance in parallel with each unit (or reference) current source, as illustrated in Figure 4.10.

). As will be discussed later in this chapter, the ideal operation of the current sources, and consequently the current-steering DAC, is degraded in practice by mismatch errors, finite output impedance (of the current sources), thermal gradients, etc. The majority of these errors, such as mismatch and technology-related errors, require doing a large number of simulations in order to evaluate their impact on the performance of the modulator. For that reason, these errors are usually considered at system-level behavioral models, for instance implemented in MATLAB/SIMULINK as described in Chapter 3. Some other nonidealities, such as output impedance of current sources, which also affect the dynamic operation of the modulator loop filter, can be easily macromodeled by simply including an output resistance in parallel with each unit (or reference) current source, as illustrated in Figure 4.10.

4.1.6 Examples of  M Macromodels

M Macromodels

To conclude this section, a couple of examples are described to illustrate the use of the macromodels for the implementation of ![]() Ms. The first one is based on SC circuits while the second one is implemented with active-RC circuits. In both cases, the well-known, single-loop, second-order

Ms. The first one is based on SC circuits while the second one is implemented with active-RC circuits. In both cases, the well-known, single-loop, second-order ![]() M is used as a demonstration vehicle, considering an embedded trilevel quantizer.

M is used as a demonstration vehicle, considering an embedded trilevel quantizer.

SC Second-Order Example

Figure 4.11 shows the conceptual schematic of the second-order SC-![]() M under study, which includes a trilevel embedded quantizer. The values of capacitors used are highlighted in the figure. The circuit elements forming this modulator—that is switches, amplifiers, a flash (trilevel) ADC, and an SC (trilevel) DAC—can be implemented using the macromodels described in previous section.

M under study, which includes a trilevel embedded quantizer. The values of capacitors used are highlighted in the figure. The circuit elements forming this modulator—that is switches, amplifiers, a flash (trilevel) ADC, and an SC (trilevel) DAC—can be implemented using the macromodels described in previous section.

Figure 4.11 Conceptual schematic of a second-order SC-![]() M with a trilevel embedded quantizer.

M with a trilevel embedded quantizer.

Figure 4.12 shows the schematic of the modulator in Figure 4.11 implemented in Cadence Design FrameWork, using Cadence Virtuoso Schematic. In this example, ideal clock phases (implemented with ideal voltage sources) are used for the sake of simplicity. This is a common practice at the very beginning of the design phase as the use of a clock-phase generator circuit—discussed later in this chapter—slows down the simulations unnecessarily.

Figure 4.12 Implementation of the modulator in Figure 4.11 using Cadence Virtuoso Schematics.

Note that each modulator building block in Figure 4.12 uses a suitable schematic symbol. This is very useful in practice to clearly identify the different parts of the modulator and to establish an appropriate hierarchic partitioning that allows us to systematize the design from a top-down/bottom-up approach. This way, designers can move through the modulator hierarchy, using the most convenient schematic representation according to the circuit part being analyzed. As an illustration, Figure 4.13 shows the macromodel of the first integrator in Figure 4.12, where the symbols for the switches, capacitors, and opamps are clearly identified.

Figure 4.13 Schematic of the SC first integrator of Figure 4.12.

As discussed earlier in this chapter, the use of even ideal macromodels allows designers to clearly define the electrical representation of a ![]() M circuit, including all their nodes and branches. These macromodels can be progressively replaced by their transistor-level implementations as the different building blocks are being sized. This is something that can be done very easily in some circuit design environments, such as in Cadence Design Framework. Figure 4.14 shows how to change the type of implementation, often referred to as view. Note that four different cell view names are available in this example: symbol (which is the highest abstraction level), macromodel, schematic (transistor-level), and layout.

M circuit, including all their nodes and branches. These macromodels can be progressively replaced by their transistor-level implementations as the different building blocks are being sized. This is something that can be done very easily in some circuit design environments, such as in Cadence Design Framework. Figure 4.14 shows how to change the type of implementation, often referred to as view. Note that four different cell view names are available in this example: symbol (which is the highest abstraction level), macromodel, schematic (transistor-level), and layout.

Figure 4.14 Illustrating the selection of a circuit view name in Cadence Design FrameWork.

As an illustration, Figure 4.15 shows the macromodel of different parts of the SC integrator in Figure 4.13. Figure 4.15a shows the macromodel of the fully-differential amplifier and Figure 4.15b depicts the macromodel of a CMOS switch. In both cases, the different model parameters can be set according to the building-block specifications derived from behavioral simulations, for instance using SIMSIDES as described in Chapter 3.

Figure 4.15 Illustrating the macromodel implementation of different circuit elements of SC integrators in Cadence Design FrameWork: (a) fully-differential amplifier and (b) switch.

Second-Order Active-RC  M

M

Figure 4.16 shows the conceptual schematic of a second-order active-RC ![]() M with trilevel embedded quantizer. For the sake of simplicity, the modulator does not include any excess-loop delay cancellation technique. The values and expressions of the resistances, capacitances, and feedback DAC currents are shown in the figure, where

M with trilevel embedded quantizer. For the sake of simplicity, the modulator does not include any excess-loop delay cancellation technique. The values and expressions of the resistances, capacitances, and feedback DAC currents are shown in the figure, where ![]() denotes the FS reference voltage of the modulator.

denotes the FS reference voltage of the modulator.

Figure 4.16 Conceptual schematic of a second-order active-RC ![]() M with a trilevel embedded quantizer and CS feedback DACs.

M with a trilevel embedded quantizer and CS feedback DACs.

The circuit shown in Figure 4.16 can be modeled very easily using the macromodel circuits described in previous sections. Figure 4.17 shows an example implemented in Cadence Virtuoso schematic editor, highlighting the main parts of the circuit. The opamp included in the active-RC model (Figure 4.17b) uses the macromodel described in Figure 4.5b. In this example, the trilevel quantization is implemented as illustrated in Figure 4.18. The ADC, depicted in Figure 4.18a, is modeled as shown in Figure 4.7b. However, for the sake of simplicity, the current-steering DAC, shown in Figure 4.18b, is modeled by two ideal voltage-controlled current sources, which emulate the ideal switches connected in series with the reference currents (Figure 4.10).

Figure 4.17 Schematic of the modulator in Figure 4.16 implemented in Cadence Virtuoso schematic editor: (a) modulator and (b) active-RC integrator.

Figure 4.18 Illustrating the macromodel implementation of a trilevel quantizer in Cadence Virtuoso schematic editor: (a) flash ADC and (b) current-steering DAC.

4.2 Including Noise in Transient Electrical Simulations of  Ms

Ms

As stated in Chapter 2, circuit noise is an ultimate limiting factor degrading the performance of ![]() Ms. Therefore, it is essential to take into account this effect in all steps of the design flow. At system level, accurate models described in Chapter 2 can be incorporated in behavioral simulations, for instance, using SIMSIDES as detailed in Chapter 3. At electrical level, however, the majority of SPICE-like simulators do not include noise sources in the transient analysis,5 which makes their analysis at transistor level more complicated.

Ms. Therefore, it is essential to take into account this effect in all steps of the design flow. At system level, accurate models described in Chapter 2 can be incorporated in behavioral simulations, for instance, using SIMSIDES as detailed in Chapter 3. At electrical level, however, the majority of SPICE-like simulators do not include noise sources in the transient analysis,5 which makes their analysis at transistor level more complicated.

This section describes a methodology that allows designers to do electrical (transistor-level) simulations of ![]() Ms including noise sources. The method—based on generating a noisy data sequence in MATLAB and then injecting this data sequence in the electrical simulation—can be used in most SPICE-like simulators such as PSPICE and HSPICE [4, 16].

Ms including noise sources. The method—based on generating a noisy data sequence in MATLAB and then injecting this data sequence in the electrical simulation—can be used in most SPICE-like simulators such as PSPICE and HSPICE [4, 16].

4.2.1 Generating and Injecting Noise Data Sequences in HSPICE

Let us consider the simple SC circuit shown in Figure 4.19a, in which a noise voltage source ![]() is sampled by an ideal switch

is sampled by an ideal switch ![]() and stored on capacitor

and stored on capacitor ![]() . This circuit can be simulated using the HSPICE netlist shown in Figure 4.19b. In this example

. This circuit can be simulated using the HSPICE netlist shown in Figure 4.19b. In this example ![]() pF, the switch off/on-resistances used in the ideal switch model are, respectively,

pF, the switch off/on-resistances used in the ideal switch model are, respectively, ![]() and

and ![]() and the clock frequency is

and the clock frequency is ![]() MHz. Note that the noise sequence data is

MHz. Note that the noise sequence data is ![]() in the HSPICE transient simulation through the use of the .DATA statement [16]. This command allows inclusion of data that has been externally generated. In this example, a two-column (time, voltage) format file, named noisedata, is loaded, and the transient analysis uses the time data provided in column 1 of file noisedata as the sweep input parameter.

in the HSPICE transient simulation through the use of the .DATA statement [16]. This command allows inclusion of data that has been externally generated. In this example, a two-column (time, voltage) format file, named noisedata, is loaded, and the transient analysis uses the time data provided in column 1 of file noisedata as the sweep input parameter.

Figure 4.19 Injecting noise data sequences in transient HSPICE simulations: (a) sampling circuit example and (b) SPICE netlist.

In order to compute the noise data used in the electrical simulations, it should be taken into account that ![]() is a random signal, and hence, its instantaneous value is not known. Instead, it can be described as a random process of zero mean and an amplitude uniformly distributed in the range

is a random signal, and hence, its instantaneous value is not known. Instead, it can be described as a random process of zero mean and an amplitude uniformly distributed in the range ![]() , where

, where ![]() denotes the rms value of

denotes the rms value of ![]() . In this case, the mean-square value of

. In this case, the mean-square value of ![]() is given by [17]

is given by [17]

4.7

Assuming a band-limited noise source, the PSD of ![]() can be computed as

can be computed as

4.8 ![]()

where ![]() stands for the equivalent noise bandwidth of

stands for the equivalent noise bandwidth of ![]() . Hence, if

. Hence, if ![]() is sampled at

is sampled at ![]() , the value of

, the value of ![]() at instant

at instant ![]() can be computed as

can be computed as

where ![]() represents a random number in the range

represents a random number in the range ![]() and

and ![]() [18].

[18].

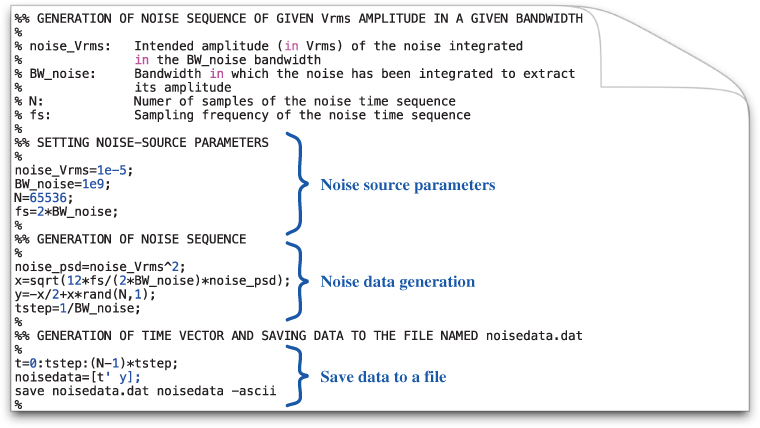

Figure 4.20 shows the MATLAB code used for generating an ![]() -point data sequence derived from Equation 4.9. Note that the data sequence is saved as a two-column format file, in which the first column represents the time series (i.e.,

-point data sequence derived from Equation 4.9. Note that the data sequence is saved as a two-column format file, in which the first column represents the time series (i.e., ![]() ) and the second column is the noise data sequence generated using Equation 4.9.

) and the second column is the noise data sequence generated using Equation 4.9.

Figure 4.20 MATLAB code used for generating an ![]() -point data sequence derived from Equation 4.9.

-point data sequence derived from Equation 4.9.

As an illustration, Figure 4.21 shows the PSD of the noise sampled and stored in the capacitor of Figure 4.19a, considering different values of ![]() . In this example, a noise source with

. In this example, a noise source with ![]() Vrms,

Vrms, ![]() GHz, and

GHz, and ![]() was considered in order to emulate an unlimited-band noise source. This way, the time interval between two consecutive samples is low enough (1 ns in this example), thus enabling to model the noise source as a CT source [19], which is filtered by the circuit made up of

was considered in order to emulate an unlimited-band noise source. This way, the time interval between two consecutive samples is low enough (1 ns in this example), thus enabling to model the noise source as a CT source [19], which is filtered by the circuit made up of ![]() and

and ![]() , with

, with ![]() being the switch on-resistance. This results in an equivalent bandwidth of the sampled noise given by

being the switch on-resistance. This results in an equivalent bandwidth of the sampled noise given by ![]() . As shown in Figure 4.21, aliasing occurs in this case because

. As shown in Figure 4.21, aliasing occurs in this case because ![]() . As a consequence the noise power increases within the Nyquist band, that is, from DC to

. As a consequence the noise power increases within the Nyquist band, that is, from DC to ![]() .

.

Figure 4.21 Illustrating the effect of sampling noise in HSPICE transient simulations. Output spectrum of the voltage stored in ![]() in Figure 4.19a, considering the following simulation data:

in Figure 4.19a, considering the following simulation data: ![]() ,

, ![]() pF,

pF, ![]() 1 MHz.

1 MHz.

4.2.2 Analyzing the Impact of Main Noise Sources in SC Integrators

The simulation technique formerly described can be used for verifying the impact of most critical noise sources on the performance of main ![]() building blocks through transient SPICE simulations. This is particularly critical in SC circuits because of the action of their sampled-data circuit nature, with the subsequent effect of the sampling process on noise sources.

building blocks through transient SPICE simulations. This is particularly critical in SC circuits because of the action of their sampled-data circuit nature, with the subsequent effect of the sampling process on noise sources.

As an illustration, let us consider an SC FE integrator similar to that shown in Figure 3.5a. As stated in Chapter 2, their main sources of circuit noise are generated in the switches and in the amplifier. Figure 4.22 shows the circuit schematics that can be used for evaluating the influence of these noise sources on SC integrators and Figure 4.23 shows the corresponding HSPICE netlist. Note that all circuits are built through simple macromodels for the switches and the amplifier in order to isolate the effect of the different error sources to be considered. Figure 4.22a shows the schematic used for simulating the thermal noise introduced by switches controlled by clock phase ![]() , and Figure 4.22b shows the corresponding test-bench schematic for the evaluation of thermal noise generated in the switches controlled by

, and Figure 4.22b shows the corresponding test-bench schematic for the evaluation of thermal noise generated in the switches controlled by ![]() . The test-bench schematic used for the noise sources generated in the amplifier is shown in Figure 4.22c. In the latter case, both thermal and flicker noise components need to be generated. This can be done as detailed in the next section.

. The test-bench schematic used for the noise sources generated in the amplifier is shown in Figure 4.22c. In the latter case, both thermal and flicker noise components need to be generated. This can be done as detailed in the next section.

Figure 4.22 Equivalent single-ended circuits used for simulating the effect of main noise sources in SC integrators: (a) noise contribution of switches controlled by ![]() and (b) noise contribution of switches controlled by

and (b) noise contribution of switches controlled by ![]() , and (c) noise contribution of the amplifier.

, and (c) noise contribution of the amplifier.

Figure 4.23 HSPICE netlist of the circuits shown in Figure 4.22.

4.2.3 Generating and Injecting Flicker Noise Sources in Electrical Simulations

The procedure described in Section 4.2.1 assumed white noise sources. However, some noise sources of noise in ![]() Ms also include flicker (

Ms also include flicker (![]() ) noise components that might be critical in low-bandwidth applications such as sensors, instrumentation, and biomedical applications.

) noise components that might be critical in low-bandwidth applications such as sensors, instrumentation, and biomedical applications.

Flicker noise can be generated as a colored noise sequence in MATLAB by filtering a white noise source through a filter with the following transfer function [20]

4.10 ![]()

where ![]() is a real number between 0 and 2. This way, the corresponding noise sequence data can be injected in HSPICE transient simulations using the same method as that described in previous sections.

is a real number between 0 and 2. This way, the corresponding noise sequence data can be injected in HSPICE transient simulations using the same method as that described in previous sections.

Alternatively, colored noise data sequence, including both ![]() and white noise components, can be generated by extracting the PSD data of the corresponding noise source using a .NOISE analysis in SPICE and then, generating a noise time sequence in MATLAB which is equivalent to the captured PSD, and that can be injected in transient simulations using the .DATA statement.

and white noise components, can be generated by extracting the PSD data of the corresponding noise source using a .NOISE analysis in SPICE and then, generating a noise time sequence in MATLAB which is equivalent to the captured PSD, and that can be injected in transient simulations using the .DATA statement.

Figure 4.24 shows a MATLAB code used for generating a time data sequence according to the electrical data captured from a .NOISE simulation in HSPICE. In this example, simulation output data resulting from the noise analysis in HSPICE is stored in a file named psd_eq_preamp_1f_white_RRF.dat, which is assumed to be expressed in ![]() Hz, that is, corresponding to a PSD curve. Both PSD and rms values of the

Hz, that is, corresponding to a PSD curve. Both PSD and rms values of the ![]() and white noise components are identified and computed, and the corresponding time data series are generated using Equation 4.9.

and white noise components are identified and computed, and the corresponding time data series are generated using Equation 4.9.

Figure 4.24 MATLAB code used for generating colored noise data sequence extracted from HSPICE .NOISE simulation.

As an illustration, Figure 4.25 shows the output spectra generated by the MATLAB routine in Figure 4.24. Note that a huge number of points (![]() in this example) are required to generate FFTs at low frequencies and see the flicker noise corner frequency.

in this example) are required to generate FFTs at low frequencies and see the flicker noise corner frequency.

Figure 4.25 Output spectrum generated by the MATLAB routine shown in Figure 4.24.

4.2.4 Test Bench to Include Noise in the Simulation of  Ms

Ms

At the end of the design phase, transistor-level simulations of the whole ![]() M are mandatory in order to check that the electrical performance agrees with system-level behavioral simulations, and consequently with target specifications. In this situation, injecting noise sources in SPICE transient simulations is required. To this end, the total input-referred noise source, including the effect of sampling, can be generated and injected at the input node of the modulator following the methodology described in previous sections.

M are mandatory in order to check that the electrical performance agrees with system-level behavioral simulations, and consequently with target specifications. In this situation, injecting noise sources in SPICE transient simulations is required. To this end, the total input-referred noise source, including the effect of sampling, can be generated and injected at the input node of the modulator following the methodology described in previous sections.

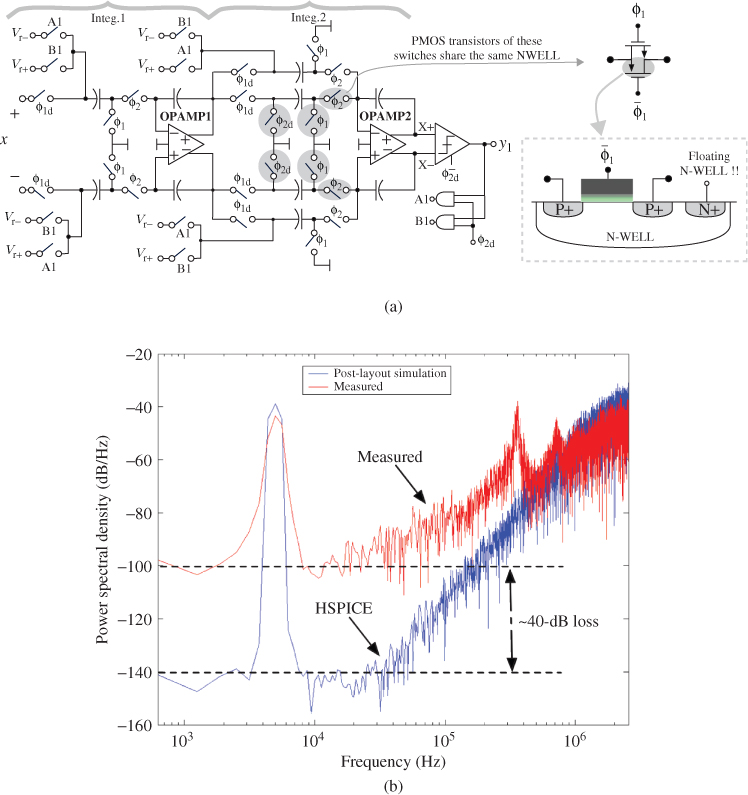

As an illustration, Figure 4.26a shows how to inject noise in transient simulations carried out using Cadence Virtuoso Schematic Editor [21] and Cadence-Spectre simulator [15]. The input-referred noise source is injected in the modulator (a fourth-order cascade 2-2 SC architecture in this example) by including a piece-wise linear (PWL) voltage source at the input node. The noise data sequence is loaded from a file as shown in Figure 4.26b. In this case, the noise data sequence is generated using the MATLAB code shown in Figure 4.27, where the standard deviation of the noise source is computed as

where ![]() is the sampling frequency of the modulator,

is the sampling frequency of the modulator, ![]() is the signal bandwidth, and

is the signal bandwidth, and ![]() (power_IBN in Figure 4.27) is the IBN due to the noise source—derived from the behavioral simulation data provided by SIMSIDES. Note that in this example, a Gaussian noise is generated using the randn function provided by MATLAB. Several cases of IBN are considered, which correspond to a reconfigurable

(power_IBN in Figure 4.27) is the IBN due to the noise source—derived from the behavioral simulation data provided by SIMSIDES. Note that in this example, a Gaussian noise is generated using the randn function provided by MATLAB. Several cases of IBN are considered, which correspond to a reconfigurable ![]() M for multistandard applications. As an illustration, Figure 4.28 shows the output spectrum of a fourth-order cascade 2-2 SC-

M for multistandard applications. As an illustration, Figure 4.28 shows the output spectrum of a fourth-order cascade 2-2 SC-![]() M, in which the effect of injecting thermal noise is highlighted. In this example, macromodels have been considered in all

M, in which the effect of injecting thermal noise is highlighted. In this example, macromodels have been considered in all ![]() building blocks in order to speed up the simulation, although the method is obviously valid for transistor-level simulations as well.

building blocks in order to speed up the simulation, although the method is obviously valid for transistor-level simulations as well.

Figure 4.26 Test-bench example to inject noise in transient simulations of ![]() Ms using Cadence-Spectre simulator: (a) schematic in the Virtuoso editor environment and (b) object properties windows highlighting how to load the noise data sequence file.

Ms using Cadence-Spectre simulator: (a) schematic in the Virtuoso editor environment and (b) object properties windows highlighting how to load the noise data sequence file.

Figure 4.27 MATLAB code used for generating an ![]() -point data sequence derived from Equation 4.11.

-point data sequence derived from Equation 4.11.

Figure 4.28 Output spectrum of a fourth-order cascade 2-2 SC-![]() M. The simulation was carried out in Cadence-Spectre, considering macromodels for all building blocks and injecting the input-referred noise source as illustrated in Figure 4.26.

M. The simulation was carried out in Cadence-Spectre, considering macromodels for all building blocks and injecting the input-referred noise source as illustrated in Figure 4.26.

4.3 Processing  M Output Results of Electrical Simulations

M Output Results of Electrical Simulations

The ![]() M output bitstreams obtained by electrical simulations need to be properly processed in order to characterize main figures of merit, namely output spectrum, IBN, SNR/SNDR, THD, etc. To this purpose, the following step-by-step procedure can be followed:6

M output bitstreams obtained by electrical simulations need to be properly processed in order to characterize main figures of merit, namely output spectrum, IBN, SNR/SNDR, THD, etc. To this purpose, the following step-by-step procedure can be followed:6

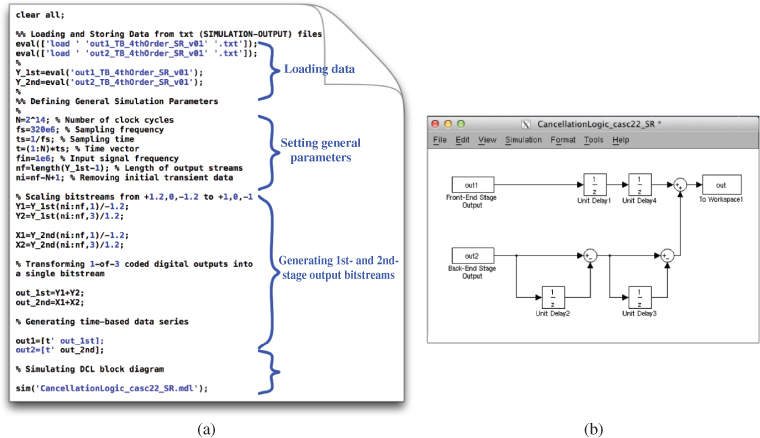

Figure 4.29 shows a conceptual diagram of the step-by-step procedure formerly described, considering that the electrical simulations are carried out with Cadence-Spectre, and the results are processed using SIMSIDES. As an example, let us consider a fourth-order cascade 2-2 SC-![]() M with trilevel quantization in both stages. Figure 4.30a shows the test-bench schematic used in Cadence to simulate the modulator. In this example, the output of the front-end and the back-end stages of the modulator are, respectively, named Output1<1:3> and Output2<1:3>, where Outputj<i> corresponds to the

M with trilevel quantization in both stages. Figure 4.30a shows the test-bench schematic used in Cadence to simulate the modulator. In this example, the output of the front-end and the back-end stages of the modulator are, respectively, named Output1<1:3> and Output2<1:3>, where Outputj<i> corresponds to the ![]() th output bit of the

th output bit of the ![]() th stage quantizer, considering a 1-of-3 digital code as illustrated in Figure 4.7. Overall, six bitstreams are collected and stored in a text file. This task is implemented by the blocks named WRITE OUTPUT, which implement the Verilog-A code shown in Figure 4.30b. Note that the output data—consisting of the three bitstreams named Out1, Out2, Out3—are collected and stored in the text file at a rate of one sample per clock cycle as illustrated in Figure 4.30c. The event at which the data are collected is governed by a trigger signal, named trigger in this example. This trigger signal corresponds to the clock phase in which the comparator outputs are settled, which in this example is clock phase

th stage quantizer, considering a 1-of-3 digital code as illustrated in Figure 4.7. Overall, six bitstreams are collected and stored in a text file. This task is implemented by the blocks named WRITE OUTPUT, which implement the Verilog-A code shown in Figure 4.30b. Note that the output data—consisting of the three bitstreams named Out1, Out2, Out3—are collected and stored in the text file at a rate of one sample per clock cycle as illustrated in Figure 4.30c. The event at which the data are collected is governed by a trigger signal, named trigger in this example. This trigger signal corresponds to the clock phase in which the comparator outputs are settled, which in this example is clock phase ![]() .

.

Figure 4.29 Step-by-step procedure to process electrical simulation outputs.

Figure 4.30 Collecting and storing the output bitstreams of a ![]() M in an electrical simulation: (a) test-bench schematic in Cadence Design FrameWork, (b) Verilog-A code to capture simulation output results, and (c) excerpt of the generated output file (text format).

M in an electrical simulation: (a) test-bench schematic in Cadence Design FrameWork, (b) Verilog-A code to capture simulation output results, and (c) excerpt of the generated output file (text format).

Once the simulation output data has been stored in a multicolumn text file, this data can be loaded and processed using the MATLAB routine shown in Figure 4.31a. Note that the bitstreams of both stages are scaled from the values of the supply voltage (1.2V) to 1V and the 1-of-3 codification is transformed into a single-bit output format. Both output bitstreams are processed by a DCL implemented in SIMULINK as shown in Figure 4.31b. Once this DCL diagram is simulated, the overall modulator output is saved into the MATLAB workspace and can be processed using SIMSIDES post-processing facilities. As an illustration, the output spectrum shown in Figure 4.28 was obtained using the procedure and routines described in this section.

Figure 4.31 MATLAB routine used for processing ![]() M outputs from electrical simulations: (a) MATLAB code and (b) DCL block diagram implemented in SIMULINK.

M outputs from electrical simulations: (a) MATLAB code and (b) DCL block diagram implemented in SIMULINK.

4.4 Design Considerations and Simulation Test Benches of  M Basic Building Blocks

M Basic Building Blocks

Once the modulator has been verified using macromodels and the performance has been evaluated considering main nonideal circuit and physical effects (including circuit noise), the next step is the electrical transistor-level design of ![]() M building blocks and circuit elements. In this book, we will distinguish between two different categories of

M building blocks and circuit elements. In this book, we will distinguish between two different categories of ![]() M building blocks or subcircuits. The first category, referred to as basic building blocks, includes the loop filter (essentially based on integrators and resonators) and the embedded quantizer, made up of an ADC (usually a flash ADC made of a bank of comparators) and a DAC. The second category includes a number of so-called auxiliary building blocks which are also needed to implement a

M building blocks or subcircuits. The first category, referred to as basic building blocks, includes the loop filter (essentially based on integrators and resonators) and the embedded quantizer, made up of an ADC (usually a flash ADC made of a bank of comparators) and a DAC. The second category includes a number of so-called auxiliary building blocks which are also needed to implement a ![]() M IC. Among others, the most important auxiliary blocks are the clock-phase generator, the master bias generator, the reference voltage generator, and the digital circuits required for buffering and signal processing.

M IC. Among others, the most important auxiliary blocks are the clock-phase generator, the master bias generator, the reference voltage generator, and the digital circuits required for buffering and signal processing.

This section deals with the design of basic ![]() M building blocks, focusing on their essential circuit elements, namely switches, comparators, OTAs, and DACs. The main design considerations concerning these circuits are described together with practical simulation test benches frequently used for characterizing their main electrical performance metrics, which have been derived from system-level behavioral simulations.

M building blocks, focusing on their essential circuit elements, namely switches, comparators, OTAs, and DACs. The main design considerations concerning these circuits are described together with practical simulation test benches frequently used for characterizing their main electrical performance metrics, which have been derived from system-level behavioral simulations.

4.4.1 Design Considerations of CMOS Switches

Practically, all switches used in SC-![]() Ms are of CMOS type, that is, based on a pMOS and an nMOS transistor connected in parallel, as illustrated in Figure 4.32.7 As stated in Chapters 2 and 3, the most important design specification of CMOS switches is the switch on-resistance

Ms are of CMOS type, that is, based on a pMOS and an nMOS transistor connected in parallel, as illustrated in Figure 4.32.7 As stated in Chapters 2 and 3, the most important design specification of CMOS switches is the switch on-resistance ![]() . The value of

. The value of ![]() is mainly constricted by dynamic considerations that affect the integrator transient response and consequently the effective resolution of the modulator [22].

is mainly constricted by dynamic considerations that affect the integrator transient response and consequently the effective resolution of the modulator [22].

Figure 4.32 Switch symbol and its equivalent CMOS circuit.

Let us consider that the CMOS switch of Figure 4.32 is switched on, that is, ![]() and

and ![]() . Assuming that the nMOS and pMOS transistors operate in the ohmic region, their on-resistances can be approximated by Equation 2.47, and the overall CMOS switch on-resistance is the result of the parallel connection of resistors

. Assuming that the nMOS and pMOS transistors operate in the ohmic region, their on-resistances can be approximated by Equation 2.47, and the overall CMOS switch on-resistance is the result of the parallel connection of resistors ![]() and

and ![]() .

.

Trade-Off Between  and the CMOS Switch Drain/Source Parasitic Capacitances

and the CMOS Switch Drain/Source Parasitic Capacitances

As discussed in Section 2.7.2, the value of ![]() can be reduced by increasing the aspect ratio (

can be reduced by increasing the aspect ratio (![]() ) of both transistors in the CMOS switch. However, this increases the transistors area, and consequently their associated drain/source parasitic capacitances, with the subsequent penalty in the transient response and integrators dynamics degradation. Therefore, there is a trade-off between the maximum value of

) of both transistors in the CMOS switch. However, this increases the transistors area, and consequently their associated drain/source parasitic capacitances, with the subsequent penalty in the transient response and integrators dynamics degradation. Therefore, there is a trade-off between the maximum value of ![]() that can be tolerated—which can be determined by behavioral simulation as shown in Chapter 3—and the drain/source parasitic capacitances associated with the CMOS switch that are in turn conditioned by the value of capacitors used in the SC branches. This way, switch transistor sizes can be scaled down across the modulator chain, using higher sizes in the front-end switches—where larger capacitors are chosen according to thermal noise considerations—while lower sizes are tolerated in back-end integrators, where smaller capacitors are normally used and hence the influence of switch parasitic capacitances is diminished.

that can be tolerated—which can be determined by behavioral simulation as shown in Chapter 3—and the drain/source parasitic capacitances associated with the CMOS switch that are in turn conditioned by the value of capacitors used in the SC branches. This way, switch transistor sizes can be scaled down across the modulator chain, using higher sizes in the front-end switches—where larger capacitors are chosen according to thermal noise considerations—while lower sizes are tolerated in back-end integrators, where smaller capacitors are normally used and hence the influence of switch parasitic capacitances is diminished.

Characterizing the Nonlinear Behavior of

According to Equation 2.47, the values of ![]() and

and ![]() depend on the switch common-mode voltage,

depend on the switch common-mode voltage, ![]() , and hence on the drain and source voltages (denoted as

, and hence on the drain and source voltages (denoted as ![]() and

and ![]() in Figure 4.32) of the nMOS and pMOS transistors. As a consequence, the value of

in Figure 4.32) of the nMOS and pMOS transistors. As a consequence, the value of ![]() becomes a nonlinear function of the voltage being transmitted, thus generating harmonic distortion as discussed in Chapters 2 and 3.

becomes a nonlinear function of the voltage being transmitted, thus generating harmonic distortion as discussed in Chapters 2 and 3.

In order to evaluate the nonlinear characteristic of ![]() in CMOS switches, the circuit shown in Figure 4.33a can be used. The gate of nMOS transistor is connected to

in CMOS switches, the circuit shown in Figure 4.33a can be used. The gate of nMOS transistor is connected to ![]() and the gate of pMOS transistor is connected to

and the gate of pMOS transistor is connected to ![]() so that both transistors are switched on. A small voltage imbalance, typically in the order of 10–20 mV, is applied across the CMOS switch to guarantee that both nMOS and pMOS are properly biased and operate in the linear region. A DC common-mode voltage source is connected to the input node of the switch. This voltage is swept in a DC analysis in order to evaluate its impact on the variation of

so that both transistors are switched on. A small voltage imbalance, typically in the order of 10–20 mV, is applied across the CMOS switch to guarantee that both nMOS and pMOS are properly biased and operate in the linear region. A DC common-mode voltage source is connected to the input node of the switch. This voltage is swept in a DC analysis in order to evaluate its impact on the variation of ![]() .

.

Figure 4.33 Characterizing nonlinear switch on-resistance: (a) test-bench circuit, (b) HSPICE netlist, and (c) ![]() versus

versus ![]() considering a 90-nm CMOS technology with 1.2-V supply voltage.

considering a 90-nm CMOS technology with 1.2-V supply voltage.

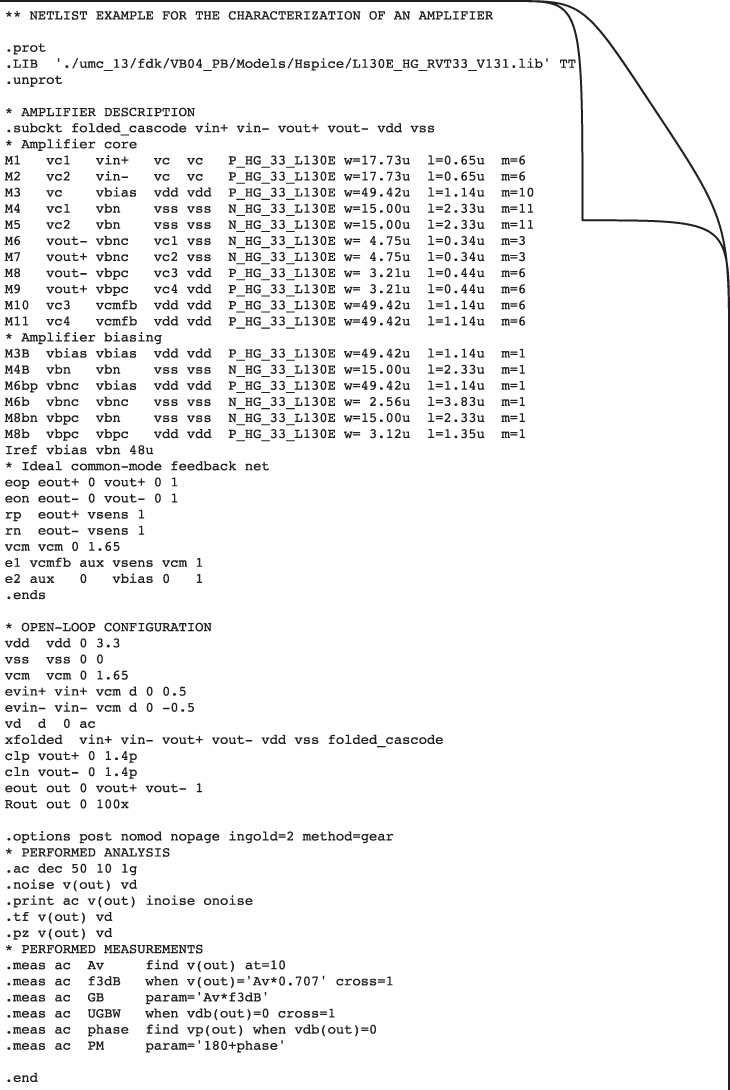

Figure 4.33b shows the SPICE netlist used for simulating the circuit in Figure 4.33a. In this example, a 10-mV voltage, named vd, is applied across the switch and the common-mode voltage (vin in Figure 4.33a) is swept using a .DC analysis in SPICE. The value of ![]() can be extracted from each operating point in the .DC analysis by means of a parameter defined as PAR(1/(lx8(mp)+lx8(mn)) where lx8(mp,n) is an alias parameter used in HSPICE to represent the DC drain-source conductance of MOS transistors (

can be extracted from each operating point in the .DC analysis by means of a parameter defined as PAR(1/(lx8(mp)+lx8(mn)) where lx8(mp,n) is an alias parameter used in HSPICE to represent the DC drain-source conductance of MOS transistors (![]() and

and ![]() in Figure 4.33a). Thus, the values of

in Figure 4.33a). Thus, the values of ![]() and

and ![]() are extracted from 1/lx8(mn) and 1/lx8(mp), respectively [16].

are extracted from 1/lx8(mn) and 1/lx8(mp), respectively [16].

Figure 4.33c represents ![]() as a function of

as a function of ![]() , giving rise to a function similar to that shown in Figure 2.20b. The curves corresponding to both

, giving rise to a function similar to that shown in Figure 2.20b. The curves corresponding to both ![]() and

and ![]() are also depicted to illustrate the separate contribution of each transistor to the overall switch on-resistance. The maximum value of

are also depicted to illustrate the separate contribution of each transistor to the overall switch on-resistance. The maximum value of ![]() , denoted as ronmax, and the quiescent value of

, denoted as ronmax, and the quiescent value of ![]() , denoted as ronQ, can also be extracted from HSPICE simulations using the .meas command [16] as detailed in the netlist shown in Figure 4.33b.

, denoted as ronQ, can also be extracted from HSPICE simulations using the .meas command [16] as detailed in the netlist shown in Figure 4.33b.

The ![]() -versus-

-versus-![]() characteristic shown in Figure 4.33c has been obtained for

characteristic shown in Figure 4.33c has been obtained for ![]() , which according to Equation 2.47, gives an almost symmetrical function. An alternative approach consists of increasing

, which according to Equation 2.47, gives an almost symmetrical function. An alternative approach consists of increasing ![]() to equal

to equal ![]() , as illustrated in Figure 2.22. For the sake of completeness a similar figure is depicted in Figure 4.34, considering a 90-nm CMOS technology with a 1.2-V supply voltage. It can be noted how as

, as illustrated in Figure 2.22. For the sake of completeness a similar figure is depicted in Figure 4.34, considering a 90-nm CMOS technology with a 1.2-V supply voltage. It can be noted how as ![]() increases, the nonlinearity of the switch on-resistance increases, although its average value decreases. Hence, as discussed in Section 2.7.2, if the sizing of the nMOS and pMOS transistors in a CMOS switch compensates the difference in their transconductance parameters, the switch on-resistance nonlinearity is reduced, but the average on-resistance is larger than using the same sizes, that is,

increases, the nonlinearity of the switch on-resistance increases, although its average value decreases. Hence, as discussed in Section 2.7.2, if the sizing of the nMOS and pMOS transistors in a CMOS switch compensates the difference in their transconductance parameters, the switch on-resistance nonlinearity is reduced, but the average on-resistance is larger than using the same sizes, that is, ![]() . In the latter case, the area, and consequently the values of parasitic drain/source capacitances, increases as well although the overall effect of the finite switch on-resistance on the settling performance decreases [23]. Therefore, there is a design trade-off involving the switch on-resistance nonlinearity and its average value, which at the modulator level translates in the well-known analog design trade-off between speed (limited by the incomplete settling) and linearity (limited by nonlinear switch on-resistance) [22]. Nevertheless, in the majority of state-of-the-art SC-

. In the latter case, the area, and consequently the values of parasitic drain/source capacitances, increases as well although the overall effect of the finite switch on-resistance on the settling performance decreases [23]. Therefore, there is a design trade-off involving the switch on-resistance nonlinearity and its average value, which at the modulator level translates in the well-known analog design trade-off between speed (limited by the incomplete settling) and linearity (limited by nonlinear switch on-resistance) [22]. Nevertheless, in the majority of state-of-the-art SC-![]() Ms, CMOS switches are designed to keep a low enough average value of

Ms, CMOS switches are designed to keep a low enough average value of ![]() , while keeping a symmetrical

, while keeping a symmetrical ![]() -versus-

-versus-![]() characteristic similar to that shown in Figure 4.33c.

characteristic similar to that shown in Figure 4.33c.

Figure 4.34 ![]() versus

versus ![]() for different values of

for different values of ![]() , considering a 90-nm CMOS technology with 1.2-V supply voltage (

, considering a 90-nm CMOS technology with 1.2-V supply voltage (![]() nm).

nm).

Influence of Technology Downscaling

According to Equation 2.47, the reduction of the supply voltage caused by CMOS technology downscaling causes an increase of ![]() . However, this effect can be compensated by the lower channel lengths (

. However, this effect can be compensated by the lower channel lengths (![]() ) used in smaller technologies. This is illustrated in Figure 4.35, where

) used in smaller technologies. This is illustrated in Figure 4.35, where ![]() is represented versus

is represented versus ![]() for

for ![]() , considering different CMOS processes from 250 to 90 nm. Note that, generally speaking, the design of switches benefits from technology downscaling as lower values of

, considering different CMOS processes from 250 to 90 nm. Note that, generally speaking, the design of switches benefits from technology downscaling as lower values of ![]() can be obtained for the same (or even smaller) switch sizing, with the subsequent advantages in terms of silicon area and robustness against parasitic capacitances. It can be noticed how migrating from 180 to 130 nm has no effect on

can be obtained for the same (or even smaller) switch sizing, with the subsequent advantages in terms of silicon area and robustness against parasitic capacitances. It can be noticed how migrating from 180 to 130 nm has no effect on ![]() because the reduction in MOS transistor sizes is compensated by the voltage supply downscaling. However, comparing 130 nm with 90 nm, both using 1.2-V supply voltage, the downscaling process becomes beneficial.

because the reduction in MOS transistor sizes is compensated by the voltage supply downscaling. However, comparing 130 nm with 90 nm, both using 1.2-V supply voltage, the downscaling process becomes beneficial.

Figure 4.35 Illustrating the effect of technology downscaling on ![]() .

.

Evaluating Harmonic Distortion

Figure 4.36a shows the equivalent circuit that can be used for the evaluation of the harmonic distortion caused by the nonlinear sampling process because of the finite switch on-resistance. This test-bench circuit—which contains essentially the equivalent circuit shown in Figure 2.22—corresponds to the fully-differential implementation of the input SC branch in a typical front-end integrator used in SC-![]() Ms—conceptually illustrated in Figure 4.36a. As discussed in Section 2.7.2, as switch

Ms—conceptually illustrated in Figure 4.36a. As discussed in Section 2.7.2, as switch ![]() is directly connected to the input node, its nonlinear on-resistance may vary a lot during the sampling period, thus generating considerable harmonic distortion. In contrast, switch

is directly connected to the input node, its nonlinear on-resistance may vary a lot during the sampling period, thus generating considerable harmonic distortion. In contrast, switch ![]() has one of its terminals connected to a fixed voltage—the analog common-mode voltage—so that the voltage across this switch remains approximately constant over clock periods. As illustrated in Figure 4.36a, the voltage variations at the input node of

has one of its terminals connected to a fixed voltage—the analog common-mode voltage—so that the voltage across this switch remains approximately constant over clock periods. As illustrated in Figure 4.36a, the voltage variations at the input node of ![]() are considerably lower than that in

are considerably lower than that in ![]() . As a consequence, the effect of

. As a consequence, the effect of ![]() can be neglected in practice. Indeed, the test-bench circuit shown in Figure 4.36b will give essentially the same results as the circuit in Figure 4.36a in the majority of practical situations.

can be neglected in practice. Indeed, the test-bench circuit shown in Figure 4.36b will give essentially the same results as the circuit in Figure 4.36a in the majority of practical situations.

Figure 4.36 Characterizing harmonic distortion caused by nonlinear sampling: (a) test-bench equivalent circuit, (b) practical (simplified) version of the test-bench circuit, and (c) HSPICE netlist. (A test-bench circuit with ![]() and

and ![]() can be used as well.)

can be used as well.)

The corresponding SPICE netlist is shown in Figure 4.36c. A transient analysis is carried out considering different situations for the input signal, that is, a single tone signal, a two-tone signal, etc. To this end, a single-ended source is converted to a differential input signal using voltage-controlled voltage sources, while some subcircuits are used for representing the switches and sampling branches included in the test bench. A .TRAN analysis is carried out with a printing time step defined as the sampling period—10 ns in this example. The stop time is given by N/fs, where N is the number of simulation clock cycles (4096 in this example) and fs is the sampling frequency (100 MHz in this example).

As stated above, harmonic distortion is mainly caused by the switches that are directly connected to the input (![]() ) given that the voltages at the input/output nodes of the remaining ones remain approximately constant over clock periods, and consequently

) given that the voltages at the input/output nodes of the remaining ones remain approximately constant over clock periods, and consequently ![]() is approximately constant during the sampling phase time. The same reasoning applies to those switches that are in any of the following situations:

is approximately constant during the sampling phase time. The same reasoning applies to those switches that are in any of the following situations:

- Switches that are connected to nodes where the voltage keeps constant over the sampling period.

- Switches that are connected to the output of an SC circuit. For instance all switches of the back-end SC integrators, that is, all integrators except the front-end one. In all these switches, the voltages in their terminals remain constant over clock periods.

- Sampling switches that are connected to the input node of SC-

Ms whenever the ratio between the input signal frequency and the sampling frequency is small, typically less than one-tenth.

Ms whenever the ratio between the input signal frequency and the sampling frequency is small, typically less than one-tenth.

The latter situation is illustrated in Figure 4.37, where a sinewave input signal with different values of the input frequency ![]() is represented within the sampling time period, from 0 to

is represented within the sampling time period, from 0 to ![]() , with

, with ![]() and

and ![]() MHz in this example. Note that as the ratio between

MHz in this example. Note that as the ratio between ![]() and

and ![]() increases, there are larger variations of

increases, there are larger variations of ![]() over the sampling period, which translates into a higher variation of

over the sampling period, which translates into a higher variation of ![]() , thus increasing the harmonic distortion.

, thus increasing the harmonic distortion.

Figure 4.37 Impact of increasing the input signal frequency on the variation of ![]() over the sampling period. A fully-differential sinewave input signal of frequency

over the sampling period. A fully-differential sinewave input signal of frequency ![]() is considered with

is considered with ![]() MHz. This figure plots both positive and negative single-ended inputs.

MHz. This figure plots both positive and negative single-ended inputs.

The analysis of the harmonic distortion caused by the nonlinear sampling process using the Volterra series method [24, 25] demonstrates that the third-order harmonic distortion caused by this dynamic nonlinearity is approximately given by [26]

where ![]() is the input signal amplitude,

is the input signal amplitude, ![]() denotes the switch-on voltage (either

denotes the switch-on voltage (either ![]() or

or ![]() ), and

), and ![]() is the maximum (worst-case) value of

is the maximum (worst-case) value of ![]() and

and ![]() .

.

The expression given in Equation 4.12 is consistent with the results highlighted in Figure 4.37, showing a direct dependency of ![]() on

on ![]() . This is illustrated in Figure 4.38, where several output spectra of the circuit in Figure 4.36b are depicted for different values of

. This is illustrated in Figure 4.38, where several output spectra of the circuit in Figure 4.36b are depicted for different values of ![]() , with

, with ![]() . These output spectra have been processed with SIMSIDES based on the use of a Kaiser FFT window.

. These output spectra have been processed with SIMSIDES based on the use of a Kaiser FFT window.

Figure 4.38 Illustrating the impact of increasing the input signal frequency on the harmonic distortion caused by nonlinear sampling process. Three cases of ![]() are considered:

are considered: ![]() ,

, ![]() , and

, and ![]() , where

, where ![]() MHz.

MHz.

In practical situations, ![]() is chosen to be

is chosen to be ![]() , with

, with ![]() being the signal bandwidth. This way, the third-order harmonic components fall into the signal bandwidth. This is not the case of BP-

being the signal bandwidth. This way, the third-order harmonic components fall into the signal bandwidth. This is not the case of BP-![]() Ms where the notch frequency (i.e., the center signal frequency) is typically placed at

Ms where the notch frequency (i.e., the center signal frequency) is typically placed at ![]() as stated in Chapter 1. In this case, other distortion metrics, such us the third-order intermodulation distortion

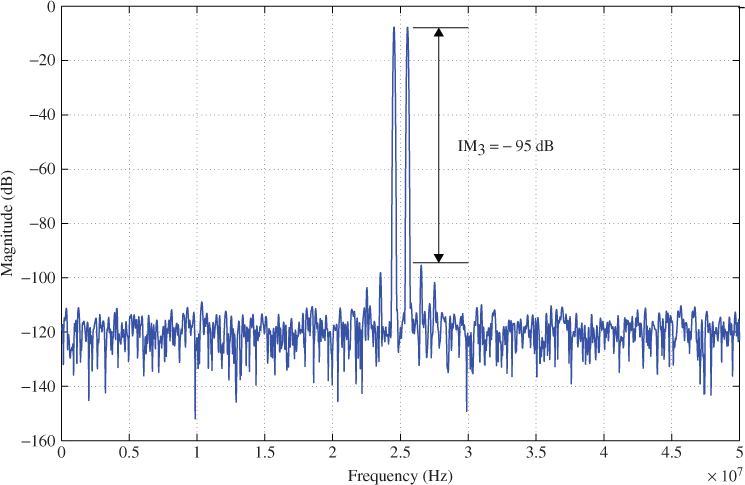

as stated in Chapter 1. In this case, other distortion metrics, such us the third-order intermodulation distortion ![]() is used. Thus, in this case a two-tone input signal is used in the test-bench circuit of Figure 4.36b. As an illustration, Figure 4.39 shows the output spectrum of Figure 4.36b considering two tones with amplitude

is used. Thus, in this case a two-tone input signal is used in the test-bench circuit of Figure 4.36b. As an illustration, Figure 4.39 shows the output spectrum of Figure 4.36b considering two tones with amplitude ![]() located at8

located at8

4.13 ![]()

![]() MHz and

MHz and ![]() MHz with

MHz with ![]() MHz.

MHz.

Figure 4.39 Intermodulation distortion caused by the nonlinear sampling operation. Data used in the simulation: 90-nm CMOS technology, ![]() V,

V, ![]() m,

m, ![]() m,

m, ![]() nm,

nm, ![]() .

.

4.4.2 Design Considerations of Operational Amplifiers

Voltage amplifiers are basic circuits of SC-![]() Ms used for building SC integrators and resonators. They are also used for implementing active-RC integrators in CT-

Ms used for building SC integrators and resonators. They are also used for implementing active-RC integrators in CT-![]() Ms. As already discussed in Chapters 2 and 3, the main electrical requirements of amplifiers can be determined from closed-form expressions and behavioral simulations, and usually comprise specifications for the DC gain, output swing, dynamic behavior, and input-referred noise.

Ms. As already discussed in Chapters 2 and 3, the main electrical requirements of amplifiers can be determined from closed-form expressions and behavioral simulations, and usually comprise specifications for the DC gain, output swing, dynamic behavior, and input-referred noise.

Typical Amplifier Topologies

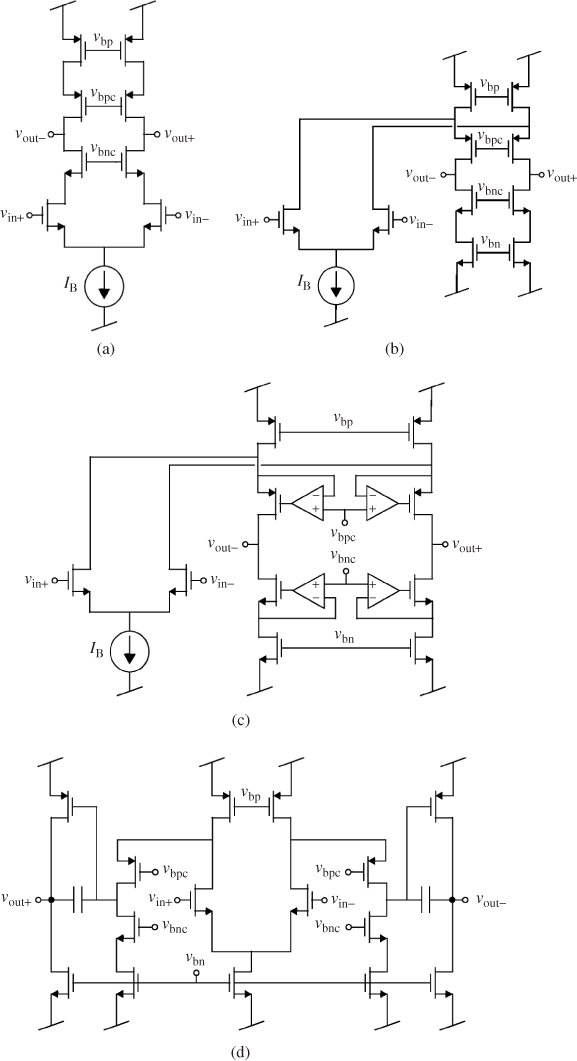

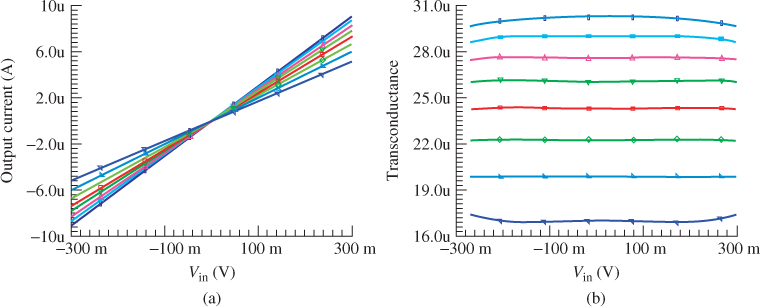

Many different topologies can be considered in order to fulfill the derived amplifier specifications at the transistor level. Figure 4.40 depicts some of the most representative amplifier topologies that are widely used in ![]() M design, namely:

M design, namely:

- Telescopic Amplifier (Figure 4.40a). This single-stage topology is capable of providing a moderate DC gain and an excellent dynamic behavior while being very power efficient, as it employs a single current branch. However, the topology requires five stacked transistors, what results in a reduced output swing and complicates its design (or even prevents its use) in low-voltage

implementations. Nevertheless, the telescopic amplifier should be considered the best option if high DC gain and high output swing are not required.

implementations. Nevertheless, the telescopic amplifier should be considered the best option if high DC gain and high output swing are not required. - Folded Cascode Amplifier (Figure 4.40b). This single-stage topology exhibits an output swing larger than that of the telescopic amplifier—only four transistors are stacked—but doubles the power consumption because of the two current branches required. It provides a very good settling behavior, although its first nondominant pole—and thus its phase margin—is somewhat lower compared to the telescopic amplifier. Folded cascode amplifiers are often used if moderate DC gain is required in

Ms with medium- and low-voltage supply.

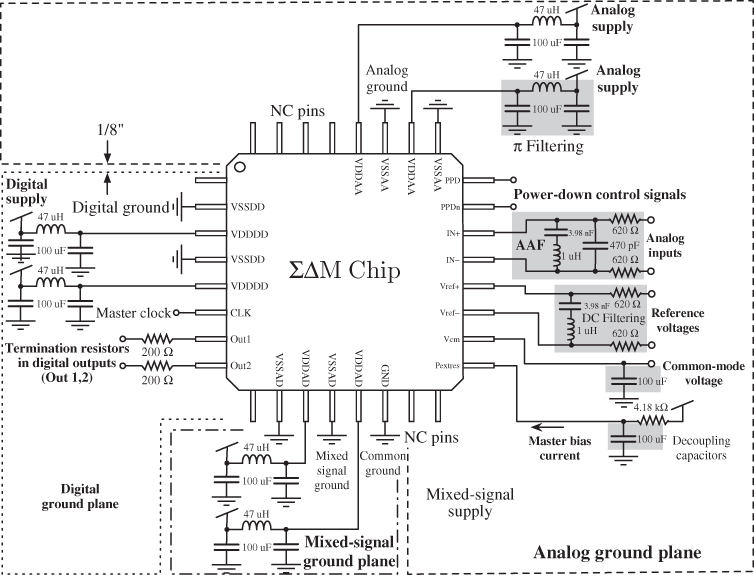

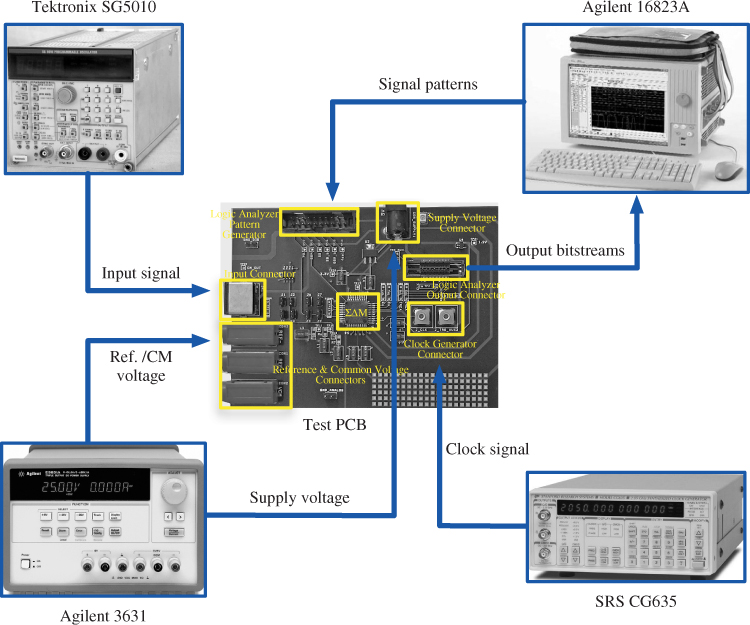

Ms with medium- and low-voltage supply. - Folded Cascode Amplifier with Gain Boosting (Figure 4.40c). This topology provides larger DC gain than the conventional folded cascode amplifier in Figure 4.40b by means of increasing its output resistance through the regulation of the cascode transistors. The auxiliary amplifiers are usually designed as simple as possible for their additional power consumption not to penalize that of the overall amplifier. Gain-boosting techniques are often employed in single-stage amplifiers, although especial attention must be paid so that the inner feedback loop does not degrade the amplifier frequency response, or even make it unstable in closed-loop form.