Chapter 5

Frontiers of ΣΔ Modulators: Trends and Challenges

Since the introduction of the ![]() modulation technique, there has been a pleiad of ICs published; implemented using many diverse technology processes, architectural, and circuit techniques, which have targeted a huge number of applications that span from sensors and instrumentation to ultra-low power, biomedical applications, and broadband communications [1–3].

modulation technique, there has been a pleiad of ICs published; implemented using many diverse technology processes, architectural, and circuit techniques, which have targeted a huge number of applications that span from sensors and instrumentation to ultra-low power, biomedical applications, and broadband communications [1–3].

An in-depth understanding of the performance of state-of-the-art ![]() Ms, their trends, challenges, and circuits and systems solutions, constitutes a powerful and empirical tool for designers to select the optimum

Ms, their trends, challenges, and circuits and systems solutions, constitutes a powerful and empirical tool for designers to select the optimum ![]() M architecture, circuit implementation, technology process, etc, for a given set of specifications and/or a particular application. With this objective in mind and following the practical approach considered throughout this book, this chapter gives an overview of reported cutting-edge

M architecture, circuit implementation, technology process, etc, for a given set of specifications and/or a particular application. With this objective in mind and following the practical approach considered throughout this book, this chapter gives an overview of reported cutting-edge ![]() M ICs fabricated in CMOS technologies. The main purpose of this overview is to make an exhaustive analysis of the evolution trends, design challenges, and reported solutions in order to extract practical conclusions and guidelines which may be useful for designers in their own projects.

M ICs fabricated in CMOS technologies. The main purpose of this overview is to make an exhaustive analysis of the evolution trends, design challenges, and reported solutions in order to extract practical conclusions and guidelines which may be useful for designers in their own projects.

The study described here is inspired by previous surveys on state-of-the-art performance of ADCs [3–10]. In the majority of cases, these surveys cover different kinds of ADCs, not only ![]() Ms. Among others, the surveys published by Walden [4], Murmann [5], and more recently Jonsson [8, 9] and Manganaro [10], are particularly exhaustive and accurate. Compared to these works, the study described in this book focuses on

Ms. Among others, the surveys published by Walden [4], Murmann [5], and more recently Jonsson [8, 9] and Manganaro [10], are particularly exhaustive and accurate. Compared to these works, the study described in this book focuses on ![]() M ICs; emphasizing on the different architectures and circuits used in many different applications. Moreover, in addition to analyzing statistics and comparing data collected from publications and extracted from standard performance metrics, the study presented in this chapter gives an overview of cutting-edge

M ICs; emphasizing on the different architectures and circuits used in many different applications. Moreover, in addition to analyzing statistics and comparing data collected from publications and extracted from standard performance metrics, the study presented in this chapter gives an overview of cutting-edge ![]() M circuits and systems techniques which are at the frontier of state-of-the-art performance, highlighting the incoming trends and challenges as well as the proposed efficient solutions.

M circuits and systems techniques which are at the frontier of state-of-the-art performance, highlighting the incoming trends and challenges as well as the proposed efficient solutions.

The data used for this study was mainly collected from the IEEE Journal of Solid-State Circuits as well as the major conferences sponsored by the IEEE Solid-State Circuits Society (SSCS), namely International Solid-State Circuits Conference (ISSCC), European Solid-State Circuits Conference (ESSCIRC), Custom Integrated Circuits Conference (CICC), Symposium on VLSI Circuits (VLSI), Asian Solid-State Circuits Conference (ASSCC), and Radio Frequency Integrated Circuits Symposium (RFIC). In addition to these SSCS publications, some other remarkable ![]() M ICs published in the IEEE Transactions on Circuits and Systems (parts I and II) and the IEEE International Symposium on Circuits and Systems (ISCAS) have also been collected in the survey.Overall, more than 300

M ICs published in the IEEE Transactions on Circuits and Systems (parts I and II) and the IEEE International Symposium on Circuits and Systems (ISCAS) have also been collected in the survey.Overall, more than 300 ![]() M ICs have been analyzed in detail and considered in this review. Although the works under study include papers published since 1990 to June 2012, data was more exhaustively collected in the last 10 years.

M ICs have been analyzed in detail and considered in this review. Although the works under study include papers published since 1990 to June 2012, data was more exhaustively collected in the last 10 years.

All data collected and analyzed in the survey is compiled in an Excel spreadsheet that is available online at http://www.imse-cnm.csic.es/∼jrosa/CMOS-SDMs-Survey-IMSE-JMdelaRosa.xlsx. The database in this spreadsheet file is periodically kept up to date every six months and aims to be a complement to the popular and highly cited Murmann's ADC survey data collection [11].

Following this introduction, the chapter is organized as follows. Section 5.1 gives an overview of the state-of-the-art ![]() Ms, comparing their performance with Nyquist-rate ADCs. The diverse families of

Ms, comparing their performance with Nyquist-rate ADCs. The diverse families of ![]() M architectures and circuit techniques are exhaustively analyzed and compared in Section 5.2 in order to extract practical and empirical design guidelines. Section 5.3 reviews some of the most significant cutting-edge

M architectures and circuit techniques are exhaustively analyzed and compared in Section 5.2 in order to extract practical and empirical design guidelines. Section 5.3 reviews some of the most significant cutting-edge ![]() M techniques, analyzing the design trends and challenges in the frontiers of

M techniques, analyzing the design trends and challenges in the frontiers of ![]() Ms. Finally, the chapter is concluded with a classified description of state-of-the-art references.

Ms. Finally, the chapter is concluded with a classified description of state-of-the-art references.

5.1 Overview of the State of the Art on  Ms

Ms

Tables 5.13 sum up the performance of the state-of-the-art ![]() M ICs considered in this survey. For the sake of clarity and simplicity, the ICs included in the study have been classified according to their architecture/circuit characteristics into the following tables:

M ICs considered in this survey. For the sake of clarity and simplicity, the ICs included in the study have been classified according to their architecture/circuit characteristics into the following tables:

- SC-

Ms: single-loop single-bit LP-

Ms: single-loop single-bit LP- Ms (Table 5.1), single-loop multibit LP-

Ms (Table 5.1), single-loop multibit LP- Ms (Table 5.2), cascade single-bit LP-

Ms (Table 5.2), cascade single-bit LP- Ms (Table 5.3), cascade multibit LP-

Ms (Table 5.3), cascade multibit LP- Ms (Table 5.4), and BP-

Ms (Table 5.4), and BP- Ms (Table 5.5).

Ms (Table 5.5). - CT-

Ms: single-loop single-bit LP-

Ms: single-loop single-bit LP- Ms (Table 5.6), single-loop multibit LP-

Ms (Table 5.6), single-loop multibit LP- Ms (Table 5.7), cascade LP-

Ms (Table 5.7), cascade LP- Ms (Table 5.8), and BP-

Ms (Table 5.8), and BP- Ms (Table 5.9).

Ms (Table 5.9).  Ms with time-coded quantization (Table 5.10).

Ms with time-coded quantization (Table 5.10).- Hybrid

Ms: CT/DT

Ms: CT/DT  Ms, active/passive

Ms, active/passive  Ms, digital-based

Ms, digital-based  Ms, and

Ms, and  M/Nyquist-rate ADCs (Table 5.11).

M/Nyquist-rate ADCs (Table 5.11). - Reconfigurable

Ms implemented using SC (Table 5.12) and CT circuits (Table 5.13).

Ms implemented using SC (Table 5.12) and CT circuits (Table 5.13).

Table 5.1 State-of-the-art SC single-loop single-bit LP-![]() Ms

Ms

The ![]() M ICs are sorted by FOM. Engineering notation is used for

M ICs are sorted by FOM. Engineering notation is used for ![]() and power consumption.

and power consumption.

Table 5.2 State-of-the-art SC single-loop multibit LP-![]() Ms

Ms

The ![]() M ICs are sorted by FOM. Architecture is expressed in terms of the modulator order and the number of bits/levels of the embedded quantizer. For instance, 2nd-ord(4b) represents a second-order loop filter with 4-bit quantizer and 5th-ord(33L) means a fifth-order architecture with 33-level quantizer.

M ICs are sorted by FOM. Architecture is expressed in terms of the modulator order and the number of bits/levels of the embedded quantizer. For instance, 2nd-ord(4b) represents a second-order loop filter with 4-bit quantizer and 5th-ord(33L) means a fifth-order architecture with 33-level quantizer.

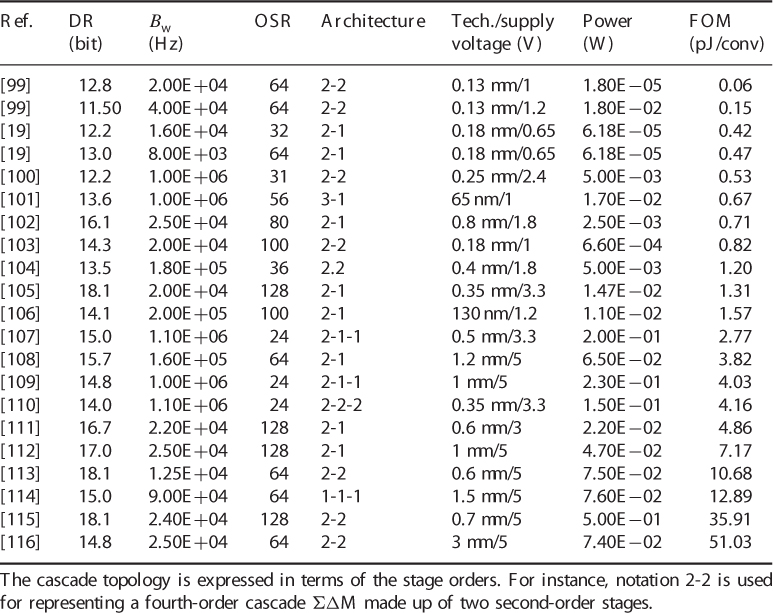

Table 5.3 State-of-the-art SC cascade single-bit LP-![]() Ms

Ms

The cascade topology is expressed in terms of the stage orders. For instance, notation 2-2 is used for representing a fourth-order cascade ![]() M made up of two second-order stages.

M made up of two second-order stages.

Table 5.4 State-of-the-art SC cascade multibit LP-![]() Ms

Ms

The number of bits per levels of the quantizer is given in parentheses. This way, notation 2-1(5L) is used for denoting a cascade 2-1 ![]() M topology with 5-level quantizer in the second stage. If no parentheses are shown, single-bit quantization is assumed in a given modulator stage.

M topology with 5-level quantizer in the second stage. If no parentheses are shown, single-bit quantization is assumed in a given modulator stage.

Table 5.5 State-of-the-art SC BP-![]() Ms

Ms

Table 5.6 State-of-the-art CT single-loop single-bit LP-![]() Ms

Ms

Table 5.7 State-of-the-art CT single-loop multibit LP-![]() Ms

Ms

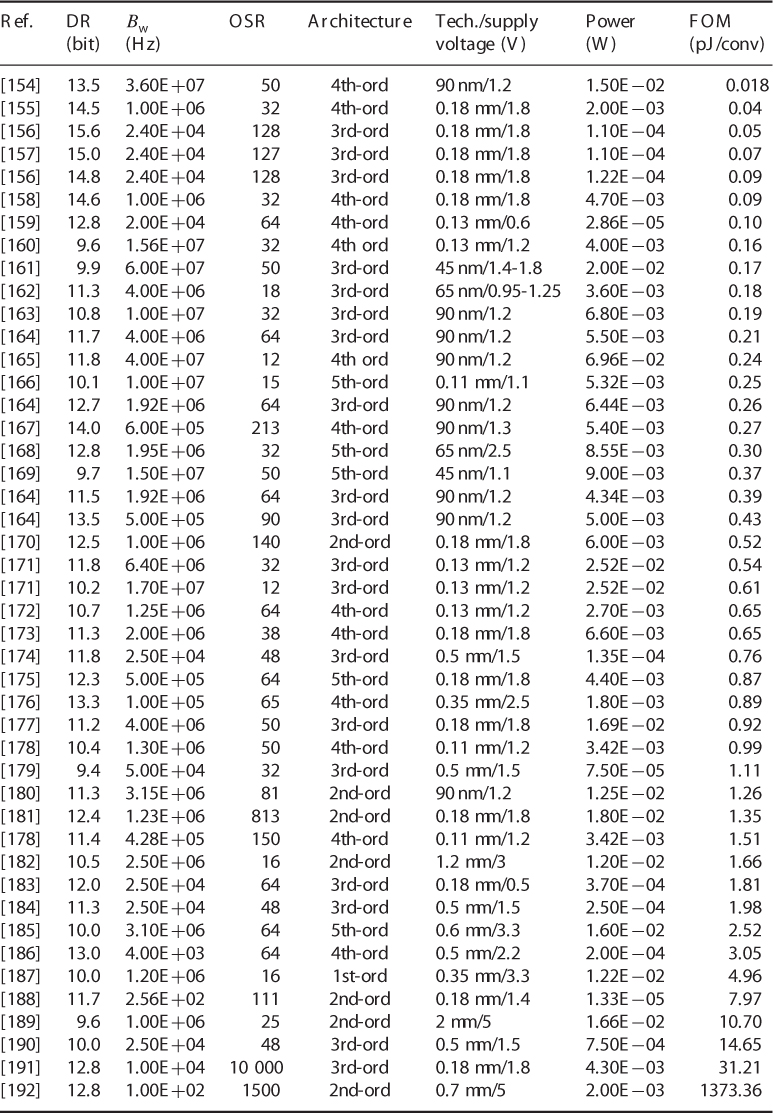

Table 5.8 State-of-the-art CT cascade LP-![]() Ms

Ms

I/Q is used for denoting a quadrature topology.

Table 5.9 State-of-the-art CT BP-![]() Ms

Ms

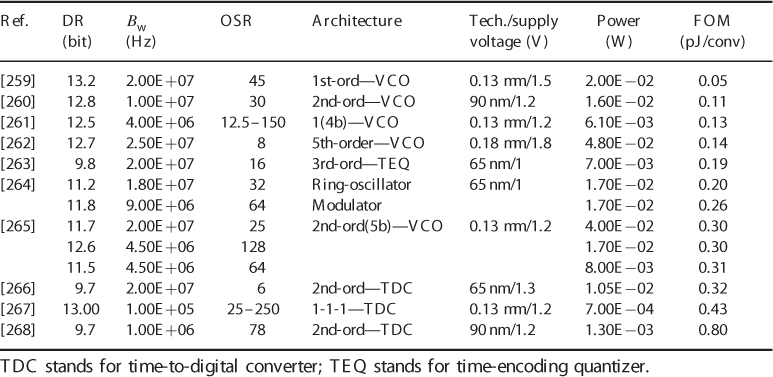

Table 5.10 State-of-the-art ![]() Ms with time-coded quantization

Ms with time-coded quantization

TDC stands for time-to-digital converter; TEQ stands for time-encoding quantizer.

Table 5.11 State-of-the-art hybrid ![]() Ms

Ms

Table 5.12 State-of-the-art SC adaptive/reconfigurable ![]() Ms

Ms

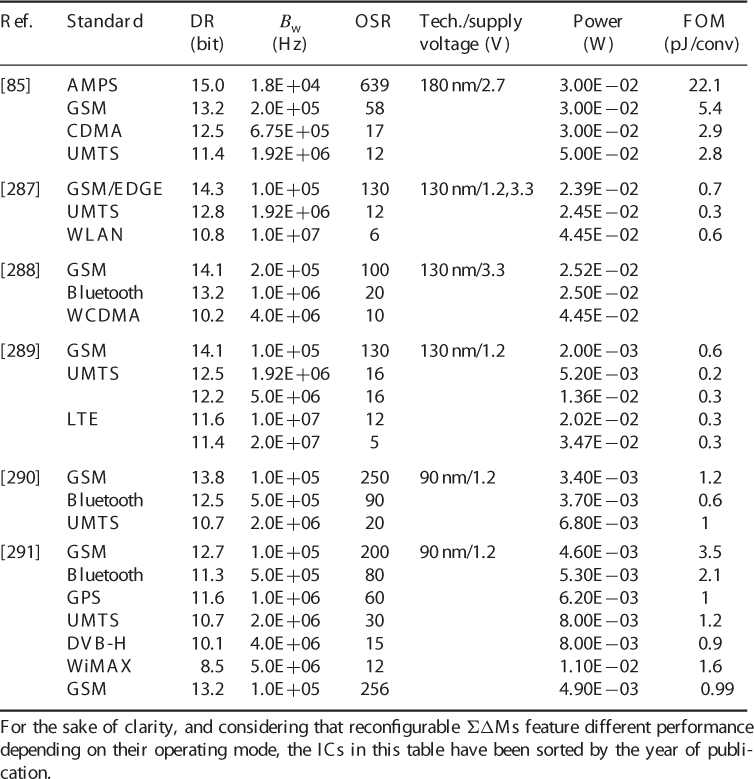

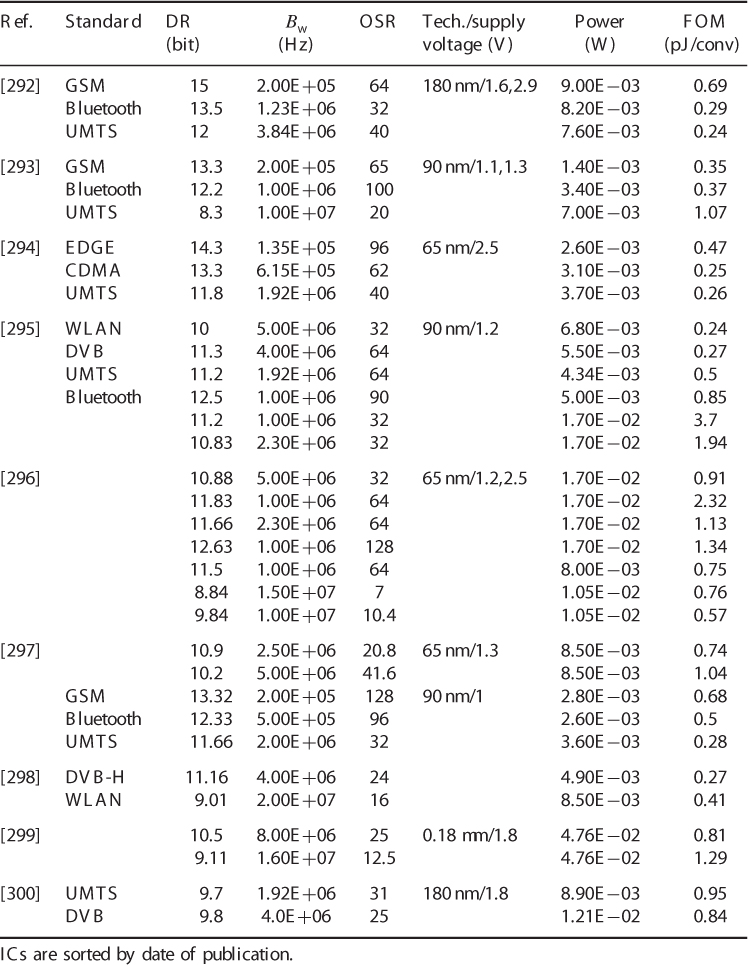

For the sake of clarity, and considering that reconfigurable ![]() Ms feature different performance depending on their operating mode, the ICs in this table have been sorted by the year of publication.

Ms feature different performance depending on their operating mode, the ICs in this table have been sorted by the year of publication.

Table 5.13 State-of-the-art CT adaptive/reconfigurable ![]() Ms

Ms

ICs are sorted by date of publication.

In all cases, the main features of each reported IC are summarized in terms of the following performance metrics: DR (measured in bits), ![]() , OSR, technology process, supply voltage, and power consumption.1 In the case of BP-

, OSR, technology process, supply voltage, and power consumption.1 In the case of BP-![]() Ms (Tables 5.5 and 5.9), the notch frequency

Ms (Tables 5.5 and 5.9), the notch frequency ![]() is also given. A schematic description of each

is also given. A schematic description of each ![]() M topology is sketched in the tables, highlighting the loop-filter order, the number of stages (in cascade

M topology is sketched in the tables, highlighting the loop-filter order, the number of stages (in cascade ![]() Ms), the number of bits of the embedded quantizer, the type of quantization technique (in time-based quantizers), the operation mode and standard covered (in the case of reconfigurable

Ms), the number of bits of the embedded quantizer, the type of quantization technique (in time-based quantizers), the operation mode and standard covered (in the case of reconfigurable ![]() Ms), etc. A more complete description of the modulators—not shown in the tables of this chapter for the sake of simplicity–can be found in the spreadsheet available on the Web.

Ms), etc. A more complete description of the modulators—not shown in the tables of this chapter for the sake of simplicity–can be found in the spreadsheet available on the Web.

5.1.1 DR-versus- Conversion Region

Conversion Region

Figure 5.1 represents DR versus ![]() for the different families of

for the different families of ![]() Ms.2 It can be noted in Figure 5.1 that a wide DR-versus-

Ms.2 It can be noted in Figure 5.1 that a wide DR-versus-![]() conversion region is covered, ranging over seven decades in frequency and 16 bit in the DR axis. The highest DR is 21 bit, which was reported in 1994 by Kerth et al. who designed a fourth-order single-loop single-bit SC-

conversion region is covered, ranging over seven decades in frequency and 16 bit in the DR axis. The highest DR is 21 bit, which was reported in 1994 by Kerth et al. who designed a fourth-order single-loop single-bit SC-![]() M in a 3-µm CMOS technology which digitized 400-Hz signals for seismic applications [48]. On the other hand, the highest value of

M in a 3-µm CMOS technology which digitized 400-Hz signals for seismic applications [48]. On the other hand, the highest value of ![]() was reported by Shibata et al. at ISSCC in February 2012. This chip consisted of a DC-to-1-GHz tunable notch-frequency sixth-order multibit LP/BP CT-

was reported by Shibata et al. at ISSCC in February 2012. This chip consisted of a DC-to-1-GHz tunable notch-frequency sixth-order multibit LP/BP CT-![]() M, implemented in a 65-nm CMOS technology, achieving 12-bit DR within a 150 MHz signal bandwidth [239].

M, implemented in a 65-nm CMOS technology, achieving 12-bit DR within a 150 MHz signal bandwidth [239].

Figure 5.1 DR-versus-![]() conversion region of state-of-the-art CMOS

conversion region of state-of-the-art CMOS ![]() Ms.

Ms.

Figure 5.2 compares the conversion region achieved by the state-of-the-art ![]() Ms with the one achieved by Nyquist-rate CMOS ADCs. The data in this figure was collected from Murmann's ADC survey [11], as well as from that used in Figure 5.1. It can be observed from Figure 5.2 that

Ms with the one achieved by Nyquist-rate CMOS ADCs. The data in this figure was collected from Murmann's ADC survey [11], as well as from that used in Figure 5.1. It can be observed from Figure 5.2 that ![]() ADCs dominate the state-of-the-art DR-versus-

ADCs dominate the state-of-the-art DR-versus-![]() front in a wide frequency range: from hundreds of hertz to hundreds of megahertz. Beyond this range, Nyquist-rate are more competitive, reporting state-of-the-art performance in high-frequency applications with signal bandwidths ranging from hundreds of megahertz to dozens of gigahertz.

front in a wide frequency range: from hundreds of hertz to hundreds of megahertz. Beyond this range, Nyquist-rate are more competitive, reporting state-of-the-art performance in high-frequency applications with signal bandwidths ranging from hundreds of megahertz to dozens of gigahertz.

Figure 5.2 Comparison of the DR-versus-![]() conversion region of

conversion region of ![]() M and Nyquist-rate ADCs. In all cases, only CMOS ICs are considered.

M and Nyquist-rate ADCs. In all cases, only CMOS ICs are considered.

Analyzing the evolution over time of the ![]() handled by

handled by ![]() Ms, it can be observed that the tendency is toward extending their range of application, particularly increasing the digitized signal bandwidth, although these designs—placed in the so-called technology front—are sometimes less power efficient, as will be discussed later. Figure 5.3 represents the

Ms, it can be observed that the tendency is toward extending their range of application, particularly increasing the digitized signal bandwidth, although these designs—placed in the so-called technology front—are sometimes less power efficient, as will be discussed later. Figure 5.3 represents the ![]() reported by

reported by ![]() Ms over time of publication for the years 1990–2012. It can be observed how

Ms over time of publication for the years 1990–2012. It can be observed how ![]() Ms have evolved from low-frequency (high-resolution) to high-frequency (medium-to-low resolution) applications. Note also that the range of

Ms have evolved from low-frequency (high-resolution) to high-frequency (medium-to-low resolution) applications. Note also that the range of ![]() is spread over time from two orders of magnitude to over six orders of magnitude. This trend benefits from the technology downscaling and it is expected to continue in the coming years.

is spread over time from two orders of magnitude to over six orders of magnitude. This trend benefits from the technology downscaling and it is expected to continue in the coming years.

Figure 5.3 ![]() spread of

spread of ![]() Ms over time for the years 1990–2012.

Ms over time for the years 1990–2012.

5.1.2 Conversion Energy and Figures of Merit

Apart from their main specifications (DR (or SNDR) and ![]() ), the efficiency of ADCs is quantified in terms of the power consumption required to achieve these specifications. Taking all these ingredients into account, the amount of energy per converted sample

), the efficiency of ADCs is quantified in terms of the power consumption required to achieve these specifications. Taking all these ingredients into account, the amount of energy per converted sample ![]() —also referred to as conversion energy [5]—can be calculated as [5, 9],

—also referred to as conversion energy [5]—can be calculated as [5, 9],

5.1 ![]()

where ![]() is the power consumption and

is the power consumption and ![]() represents the digital output rate of the ADC, that is, the Nyquist rate, measured in samples per second (S/s).

represents the digital output rate of the ADC, that is, the Nyquist rate, measured in samples per second (S/s).

Thus, it is common to analyze and graphically represent the efficiency of ADCs in the form of plots of conversion energy versus DR or SNDR—also known as energy plots [5, 10]. As an illustration, Figure 5.4 shows the energy plot of state-of-the-art ![]() Ms. Note that, in order to compute the overall performance achieved by a given

Ms. Note that, in order to compute the overall performance achieved by a given ![]() M, both magnitudes involved in Figure 5.4—that is, the conversion energy

M, both magnitudes involved in Figure 5.4—that is, the conversion energy ![]() and the resolution (expressed in terms of either DR or SNDR)—must be taken into account. As expected, there is a direct relationship between DR and

and the resolution (expressed in terms of either DR or SNDR)—must be taken into account. As expected, there is a direct relationship between DR and ![]() , so that the larger the resolution, the more conversion energy is needed.

, so that the larger the resolution, the more conversion energy is needed.

Figure 5.4 Energy plot of state-of-the-art ![]() Ms.

Ms.

It is therefore convenient to express the trade-off highlighted in Figure 5.4 between the conversion energy and DR in a single performance metric to quantify the performance of a given ![]() M and to compare the performance of different ADC architectures. Such a performance metric is often referred to as figure of merit (

M and to compare the performance of different ADC architectures. Such a performance metric is often referred to as figure of merit (![]() ), and accounts in a single formula the three basic specifications of an ADC, namely effective resolution, signal bandwidth, and power consumption.

), and accounts in a single formula the three basic specifications of an ADC, namely effective resolution, signal bandwidth, and power consumption.

Choosing the appropriate ![]() is always a matter of debate and discussion. Among others, the following expressions that relate

is always a matter of debate and discussion. Among others, the following expressions that relate ![]() with ENOB have been most frequently used for comparing the performance of ADCs [4, 102, 301]

with ENOB have been most frequently used for comparing the performance of ADCs [4, 102, 301]

5.2 ![]()

5.3 ![]()

where ![]() is the Boltzmann constant and

is the Boltzmann constant and ![]() is the chip temperature (measured in Kelvin).

is the chip temperature (measured in Kelvin).

Note that ![]() emphasizes power consumption, whereas

emphasizes power consumption, whereas ![]() emphasizes effective resolution. Therefore, the smaller the

emphasizes effective resolution. Therefore, the smaller the ![]() value and the larger the

value and the larger the ![]() value, the “better” the ADC is. In this chapter,

value, the “better” the ADC is. In this chapter, ![]() has been selected because it has been the most commonly used FOM in the recent years by the majority of the

has been selected because it has been the most commonly used FOM in the recent years by the majority of the ![]() M community. It should be noted that according to the definition of ENOB given in Equation 1.20, DR was used for computing ENOB and consequently for the value of

M community. It should be noted that according to the definition of ENOB given in Equation 1.20, DR was used for computing ENOB and consequently for the value of ![]() as shown in Tables 5.13. However, in those

as shown in Tables 5.13. However, in those ![]() M ICs presenting a strongly nonlinear behavior, the effective resolution (i.e., ENOB) is indeed limited by the peak SNDR, as stated in Chapter 1 and hence, its corresponding

M ICs presenting a strongly nonlinear behavior, the effective resolution (i.e., ENOB) is indeed limited by the peak SNDR, as stated in Chapter 1 and hence, its corresponding ![]() is worse than the one shown in the tables. However, the purpose of this chapter is to analyze the overall performance and trends of

is worse than the one shown in the tables. However, the purpose of this chapter is to analyze the overall performance and trends of ![]() ADCs, instead of the specifications achieved by a particular design. From this perspective, and considering that not all authors reported all data required to compute

ADCs, instead of the specifications achieved by a particular design. From this perspective, and considering that not all authors reported all data required to compute ![]() , the analysis was based on expressions of

, the analysis was based on expressions of ![]() derived from DR, instead of from SNDR.

derived from DR, instead of from SNDR.

Thus, following an approach similar to that proposed by Murmann [5], the results reported by state-of-the-art performance ![]() Ms are compared in Figure 5.4 with two straight lines for the numerical examples of

Ms are compared in Figure 5.4 with two straight lines for the numerical examples of ![]() 100 fJ/conversion-step and 10 fJ/conversion-step. Note that the majority of

100 fJ/conversion-step and 10 fJ/conversion-step. Note that the majority of ![]() Ms reaching the lowest values of

Ms reaching the lowest values of ![]() are placed between both lines and correspond to CT circuit implementations, showing the best efficiency of these kinds of

are placed between both lines and correspond to CT circuit implementations, showing the best efficiency of these kinds of ![]() Ms for resolutions in the order of 11–15-bit DR within 1–100 MHz bandwidths, as will be discussed later in this chapter.

Ms for resolutions in the order of 11–15-bit DR within 1–100 MHz bandwidths, as will be discussed later in this chapter.

Figure 5.5 represents ![]() versus

versus ![]() for the different

for the different ![]() M architectures included in Tables 5.13. It can be seen how CT-

M architectures included in Tables 5.13. It can be seen how CT-![]() Ms obtain better performance than SC-

Ms obtain better performance than SC-![]() Ms for

Ms for ![]() MHz, while SC-

MHz, while SC-![]() Ms are more efficient for lower values of

Ms are more efficient for lower values of ![]() . In terms of architectures, it can be noted how LP-

. In terms of architectures, it can be noted how LP-![]() Ms obtain better values of

Ms obtain better values of ![]() than BP-

than BP-![]() Ms. This is due to the fact that CT BP-

Ms. This is due to the fact that CT BP-![]() Ms digitize signals placed at a notch frequency

Ms digitize signals placed at a notch frequency ![]() , which in the majority of cases is in the order of hundreds of megahertz and even in the gigahertz range (Table 5.9). However, this parameter is not considered in

, which in the majority of cases is in the order of hundreds of megahertz and even in the gigahertz range (Table 5.9). However, this parameter is not considered in ![]() , which penalizes its performance compared to LP-

, which penalizes its performance compared to LP-![]() Ms as will be discussed later.

Ms as will be discussed later.

Figure 5.5 ![]() versus

versus ![]() corresponding to the state-of-the-art

corresponding to the state-of-the-art ![]() Ms under study.

Ms under study.

Figure 5.6 compares the value of ![]() achieved by state-of-the-art

achieved by state-of-the-art ![]() Ms with that achieved by Nyquist-rate ADCs. Note that

Ms with that achieved by Nyquist-rate ADCs. Note that ![]() Ms show a competitive performance in a wide range of

Ms show a competitive performance in a wide range of ![]() , from hundreds of hertz to hundreds of megahertz. Only SAR ADCs achieve lower values of

, from hundreds of hertz to hundreds of megahertz. Only SAR ADCs achieve lower values of ![]() within the interval 10 kHz

within the interval 10 kHz ![]() 10 MHz. Pipeline ADCs are the best choice for those applications with 100 MHz

10 MHz. Pipeline ADCs are the best choice for those applications with 100 MHz ![]() 1 GHz, whereas flash ADCs dominate for

1 GHz, whereas flash ADCs dominate for ![]() 1 GHz.

1 GHz.

Figure 5.6 Comparison of ![]() ADCs and Nyquist-rate ADCs in terms of

ADCs and Nyquist-rate ADCs in terms of ![]() versus

versus ![]() .

.

In terms of conversion energy, (as illustrated in Figure 5.7), ![]() ADCs are more efficient than SAR and pipeline ADCs for applications requiring DR

ADCs are more efficient than SAR and pipeline ADCs for applications requiring DR ![]() 12 bit, while SAR ADCs require the lowest conversion energy within the 8–12-bit resolution interval.

12 bit, while SAR ADCs require the lowest conversion energy within the 8–12-bit resolution interval.

Figure 5.7 Comparison of energy plot of state-of-the-art ![]() Ms, SAR, and pipeline ADCs.

Ms, SAR, and pipeline ADCs.

5.2 Empirical and Statistical Analysis of State-of-the-Art  Ms

Ms

Analyzing in detail the data included in Tables 5.13, a number of interesting conclusions can be drawn. This section aims to identify practical pieces of information that can be used as guidelines for designers to make a better decision on the best architecture and circuit technique for a given set of specifications.

5.2.1 SC versus CT State-of-the-Art  Ms

Ms

Although SC circuit technique has been traditionally used in most reported ![]() Ms, more and more ICs are being implemented using CT circuits, especially in those applications targeting broadband signals and/or requiring low power consumption. Overall, approximately 57

Ms, more and more ICs are being implemented using CT circuits, especially in those applications targeting broadband signals and/or requiring low power consumption. Overall, approximately 57![]() of

of ![]() M ICs included in this survey are implemented using SC circuits, whereas 43

M ICs included in this survey are implemented using SC circuits, whereas 43![]() of them are CT-

of them are CT-![]() Ms. However, as illustrated in Figure 5.8, there is a tendency, in recent years, to use CT techniques. This trend is expected to continue as this kind of

Ms. However, as illustrated in Figure 5.8, there is a tendency, in recent years, to use CT techniques. This trend is expected to continue as this kind of ![]() Ms will benefit from the technology downscaling process and the increase in transition frequency. Indeed, the decrease in voltage supplies (and consequently the voltage headroom) together with the increasing use of digital signal processing and calibration techniques are favoring the implementation of CT-

Ms will benefit from the technology downscaling process and the increase in transition frequency. Indeed, the decrease in voltage supplies (and consequently the voltage headroom) together with the increasing use of digital signal processing and calibration techniques are favoring the implementation of CT-![]() Ms in nanometer CMOS processes, increasing their operating frequency more and more [10].

Ms in nanometer CMOS processes, increasing their operating frequency more and more [10].

Figure 5.8 Number of SC- and CT-![]() Ms published for the years 1990–2012.

Ms published for the years 1990–2012.

Figure 5.9a represents the aperture plot [5] (i.e., ![]() vs DR) corresponding to the state-of-the-art SC- and CT-

vs DR) corresponding to the state-of-the-art SC- and CT-![]() Ms. Note that two state-of-the-art fronts (highlighted in the figure) can be clearly identified. One front—dominated by CT-

Ms. Note that two state-of-the-art fronts (highlighted in the figure) can be clearly identified. One front—dominated by CT-![]() Ms—goes from approximately 10-bit to 14-bit DR, covering a

Ms—goes from approximately 10-bit to 14-bit DR, covering a ![]() range from 10 to 150 MHz. The other front—covered by SC-

range from 10 to 150 MHz. The other front—covered by SC-![]() Ms—goes from 14-bit to 21-bit DR with

Ms—goes from 14-bit to 21-bit DR with ![]() ranging from 400 Hz to 2 MHz. Therefore, as could be logically expected, it can be empirically deduced from these results that CT-

ranging from 400 Hz to 2 MHz. Therefore, as could be logically expected, it can be empirically deduced from these results that CT-![]() Ms are more suitable for medium-resolution (10–14 bit) and medium–high bandwidths (10–100 MHz), whereas SC-

Ms are more suitable for medium-resolution (10–14 bit) and medium–high bandwidths (10–100 MHz), whereas SC-![]() Ms are more appropriate for applications requiring high-resolutions (15–20 bit) within low-medium bandwidths (100 Hz–1 MHz).

Ms are more appropriate for applications requiring high-resolutions (15–20 bit) within low-medium bandwidths (100 Hz–1 MHz).

Figure 5.9 Comparison between state-of-the-art SC- and CT-![]() Ms: (a) aperture plot (

Ms: (a) aperture plot (![]() versus DR) and (b) energy plot (

versus DR) and (b) energy plot (![]() versus

versus ![]() ).

).

The resolution-versus-bandwidth regions covered by the state-of-the-art fronts drawn in Figure 5.9a define the application areas where SC- and CT-![]() Ms are more efficient. This is illustrated in Figure 5.9b, where the energy plot is compared for both circuit techniques. Overall, it can be concluded that CT-

Ms are more efficient. This is illustrated in Figure 5.9b, where the energy plot is compared for both circuit techniques. Overall, it can be concluded that CT-![]() Ms are more efficient than SC-

Ms are more efficient than SC-![]() Ms for

Ms for ![]() .

.

5.2.2 Gm-C versus Active-RC State-of-the-Art CT- Ms

Ms

As already discussed in this book, CT-![]() Ms can be implemented using either active-RC or Gm-C integrators. Active-RC integrators have the advantages of better linearity and larger signal swing, whereas Gm-C integrators are potentially faster with less power consumption, at the price of reducing their linearity as compared to active-RC integrators [302]. In practice, the majority of state-of-the-art CT-

Ms can be implemented using either active-RC or Gm-C integrators. Active-RC integrators have the advantages of better linearity and larger signal swing, whereas Gm-C integrators are potentially faster with less power consumption, at the price of reducing their linearity as compared to active-RC integrators [302]. In practice, the majority of state-of-the-art CT-![]() Ms have been implemented using active-RC integrators. Sometimes an active-RC front-end integrator is chosen for its better linearity, whereas the rest integrators of the

Ms have been implemented using active-RC integrators. Sometimes an active-RC front-end integrator is chosen for its better linearity, whereas the rest integrators of the ![]() M loop-filter are of Gm-C type. This is the most common situation in LP-

M loop-filter are of Gm-C type. This is the most common situation in LP-![]() Ms, while most BP-

Ms, while most BP-![]() Ms operating at notch frequencies in the order of hundreds of megahertz or in the gigahertz band, have been implemented using either Gm-C or Gm-LC integrators.

Ms operating at notch frequencies in the order of hundreds of megahertz or in the gigahertz band, have been implemented using either Gm-C or Gm-LC integrators.

Figure 5.10a illustrates the conversion region covered by the different CT circuit techniques by showing the aperture plot of state-of-the-art CT-![]() Ms. For the sake of clarity, the different families of CT-

Ms. For the sake of clarity, the different families of CT-![]() Ms have been organized into three categories: Gm-C, active-RC, and active-RC/Gm-C. The latter assumes that only the front-end integrator is active-RC while the remaining ones in the modulator chain are implemented using Gm-C techniques. It can be noted that the state-of-the-art front (highlighted in the figure) is dominated by active-RC implementations.

Ms have been organized into three categories: Gm-C, active-RC, and active-RC/Gm-C. The latter assumes that only the front-end integrator is active-RC while the remaining ones in the modulator chain are implemented using Gm-C techniques. It can be noted that the state-of-the-art front (highlighted in the figure) is dominated by active-RC implementations.

Figure 5.10 Gm-C versus active-RC CT-![]() Ms: (a) aperture plot and (b)

Ms: (a) aperture plot and (b) ![]() versus

versus ![]() .

.

In terms of ![]() , active-RC CT-

, active-RC CT-![]() Ms have demonstrated to be more efficient than Gm-C implementations, as illustrated in Figure 5.10b. It can be shown how active-RC

Ms have demonstrated to be more efficient than Gm-C implementations, as illustrated in Figure 5.10b. It can be shown how active-RC ![]() Ms obtain lower values of

Ms obtain lower values of ![]() in a wide range of

in a wide range of ![]() —from 100 kHz to almost 100 MHz.

—from 100 kHz to almost 100 MHz.

5.2.3 Technology Used in State-of-the-Art  Ms

Ms

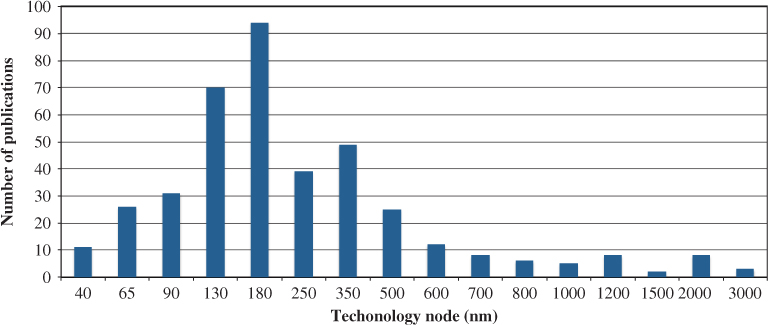

A variety of CMOS processes can be distinguished in Tables 5.13. These technologies have been used in the last 20 years by state-of-the-art ![]() Ms—going from micrometer CMOS (3-µm technology node) down to nanometer processes (40 nm). Supply voltages have scaled down with technology evolution from

Ms—going from micrometer CMOS (3-µm technology node) down to nanometer processes (40 nm). Supply voltages have scaled down with technology evolution from ![]() 6.5 to 0.5 V. As an illustration, Figure 5.11 shows an histogram of the CMOS technologies employed by the

6.5 to 0.5 V. As an illustration, Figure 5.11 shows an histogram of the CMOS technologies employed by the ![]() Ms considered in this survey. Note that 180-nm CMOS process has been the technology node most commonly employed in recent years, mainly using a single 1.8-V supply voltage.

Ms considered in this survey. Note that 180-nm CMOS process has been the technology node most commonly employed in recent years, mainly using a single 1.8-V supply voltage.

Figure 5.11 Histogram of CMOS technologies used by state-of-the-art ![]() Ms.

Ms.

As discussed in Section 5.1.1, ![]() Ms have demonstrated state-of-the-art performance in many diverse processes, taking advantage of the technology downscaling to create the conditions to increase their conversion region. This is illustrated in Figure 5.12, where

Ms have demonstrated state-of-the-art performance in many diverse processes, taking advantage of the technology downscaling to create the conditions to increase their conversion region. This is illustrated in Figure 5.12, where ![]() is represented over the technology node. Note that the minimum value of

is represented over the technology node. Note that the minimum value of ![]() achieved by

achieved by ![]() Ms decreases with the technology downscaling, reaching the lowest values for 180-nm CMOS processes.

Ms decreases with the technology downscaling, reaching the lowest values for 180-nm CMOS processes.

Figure 5.12 ![]() versus CMOS process nodes from

versus CMOS process nodes from ![]() m to 40 nm.

m to 40 nm.

5.2.4 Single-Loop versus Cascade State-of-the-Art  Ms

Ms

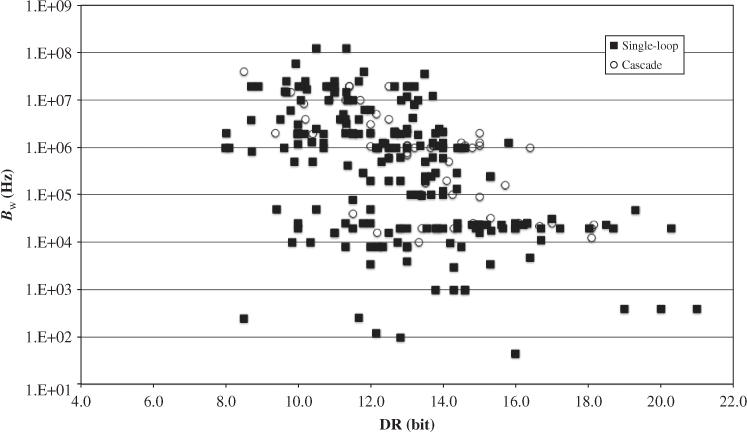

Single-loop architectures have been more used than cascade topologies. Overall, approximately 80![]() of the state-of-the-art

of the state-of-the-art ![]() M ICs considered in this survey are single-loop topologies, whereas only 20

M ICs considered in this survey are single-loop topologies, whereas only 20![]() of them are cascades. The latter have been mainly implemented using SC circuits, although recent synthesis methods are making the implementation of CT cascade ICs possible.

of them are cascades. The latter have been mainly implemented using SC circuits, although recent synthesis methods are making the implementation of CT cascade ICs possible.

In terms of the loop-filter order of single-loop architectures, the second-order topology was the most used by SC-![]() Ms, in

Ms, in ![]() of single-bit architectures and

of single-bit architectures and ![]() of multibit topologies (Tables 5.1 and 5.2). In the case of CT implementations, third- and fourth-order topologies were preferred by single-bit topologies, in

of multibit topologies (Tables 5.1 and 5.2). In the case of CT implementations, third- and fourth-order topologies were preferred by single-bit topologies, in ![]() and

and ![]() of cases, respectively (Table 5.6). In the case of multibit implementations, loop-filter orders higher than three were implemented in

of cases, respectively (Table 5.6). In the case of multibit implementations, loop-filter orders higher than three were implemented in ![]() of ICs, taking advantage of the better stability properties of high-order (

of ICs, taking advantage of the better stability properties of high-order (![]() ) implementations with multibit quantization.

) implementations with multibit quantization.

As far as the cascade topologies are concerned (Tables 5.4, and 5.8), the majority of implementations used a fourth-order loop-filter with two stages in a 2-2 configuration or three stages in a 2-1-1 configuration. Third-order 2-1 implementations are also used by SC cascades in ![]() of cases, as shown in Tables 5.3 and 5.4.

of cases, as shown in Tables 5.3 and 5.4.

Figure 5.13 compares the aperture plot of single-loop and cascade state-of-the-art ![]() Ms. It is noted how single-loop dominates almost all ranges of applications from low-bandwidth high-resolution to broadband low-medium resolution. However, as discussed in Section 5.3.1, enhanced techniques are improving the performance of cascade architectures, which may be very suited to implement reconfigurable/adaptive ADCs, thus taking advantage of the very modular nature of the cascade topology.

Ms. It is noted how single-loop dominates almost all ranges of applications from low-bandwidth high-resolution to broadband low-medium resolution. However, as discussed in Section 5.3.1, enhanced techniques are improving the performance of cascade architectures, which may be very suited to implement reconfigurable/adaptive ADCs, thus taking advantage of the very modular nature of the cascade topology.

Figure 5.13 Aperture plot of single-loop and cascade state-of-the-art ![]() Ms. Band-pass, hybrid, and reconfigurable

Ms. Band-pass, hybrid, and reconfigurable ![]() Ms are not included in this plot.

Ms are not included in this plot.

5.2.5 Single-Bit versus Multibit State-of-the-Art  Ms

Ms

Multibit quantization is in general more employed than single-bit quantization. The majority of cascade topologies include dual quantization with a multibit quantizer in the last stage in order to attenuate the impact of the nonlinearity of the feedback DAC. However, increasingly more cascade ICs are including internal quantizers with ![]() ranging from 2 to 5 bit in all stages combined with proper linearization techniques. In addition, a number of

ranging from 2 to 5 bit in all stages combined with proper linearization techniques. In addition, a number of ![]() M ICs are including trilevel quantizers to benefit from the extra level provided by fully differential circuit implementation of the embedded flash ADCs, while keeping an inherent linear behavior of the feedback DAC.

M ICs are including trilevel quantizers to benefit from the extra level provided by fully differential circuit implementation of the embedded flash ADCs, while keeping an inherent linear behavior of the feedback DAC.

In terms of conversion energy, there are more single-bit ![]() Ms than multibit

Ms than multibit ![]() Ms achieving a

Ms achieving a ![]() 100 fJ/conversion-step, as illustrated in the energy plot shown in Figure 5.14a. Although multibit implementations can also achieve a good efficiency for resolutions in the order of 12–16 bit, there are more single-bit solutions reaching state-of-the-art performance within this range.

100 fJ/conversion-step, as illustrated in the energy plot shown in Figure 5.14a. Although multibit implementations can also achieve a good efficiency for resolutions in the order of 12–16 bit, there are more single-bit solutions reaching state-of-the-art performance within this range.

Figure 5.14 Single-bit versus multibit state-of-the-art ![]() Ms: (a) energy plot and (b) aperture plot.

Ms: (a) energy plot and (b) aperture plot.

Figure 5.14b compares the aperture plot of single-bit and multibit ![]() Ms. It is shown how multibit modulators dominate the state-of-the-art fronts except for those applications with resolutions over 20 bit within signal bandwidths below 1 kHz. Indeed, a number of CT-

Ms. It is shown how multibit modulators dominate the state-of-the-art fronts except for those applications with resolutions over 20 bit within signal bandwidths below 1 kHz. Indeed, a number of CT-![]() Ms intended for broadband communications use multibit quantization. Apart from the obvious benefits in terms of the increased number of bits, multibit quantization (and NRZ DAC) is also appealing in practice for its lower sensitivity to clock jitter error, as discussed in Chapter 2. However, the price to pay for using multibit quantization is the inherent nonlinear operation of the multibit feedback DAC, what forces using linearization techniques, with the subsequent penalty in power consumption, speed limitation, and circuit complexity. To address this problem, some authors propose the use of alternative implementations of the modulator feedback waveforms—such as DACs with finite impulsive response (FIR) [154, 161]—to reduce the sensitivity to clock jitter and to relax the

Ms intended for broadband communications use multibit quantization. Apart from the obvious benefits in terms of the increased number of bits, multibit quantization (and NRZ DAC) is also appealing in practice for its lower sensitivity to clock jitter error, as discussed in Chapter 2. However, the price to pay for using multibit quantization is the inherent nonlinear operation of the multibit feedback DAC, what forces using linearization techniques, with the subsequent penalty in power consumption, speed limitation, and circuit complexity. To address this problem, some authors propose the use of alternative implementations of the modulator feedback waveforms—such as DACs with finite impulsive response (FIR) [154, 161]—to reduce the sensitivity to clock jitter and to relax the ![]() M loop-filter linearity specifications, giving rise to a more competitive performance.

M loop-filter linearity specifications, giving rise to a more competitive performance.

5.2.6 Low-Pass versus Band-Pass State-of-the-Art  Ms

Ms

As stated in Section 5.1.2, LP-![]() Ms obtain better performance in terms of

Ms obtain better performance in terms of ![]() than BP-

than BP-![]() Ms. This is better illustrated in Figure 5.15, which compares

Ms. This is better illustrated in Figure 5.15, which compares ![]() of LP- and BP-

of LP- and BP-![]() Ms. Figure 5.16a shows the aperture plot of LP- and BP-

Ms. Figure 5.16a shows the aperture plot of LP- and BP-![]() Ms. Note that the state-of-the-art front is dominated by LP-

Ms. Note that the state-of-the-art front is dominated by LP-![]() Ms, although the highest values of

Ms, although the highest values of ![]() have been reached by BP-

have been reached by BP-![]() Ms.

Ms.

Figure 5.15 Comparison of LP- and BP-![]() Ms:

Ms: ![]() and

and ![]() versus

versus ![]() .

.

Figure 5.16 LP-![]() Ms versus BP-

Ms versus BP-![]() Ms: (a) aperture plot, (b) energy plot, and (c)

Ms: (a) aperture plot, (b) energy plot, and (c) ![]() versus

versus ![]() .

.

Comparing the energy plot of both types of ![]() Ms, it can be shown that LP-

Ms, it can be shown that LP-![]() Ms consume less energy per conversion-step than BP-

Ms consume less energy per conversion-step than BP-![]() Ms, as illustrated in Figure 5.16b, where all

Ms, as illustrated in Figure 5.16b, where all ![]() Ms with

Ms with ![]() 100 fJ/conversion-step are of LP type. However, it should be noted that

100 fJ/conversion-step are of LP type. However, it should be noted that ![]() might not be adequate for quantifying the efficiency of BP-

might not be adequate for quantifying the efficiency of BP-![]() Ms, because

Ms, because ![]() may not always be representative of the operating frequency of the modulator. For instance, looking at Table 5.9, it can be noted that there are several ICs digitizing signals with

may not always be representative of the operating frequency of the modulator. For instance, looking at Table 5.9, it can be noted that there are several ICs digitizing signals with ![]() in the order of 10–20 MHz but placed at center (notch) frequencies in the order of gigahertz. For that reason some authors propose alternative FOMs such as the following one [303]:

in the order of 10–20 MHz but placed at center (notch) frequencies in the order of gigahertz. For that reason some authors propose alternative FOMs such as the following one [303]:

5.4 ![]()

which takes into account not only ![]() , but also the notch frequency

, but also the notch frequency ![]() . As illustrated in Figure 5.15, the use of

. As illustrated in Figure 5.15, the use of ![]() increases the number of state-of-the-art performance BP-

increases the number of state-of-the-art performance BP-![]() Ms, although the comparison may be not fair in this case for LP-

Ms, although the comparison may be not fair in this case for LP-![]() Ms.

Ms.

Figure 5.16c compares the performance of LP- and BP-![]() Ms, based on the following FOM proposed by Schreier and Temes [2]:

Ms, based on the following FOM proposed by Schreier and Temes [2]:

5.5 ![]()

To be consistent with the rest of the FOMs considered in this chapter, SNDR is replaced with DR in the above expression. Note that ![]() increases its value for better performing designs. The horizontal dashed line in Figure 5.16c was called the architecture front by Schreier and Temes, while the vertical front is named technology front. The former is absolutely dominated by LP-

increases its value for better performing designs. The horizontal dashed line in Figure 5.16c was called the architecture front by Schreier and Temes, while the vertical front is named technology front. The former is absolutely dominated by LP-![]() Ms, while the most advanced architectures in the technology front are BP-

Ms, while the most advanced architectures in the technology front are BP-![]() M topologies. The latter push the technology process to its limits in terms of digitized signal bandwidth and sampling frequency, at the price of being less efficient in terms of power dissipation. As discussed in the next section, the new generations of BP-

M topologies. The latter push the technology process to its limits in terms of digitized signal bandwidth and sampling frequency, at the price of being less efficient in terms of power dissipation. As discussed in the next section, the new generations of BP-![]() Ms are taking advantage of technology downscaling to push

Ms are taking advantage of technology downscaling to push ![]() Ms forward in terms of speed and efficiency.

Ms forward in terms of speed and efficiency.

5.3 Cutting-Edge  M Architectures and Techniques

M Architectures and Techniques

To conclude this survey, this section presents a review of some of the most relevant cutting-edge ![]() M topologies that are in the frontiers of the

M topologies that are in the frontiers of the ![]() M designs, identifying their most significant trends, challenges, and practical solutions. The following architecture/circuit techniques are overviewed:

M designs, identifying their most significant trends, challenges, and practical solutions. The following architecture/circuit techniques are overviewed:

- Sturdy MASH (SMASH) architectures

- Hybrid

M architectures, including

M architectures, including  M-Nyquist ADCs, active–passive CT-

M-Nyquist ADCs, active–passive CT- Ms, CT/DT circuit implementations

Ms, CT/DT circuit implementations - Multirate

Ms

Ms - Multibit

Ms with time-coded quantization

Ms with time-coded quantization  Ms implemented with digital-based circuit techniques

Ms implemented with digital-based circuit techniques- Adaptive/reconfigurable

Ms

Ms - Ultra-high-speed

Ms for RF digitization.

Ms for RF digitization.

A detailed explanation of the aforementioned ![]() Ms is beyond the scope of this book. Instead, this section provides an overview of their most significant features, with emphasis on their advantages/drawbacks, design trends, and challenges.

Ms is beyond the scope of this book. Instead, this section provides an overview of their most significant features, with emphasis on their advantages/drawbacks, design trends, and challenges.

5.3.1 SMASH  M Architectures

M Architectures

One of the main limitations of cascade ![]() Ms is their higher sensitivity to mismatch than their single-loop counterparts. This may explain why a vast majority of state-of-the-art

Ms is their higher sensitivity to mismatch than their single-loop counterparts. This may explain why a vast majority of state-of-the-art ![]() M ICs (∼

M ICs (∼![]() ) were implemented using single-loop architectures as stated in Section 5.2.4. This limitation has motivated

) were implemented using single-loop architectures as stated in Section 5.2.4. This limitation has motivated ![]() designers to look for alternative implementations of cascade

designers to look for alternative implementations of cascade ![]() Ms that reduce the sensitivity to noise leakages.

Ms that reduce the sensitivity to noise leakages.

An interesting alternative cascade ![]() topology is the so-called Sturdy MASH (SMASH) [304, 305]. The main idea behind this kind of cascade

topology is the so-called Sturdy MASH (SMASH) [304, 305]. The main idea behind this kind of cascade ![]() Ms consists of replacing the DCL by the own analog processing provided by the loop-filter integrators together with an additional interstage digital feedback path. As a result, the modulator output can be obtained from a direct digital addition (or subtraction) operation of the different stage outputs in the cascade, with no need for a DCL as in conventional cascades, and the subsequent elimination of matching requirements between the analog and the digital filtering.

Ms consists of replacing the DCL by the own analog processing provided by the loop-filter integrators together with an additional interstage digital feedback path. As a result, the modulator output can be obtained from a direct digital addition (or subtraction) operation of the different stage outputs in the cascade, with no need for a DCL as in conventional cascades, and the subsequent elimination of matching requirements between the analog and the digital filtering.

Figure 5.17 shows the conceptual block diagram of a two-stage SMASH ![]() M.3 Assuming a linear model for the embedded quantizers, the

M.3 Assuming a linear model for the embedded quantizers, the ![]() -transform of the modulator output can be written as [305],

-transform of the modulator output can be written as [305],

where ![]() and

and ![]() represent the NTF and STF of the

represent the NTF and STF of the ![]() th stage in the cascade, respectively. Note that the overall NTF of the cascade modulator—that is, the NTF filtering the second-stage quantization error

th stage in the cascade, respectively. Note that the overall NTF of the cascade modulator—that is, the NTF filtering the second-stage quantization error ![]() —is the same as that of a conventional cascade

—is the same as that of a conventional cascade ![]() M. However, the first-stage quantization error is not completely canceled. Instead, it is filtered by

M. However, the first-stage quantization error is not completely canceled. Instead, it is filtered by ![]() .

.

Figure 5.17 Conceptual block diagram of a two-stage SMASH ![]() M [304, 305].

M [304, 305].

Figure 5.18 illustrates how to implement the concept of SMASH ![]() Ms in a fourth-order 2-2 topology [305]. Note that the DCL is replaced by direct feedback paths from the output of the second stage to the input of the first stage, although an additional feedback DAC is required. Analyzing Figure 5.18 considering linear models for the quantizers, it is easy to show that the

Ms in a fourth-order 2-2 topology [305]. Note that the DCL is replaced by direct feedback paths from the output of the second stage to the input of the first stage, although an additional feedback DAC is required. Analyzing Figure 5.18 considering linear models for the quantizers, it is easy to show that the ![]() -transform of the modulator output is given by:

-transform of the modulator output is given by:

5.7 ![]()

Figure 5.18 Block diagram of a 2-2 SMASH ![]() M proposed in [305].

M proposed in [305].

Note from the above expression that a fourth-order high-pass filtering is obtained for both ![]() and

and ![]() . In this case,

. In this case, ![]() , which according to Equation 5.6, does not give a complete cancelation of

, which according to Equation 5.6, does not give a complete cancelation of ![]() . However,

. However, ![]() can be ideally canceled if

can be ideally canceled if ![]() , that is, if unity STF (USTF) [307, 308] is implemented in the second stage of the SMASH topology. Indeed, the performance of SMASH

, that is, if unity STF (USTF) [307, 308] is implemented in the second stage of the SMASH topology. Indeed, the performance of SMASH ![]() Ms can be notably improved if USTF is used in all stages of the modulator, as proposed in [288]. As stated in Chapter 1, the main advantage of using USTF is that integrators ideally process quantization error only and hence, their output swing can be reduced and the tolerance to amplifiers nonlinearities is increased. However, one of the main drawbacks of applying USTF to CT-

Ms can be notably improved if USTF is used in all stages of the modulator, as proposed in [288]. As stated in Chapter 1, the main advantage of using USTF is that integrators ideally process quantization error only and hence, their output swing can be reduced and the tolerance to amplifiers nonlinearities is increased. However, one of the main drawbacks of applying USTF to CT-![]() Ms is that the resulting modulators do feature a worse implicit AAF function.

Ms is that the resulting modulators do feature a worse implicit AAF function.

Figure 5.19 shows a ![]() M architecture that extends the underlying principle of SMASH

M architecture that extends the underlying principle of SMASH ![]() Ms to the implementation of USTF in both stages, thus taking advantage of both strategies (SMASH and USTF) to achieve higher resolution in wideband applications with lower values of OSR. In this example, the

Ms to the implementation of USTF in both stages, thus taking advantage of both strategies (SMASH and USTF) to achieve higher resolution in wideband applications with lower values of OSR. In this example, the ![]() -transform of the modulator output is given by:

-transform of the modulator output is given by:

5.8 ![]()

Figure 5.19 SMASH ![]() M with USTF proposed in [288].

M with USTF proposed in [288].

Note that contrary to conventional SMASH ![]() Ms, the quantization error in the front-end stage is ideally canceled, while avoiding any digital filtering. In addition, the use of a scaling factor

Ms, the quantization error in the front-end stage is ideally canceled, while avoiding any digital filtering. In addition, the use of a scaling factor ![]() (which is usually implemented as a power of 2) will further reduce the in-band noise power of the second-stage quantization error at the output. Moreover, using USTF in both stages of the modulator allows relaxing of the output swing and gain demands in the amplifiers, while keeping a better sensitivity to mismatch than simple SMASH and cascade topologies. However, the price to pay is that a front-end DAC with a full scale larger than that of the quantizers in the cascade (with resolutions

(which is usually implemented as a power of 2) will further reduce the in-band noise power of the second-stage quantization error at the output. Moreover, using USTF in both stages of the modulator allows relaxing of the output swing and gain demands in the amplifiers, while keeping a better sensitivity to mismatch than simple SMASH and cascade topologies. However, the price to pay is that a front-end DAC with a full scale larger than that of the quantizers in the cascade (with resolutions ![]() and

and ![]() ) is required to account for the summation of the digital outputs of the stages. Nevertheless, the location of the digital adder helps increase considerably the robustness to capacitor mismatches as demonstrated in [288].

) is required to account for the summation of the digital outputs of the stages. Nevertheless, the location of the digital adder helps increase considerably the robustness to capacitor mismatches as demonstrated in [288].

5.3.2 Hybrid  Ms

Ms

An interesting approach in the design of high-performance ![]() Ms consists of using hybrid circuit and/or architecture techniques to improve the efficiency of the digitization as compared to conventional

Ms consists of using hybrid circuit and/or architecture techniques to improve the efficiency of the digitization as compared to conventional ![]() Ms. The term hybrid is used here to denote those kinds of

Ms. The term hybrid is used here to denote those kinds of ![]() Ms that are not, strictly speaking, pure

Ms that are not, strictly speaking, pure ![]() Ms, according to the classification criteria given in Chapter 1. Thus, several categories of hybrid

Ms, according to the classification criteria given in Chapter 1. Thus, several categories of hybrid ![]() Ms (H-

Ms (H-![]() Ms)—some of them listed in Table 5.11—have reported state-of-the-art performance.

Ms)—some of them listed in Table 5.11—have reported state-of-the-art performance.

Hybrid  M-Nyquist ADCs

M-Nyquist ADCs

A first category of H-![]() M architectures is that which results from combining a Nyquist-rate ADC—usually a pipeline, SAR, or cyclic ADC—and a

M architectures is that which results from combining a Nyquist-rate ADC—usually a pipeline, SAR, or cyclic ADC—and a ![]() M [216, 228, 272, 273, 280, 286]. In the majority of cases, the basic strategy followed in this kind of H-

M [216, 228, 272, 273, 280, 286]. In the majority of cases, the basic strategy followed in this kind of H-![]() Ms consists of replacing the embedded multibit flash ADC with another kind of Nyquist-rate ADC architecture, namely pipeline [280, 286], two-step [273], SAR [216], or cyclic [228, 272]. Essentially, the main advantage of this strategy is to provide a way of increasing the number of levels of the internal quantizer without the prohibitive exponential growth of the power consumption and silicon area of flash ADCs.

Ms consists of replacing the embedded multibit flash ADC with another kind of Nyquist-rate ADC architecture, namely pipeline [280, 286], two-step [273], SAR [216], or cyclic [228, 272]. Essentially, the main advantage of this strategy is to provide a way of increasing the number of levels of the internal quantizer without the prohibitive exponential growth of the power consumption and silicon area of flash ADCs.

The idea of hybrid ![]() M-Nyquist ADCs has been implemented in both single-loop and cascade architectures, featuring a competitive performance in different application scenarios. As an illustration, Figure 5.20 shows the conceptual block diagram of one of the first reported hybrid

M-Nyquist ADCs has been implemented in both single-loop and cascade architectures, featuring a competitive performance in different application scenarios. As an illustration, Figure 5.20 shows the conceptual block diagram of one of the first reported hybrid ![]() M-Nyquist ICs, which consists of in a cascade of a 5-bit second-order

M-Nyquist ICs, which consists of in a cascade of a 5-bit second-order ![]() M and a 12-bit fourth-stage pipeline ADC [286].

M and a 12-bit fourth-stage pipeline ADC [286].

Figure 5.20 Example of the first reported hybrid ![]() M-Pipeline ADCs [286].

M-Pipeline ADCs [286].

One of the main inconveniences of combining ![]() Ms and Nyquist-rate ADCs is that as the number of bits of the Nyquist-rate subADC increases; the circuit complexity, sensitivity to circuit errors, and latency increases as well, with the risk of losing the benefits provided by

Ms and Nyquist-rate ADCs is that as the number of bits of the Nyquist-rate subADC increases; the circuit complexity, sensitivity to circuit errors, and latency increases as well, with the risk of losing the benefits provided by ![]() Ms in terms of system simplicity and robustness against circuit nonidealities. Therefore, although very competitive performance can be achieved by replacing multibit flash ADCs with other alternative Nyquist-rate ADCs, the mentioned design trade-offs have motivated

Ms in terms of system simplicity and robustness against circuit nonidealities. Therefore, although very competitive performance can be achieved by replacing multibit flash ADCs with other alternative Nyquist-rate ADCs, the mentioned design trade-offs have motivated ![]() M designers to explore alternative implementations to conventional multibit quantization, as discussed in Section 5.3.4.

M designers to explore alternative implementations to conventional multibit quantization, as discussed in Section 5.3.4.

Hybrid Active/Passive  Ms

Ms

Another kind of H-![]() Ms corresponds to a family of CT-

Ms corresponds to a family of CT-![]() Ms in which the loop filter is implemented by hybrid active–passive circuit elements. Thus, part of the loop-filter integrators (resonators in the case of BP-

Ms in which the loop filter is implemented by hybrid active–passive circuit elements. Thus, part of the loop-filter integrators (resonators in the case of BP-![]() Ms) are implemented as passive-RC networks, while others are implemented as active-RC or Gm-C circuits. The motivation for using this approach is to reduce the number of OTAs and hence reduce the power dissipation, as OTAs are the circuit blocks that consume most of the power in a

Ms) are implemented as passive-RC networks, while others are implemented as active-RC or Gm-C circuits. The motivation for using this approach is to reduce the number of OTAs and hence reduce the power dissipation, as OTAs are the circuit blocks that consume most of the power in a ![]() M. As already discussed in this book, the design issues associated with loop-filter OTAs aggravate in nanometer CMOS technologies with reduced supply voltage, and particularly in wideband applications where the dynamic requirements of the operational amplifiers yield in many cases to very power-hungry circuit solutions.

M. As already discussed in this book, the design issues associated with loop-filter OTAs aggravate in nanometer CMOS technologies with reduced supply voltage, and particularly in wideband applications where the dynamic requirements of the operational amplifiers yield in many cases to very power-hungry circuit solutions.

In this scenario, replacing some active integrators with passive-RC networks in the ![]() M loop-filter results in a more efficient solution. Apart from the power saving, integrated passive-RC networks have better linearity than their active counterparts. However, the main limitation of using passive integrators is that they do not provide any gain that makes the loop filter more sensitive to their error mechanisms. This limitation can be partially palliated if the active integrators are used at the front-end of the modulator, so that the effect of thermal noise of the passive-RC networks and other circuit nonideal effects can be reduced by the preceding active integrators. Figure 5.21 shows an example proposed by Song et al. in [275]. The modulator architecture—consisting of a fifth-order single-loop architecture—uses five integrators, two of them implemented by passive-RC networks. These passive integrators are placed in the second and fourth positions of the modulator chain, so that their nonideal effects can be attenuated by the gain of active integrators.

M loop-filter results in a more efficient solution. Apart from the power saving, integrated passive-RC networks have better linearity than their active counterparts. However, the main limitation of using passive integrators is that they do not provide any gain that makes the loop filter more sensitive to their error mechanisms. This limitation can be partially palliated if the active integrators are used at the front-end of the modulator, so that the effect of thermal noise of the passive-RC networks and other circuit nonideal effects can be reduced by the preceding active integrators. Figure 5.21 shows an example proposed by Song et al. in [275]. The modulator architecture—consisting of a fifth-order single-loop architecture—uses five integrators, two of them implemented by passive-RC networks. These passive integrators are placed in the second and fourth positions of the modulator chain, so that their nonideal effects can be attenuated by the gain of active integrators.

Figure 5.21 Example of the hybrid active–passive ![]() M reported in [275].

M reported in [275].

Prompted by the above mentioned potential benefits, passive-RC networks are becoming a popular circuit solution for the implementation of low-power wideband CT-![]() Ms. A good example is the fourth-order BP-

Ms. A good example is the fourth-order BP-![]() M reported by Chae et al. [236], which digitizes 24-MHz band-pass signals located at 200 MHz with 58-dB SNDR while consuming 12 mW. This circuit is implemented by using single-opamp high-Q resonators that incorporate positive feedback to achieve high Q and are implemented by combining an active LPF and a passive HPF. Another interesting example was proposed by Srinivasan et al. [161], who reported a third-order CT-

M reported by Chae et al. [236], which digitizes 24-MHz band-pass signals located at 200 MHz with 58-dB SNDR while consuming 12 mW. This circuit is implemented by using single-opamp high-Q resonators that incorporate positive feedback to achieve high Q and are implemented by combining an active LPF and a passive HPF. Another interesting example was proposed by Srinivasan et al. [161], who reported a third-order CT-![]() M made up of a front-end passive-RC integrator followed by two Gm-C integrators. The chip—fabricated in a 45-nm CMOS technology—digitizes 60-MHz signals with 61-dB SNDR and 20 mW power consumption, while clocked at 6 GHz—one of the highest clock frequencies reported by

M made up of a front-end passive-RC integrator followed by two Gm-C integrators. The chip—fabricated in a 45-nm CMOS technology—digitizes 60-MHz signals with 61-dB SNDR and 20 mW power consumption, while clocked at 6 GHz—one of the highest clock frequencies reported by ![]() M ICs to date. This trend is expected to continue, with the demand for higher and higher data rates and the technology downscaling, which will facilitate the integration of high-quality passive devices together with conventional active circuits.

M ICs to date. This trend is expected to continue, with the demand for higher and higher data rates and the technology downscaling, which will facilitate the integration of high-quality passive devices together with conventional active circuits.

Hybrid CT/DT  Ms

Ms

The third category of H-![]() Ms included in Table 5.11 corresponds to those

Ms included in Table 5.11 corresponds to those ![]() Ms in which the loop filter is implemented by both SC and CT integrators, thus taking advantage of both circuit techniques. As shown earlier in this chapter, CT-

Ms in which the loop filter is implemented by both SC and CT integrators, thus taking advantage of both circuit techniques. As shown earlier in this chapter, CT-![]() Ms operate at faster rates than their SC counterparts with relatively lower power dissipation. However, CT-

Ms operate at faster rates than their SC counterparts with relatively lower power dissipation. However, CT-![]() Ms are more sensitive than SC-

Ms are more sensitive than SC-![]() Ms to some circuit and architecture error mechanisms, such as circuit-element tolerances, excess loop delay, and clock jitter error.

Ms to some circuit and architecture error mechanisms, such as circuit-element tolerances, excess loop delay, and clock jitter error.

Some authors have tried to circumvent the mentioned limitations of CT-![]() Ms by using the so-called hybrid CT/DT

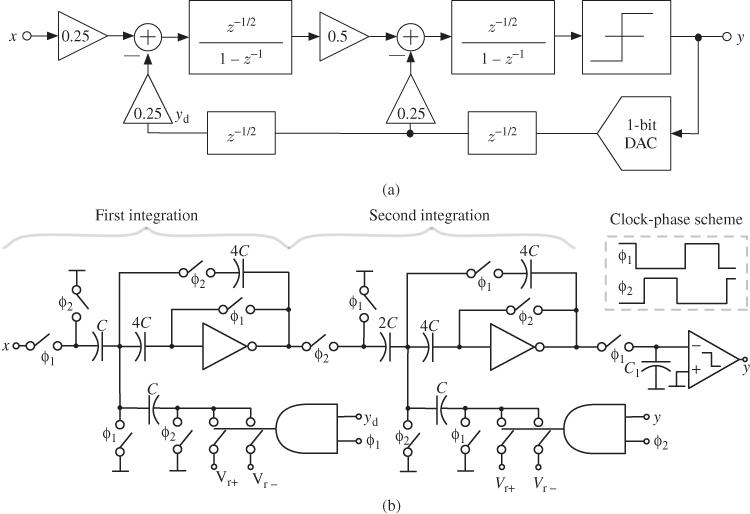

Ms by using the so-called hybrid CT/DT ![]() Ms, in which some parts of the loop filter—usually the front-end building blocks—are implemented using CT circuits, thus providing potentially faster operation and embedded antialiasing filtering with reduced power consumption [279, 281–283, 294, 309, 310]. Thus, hybrid CT/DT

Ms, in which some parts of the loop filter—usually the front-end building blocks—are implemented using CT circuits, thus providing potentially faster operation and embedded antialiasing filtering with reduced power consumption [279, 281–283, 294, 309, 310]. Thus, hybrid CT/DT ![]() Ms have been demonstrated using both single-loop [281, 283] and cascade ICs [279]. The most common situation in practice consists of using a CT front-end integrator, whereas the remaining integrators in the modulator loop are implemented using SC circuit techniques. As an illustration, Figure 5.22 shows one of the first practical implementations of a hybrid CT/DT cascade

Ms have been demonstrated using both single-loop [281, 283] and cascade ICs [279]. The most common situation in practice consists of using a CT front-end integrator, whereas the remaining integrators in the modulator loop are implemented using SC circuit techniques. As an illustration, Figure 5.22 shows one of the first practical implementations of a hybrid CT/DT cascade ![]() M, proposed in [279]. This modulator is a cascade of a second-order (active-RC) CT-

M, proposed in [279]. This modulator is a cascade of a second-order (active-RC) CT-![]() M stage with a first-order SC stage, considering 4-bit quantization in both stages.

M stage with a first-order SC stage, considering 4-bit quantization in both stages.

Figure 5.22 Example of the hybrid CT/DT cascade ![]() Ms reported in [279].

Ms reported in [279].

In spite of the mentioned advantages, reported hybrid CT/DT ![]() M ICs do not really exploit the potential capability of CT circuits integrated in CMOS processes to operate up to the gigahertz range with reasonable linearity. This is partially due to the fact that the maximum sampling rate of hybrid CT/DT

M ICs do not really exploit the potential capability of CT circuits integrated in CMOS processes to operate up to the gigahertz range with reasonable linearity. This is partially due to the fact that the maximum sampling rate of hybrid CT/DT ![]() Ms is indeed limited by the SC part of the modulator loop filter. A possible solution to alleviate this restriction could be using the so-called multirating, as described in the next section.

Ms is indeed limited by the SC part of the modulator loop filter. A possible solution to alleviate this restriction could be using the so-called multirating, as described in the next section.

5.3.3 Multirate  Ms

Ms

The so-called multirate (MR) ![]() Ms are a particular kind of

Ms are a particular kind of ![]() Ms in which a different sampling frequency is used at different parts of the modulator. The most common approach is based on using a lower sampling frequency in the building blocks placed at the front-end of the modulator—where most of the power is consumed—and a higher sampling rate in the subsequent subcircuits, where the dynamic requirements can be relaxed [311]. This concept can be applied to either single-loop or cascade architectures and implemented using SC [311] and CT circuits [312]. Without loss of generality, this section focuses on cascade implementations because the modular nature of these topologies makes the implementation of MR-

Ms in which a different sampling frequency is used at different parts of the modulator. The most common approach is based on using a lower sampling frequency in the building blocks placed at the front-end of the modulator—where most of the power is consumed—and a higher sampling rate in the subsequent subcircuits, where the dynamic requirements can be relaxed [311]. This concept can be applied to either single-loop or cascade architectures and implemented using SC [311] and CT circuits [312]. Without loss of generality, this section focuses on cascade implementations because the modular nature of these topologies makes the implementation of MR-![]() Ms more simple and robust. However, similar considerations can be derived for single-loop MR-

Ms more simple and robust. However, similar considerations can be derived for single-loop MR-![]() M topologies.

M topologies.

Upsampling Cascade MR- Ms

Ms

Figure 5.23a shows the conceptual implementation of a conventional cascade (two-stage) MR-![]() M.4 For the sake of generality, multibit quantization will be assumed in all stages of the cascade, with

M.4 For the sake of generality, multibit quantization will be assumed in all stages of the cascade, with ![]() being the number of bits of the internal quantizer in the

being the number of bits of the internal quantizer in the ![]() th stage. The sampling frequency

th stage. The sampling frequency ![]() of the different modulator blocks is depicted in the figure. The most common situation in conventional MR-

of the different modulator blocks is depicted in the figure. The most common situation in conventional MR-![]() Ms is that the front-end stage operates at

Ms is that the front-end stage operates at ![]() , whereas the remaining

, whereas the remaining ![]() th stages are sampled at

th stages are sampled at ![]() . This approach—also referred to as upsampling MR-

. This approach—also referred to as upsampling MR-![]() M [313]—benefits from increasing values of OSR in the back-end stages—where the dynamic requirements are less demanding than in the front-end stages [311, 312, 314].

M [313]—benefits from increasing values of OSR in the back-end stages—where the dynamic requirements are less demanding than in the front-end stages [311, 312, 314].

Figure 5.23 Conceptual block diagram of a conventional (upsampling) cascade MR-![]() M: (a) DT scheme and (b) hybrid CT/DT scheme.

M: (a) DT scheme and (b) hybrid CT/DT scheme.

The operation behind the modulator in Figure 5.23a is conceptually the same as in a conventional monorate cascade ![]() M. All stage outputs are combined by the DCL transfer functions—clocked at

M. All stage outputs are combined by the DCL transfer functions—clocked at ![]() —so that ideally only the quantization error of the last stage remains and it is shaped by an NTF whose order (

—so that ideally only the quantization error of the last stage remains and it is shaped by an NTF whose order (![]() ) is the sum of the orders of all stages in the cascade (