CHAPTER 2 Other Linear Circuits

![]() Section 2-1: Buffer Amplifiers

Section 2-1: Buffer Amplifiers

![]() Section 2-3: Instrumentation Amplifiers

Section 2-3: Instrumentation Amplifiers

![]() Section 2-4: Differential Amplifiers

Section 2-4: Differential Amplifiers

![]() Section 2-5: Isolation Amplifiers

Section 2-5: Isolation Amplifiers

![]() Section 2-6: Digital Isolation Techniques

Section 2-6: Digital Isolation Techniques

![]() Section 2-7: Active Feedback Amplifiers

Section 2-7: Active Feedback Amplifiers

![]() Section 2-8: Logarithmic Amplifiers

Section 2-8: Logarithmic Amplifiers

![]() Section 2-9: High Speed Clamping Amplifiers

Section 2-9: High Speed Clamping Amplifiers

![]() Section 2-11: Analog Multipliers

Section 2-11: Analog Multipliers

![]() Section 2-12: RMS to DC Converters

Section 2-12: RMS to DC Converters

![]() Section 2-13: Programmable Gain Amplifiers

Section 2-13: Programmable Gain Amplifiers

SECTION 2-1 Buffer Amplifiers

In the early days of high speed circuits, simple emitter followers were often used as high speed buffers. The term buffer was generally accepted to mean a unity-gain, open-loop amplifier. With the availability of matching PNP transistors, a simple emitter follower can be improved, as shown in Figure 2-1(A). This complementary circuit offers first-order cancellation of DC offset voltage, and can achieve bandwidths greater than 100 MHz. Typical offset voltages without trimming are usually less than 50 mV, even with unmatched discrete transistors.

If high input impedance is required, a dual FET can be used as an input stage ahead of a complementary emitter follower, as shown in Figure 2-1(B). This form of the buffer circuit was implemented by both National Semiconductor Corporation as the LH0033, and by Analog Devices as the ADLH0033.

Circuits such as these achieved bandwidths of about 100 MHz at fairly respectable levels of harmonic distortion, typically better than −60 dBc. However, they suffered from DC and AC nonlinearities when driving loads less than 500 Ω.

One of the first totally monolithic implementations of these functions was the Precision Monolithics, Inc. BUF03 shown in Figure 2-2 (see Reference 1). PMI is now a division of Analog Devices. This open-loop IC buffer achieved a bandwidth of about 50 MHz for a 2 V peak-to-peak signal.

The BUF03 circuit is interesting because it demonstrates techniques that eliminated the requirement for the slow, bandwidth-limited vertical PNP transistors associated with most IC processes available at the time of the design (approximately 1979).

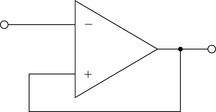

One of the problems with all the open-loop buffers discussed thus far is that although high bandwidths can be achieved, the devices discussed do not take advantage of negative feedback. Distortion and DC performance suffer considerably when open-loop buffers are loaded with typical video impedance levels of 50, 75, or 100 Ω. The solution is to use a properly compensated wide bandwidth op amp in a unity-gain follower configuration. In the early days of monolithic op amps, process limitations prevented this, so the open-loop approach provided a popular interim solution (Figure 2-3).

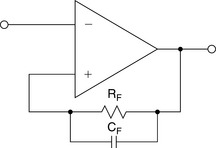

Practically all unity-gain stable voltage or current feedback op amps can be used in a simple follower configuration. Usually, however, the general-purpose op amps are compensated to operate over a wide range of gains and feedback conditions. Therefore, bandwidth suffers somewhat at low gains, especially in the unity-gain non-inverting mode, and additional external compensation is usually required, as shown in Figure 2-4.

A practical solution is to compensate the op amp for the desired closed-loop gain, while including the gain-setting resistors on-chip. Note that this form of op amp, internally configured as a buffer, may typically have no feedback pin. Also, putting the resistors and compensation on-chip serves to reduce parasitics.

There are a number of op amps optimized in this manner. Roy Gosser’s AD9620 (see Reference 2) was probably the earliest monolithic implementation. The AD9620 was a 1990 product release, and achieved a bandwidth of 600 MHz using ±5 V supplies. It was optimized for unity gain, and used the voltage feedback architecture. A newer design based on similar techniques is the AD9630, which achieves a 750 MHz bandwidth.

The BUF04 unity-gain buffer (see Reference 3) was released in 1994 and achieves a bandwidth of 120 MHz. This device was optimized for large signals and operates on supplies from ±5 V to ± 15 V. Because of the wide supply range, the BUF04 is useful not only as a standalone unit-gain buffer, but also within a feedback loop with a standard op amp, to boost output.

Although the common definition of a buffer is unity-gain device, sometimes the term is used for a circuit with a gain of two. Closed-loop buffers with a gain of two find wide applications as transmission line drivers, as shown in Figure 2-5. The internally configured fixed gain of the amplifier compensates for the loss incurred by the source and load termination. Impedances of 50, 75, and 100 Ω are popular cable impedances. The AD8074/AD8075 500 MHz triple buffers are optimized for gains of 1 and 2, respectively. The dual AD8079A/AD8079B 260 MHz buffer is optimized for gains of 2 and 2.2, respectively.

In implementing a high speed unity-gain buffer with a voltage feedback op amp, there will typically be no resistor required in the feedback loop, which considerably simplifies the circuit. Note that this is not a 100% hard-and-fast rule however, so always check the device data sheet to be sure. A unity-gain buffer with a current feedback op amp will always require a feedback resistor, typically in the range of 500–1,000 Ω. So, be sure to use a value appropriate to not only the basic part, but also the specific power supplies in use.

SECTION 2-2 Gain Blocks

While the op amp allows gain to be set with external resistors, there are a group of circuits that are designed to operate at a fixed gain. These parts are typically RF components. They are also typically designed to be operated in a 50 Ω environment, with the inputs and outputs matched internally. Often the gain blocks are available in several gain settings.

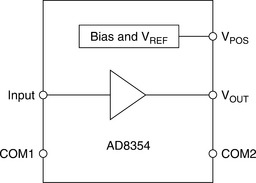

For example, the AD8354 RF gain block is a fixed-gain amplifier with single-ended input and output ports whose impedances are nominally equal to 50 Ω over the frequency range 100 MHz to 2.7 GHz. Consequently, it can be directly inserted into a 50 Ω system with no impedance matching circuitry required. The input and output impedances are sufficiently stable versus variations in temperature and supply voltage that no impedance matching compensation is required (Figure 2-6).

Differential input and output gain blocks are also available. An example of a differential input, single-ended output device is the AD8129 (see Figure 2-7).

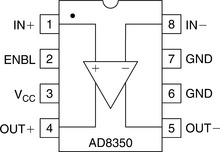

Fully differential input and output devices are also available, such as the AD8350 (see Figure 2-8).

SECTION 2-3 Instrumentation Amplifiers

The instrumentation amp is primarily used to amplify small differential voltages in the presence of (typically) larger common-mode (CM) voltages.

In Amp Definitions

An in amp is a precision closed-loop gain block. It has a pair of differential input terminals, and a single-ended output that works with respect to a reference or common terminal, as shown in Figure 2-9. The input impedances are balanced and high in value, typically ≥ 109 Ω. Again, unlike an op amp, an in amp uses an internal feedback resistor network, plus one (usually) gain set resistance, RG. Also unlike an op amp is the fact that the internal resistance network and RG are isolated from the signal input terminals. In amp gain can also be preset via an internal RG by pin selection (again isolated from the signal inputs). Typical in amp gains range from 1 to 1,000.

The in amp develops an output voltage which is referenced to a pin usually designated REFERENCE or VREF. In many applications, this pin is connected to circuit ground, but it can be connected to other voltages, as long as they lie within the rated compliance range of the in amp. This feature is especially useful in single-supply applications, where the output voltage is usually referenced to mid-supply (i.e., +2.5 V in the case of a + 5 V supply).

In order to be effective, an in amp needs to be able to amplify microvolt-level signals, while simultaneously rejecting volts of CM signal at its inputs. This requires that in amps have very high common-mode rejection (CMR). Typical values of in amp CMR are from 70 to over 100 dB (at DC), with CMR usually improving at higher gains.

It is important to note that a CMR specification for DC inputs alone is not sufficient in most practical applications. In industrial applications, the most common cause of external interference is 50/60 Hz AC power-related noise (including harmonics). In differential measurements, this type of interference tends to be induced equally onto both in amp inputs, so the interference appears as a CM input signal. Therefore, specifying CMR over frequency is just as important as specifying its DC value. Note that imbalance in the two source impedances will degrade the CMR of some in amps. Analog Devices fully specifies in amp CMR at 50/60 Hz, with a source impedance imbalance of 1 kΩ.

Op Amp/In Amp Functionality Differences

An op amp is a general-purpose gain block—user-configurable in myriad ways using external feedback components of R, C, and (sometimes) L. The final configuration and circuit function using an op amp is truly whatever you make of it.

In contrast to this, an instrumentation amp (in amp) is a more constrained device in terms of functioning, and also the allowable range(s) of operating gain. People also often confuse in amps as to their function, calling them “op amps.” But the converse is seldom (if ever) true. It should be understood that an in amp is not just a special type op amp; the function of the two devices is actually fundamentally different.

Perhaps a good way to differentiate the two devices is to remember that an op amp can be programmed to do almost anything, by virtue of its feedback flexibility. In contrast to this, an in amp cannot be programmed to do just anything. It can only be programmed for gain, and then over a specific range. An op amp is configured via a number of external components, while an in amp is configured by either one resistor, or by pin-selectable taps for its working gain.

Subtractor or Difference Amplifiers

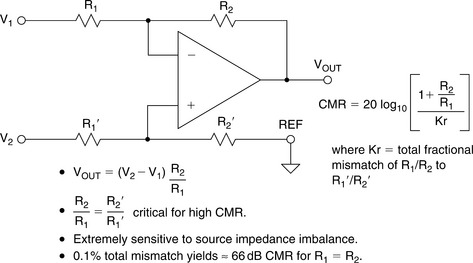

A simple subtractor or difference amplifier can be constructed with four resistors and an op amp as shown in Figure 2-10. It should be noted that this is not a true in amp, but it is often used in applications where a simple differential to single-ended conversion is required. Because of its popularity, this circuit will be examined in more detail in order to understand its fundamental limitations before discussing true in amp architectures.

There are several fundamental problems with this simple circuit. First, the input impedance seen by V1 and V2 is not balanced. The input impedance seen by V1 is R1, but the input impedance seen by V2 is R1′+R2′. The configuration can also be quite problematic in terms of CMR, since even a small source impedance imbalance will degrade the workable CMR. This problem can be solved with well-matched open-loop buffers in series with each input (e.g., using a precision dual op amp). But this adds complexity to a simple circuit, and may introduce offset drift and nonlinearity.

The second problem with this circuit is that the CMR is primarily determined by the resistor ratio matching, not the op amp. The resistor ratios R1/R2 and R1′/R2′ must match extremely well to reject CM noise—at least as well as a typical op amp CMR of 100 dB. Note also that the absolute resistor values are relatively unimportant.

Picking four 1% resistors from a single batch may yield a net ratio matching of 0.1%, which will achieve a CMR of 66 dB (assuming R1 = R2). But if one resistor differs from the rest by 1%, the CMR will drop to only 46 dB. Clearly, very limited performance is possible using ordinary discrete resistors in this circuit (without resorting to hand matching). This is because the best standard off-the-shelf RNC/RNR style resistor tolerances are on the order of 0.1% (see Reference 1).

In general, the worst-case CMR for a circuit of this type is given by the following equation (see References 2 and 3):

where Kr is the individual resistor tolerance in fractional form, for the case where four discrete resistors are used. This equation shows that the worst-case CMR for a tolerance build-up for four unselected same-nominal-value 1% resistors is no better than 34 dB.

A single resistor network with a net matching tolerance of Kr would probably be used for this circuit, in which case the expression would be as noted in the Figure, or:

A net matching tolerance of 0.1% in the resistor ratios therefore yields a worst-case DC CMR of 66 dB using Eq. (2-2), and assuming R1 = R2. Note that either case assumes a significantly higher amplifier CMR (i.e., >100 dB). Clearly for high CMR, such circuits need four single-substrate resistors, with very high absolute and TC matching. Such networks using thick-/thin-film technology are available from companies such as Caddock and Vishay, in ratio matches of 0.01% or better.

In implementing the simple difference amplifier, rather than incurring the higher costs and PCB real estate limitations of a precision op amp plus a separate resistor network, it is usually better to seek out a completely monolithic solution.

An interesting variation on the simple difference amplifier is found in the AD629 difference amplifier, optimized for high CM input voltages. A typical current-sensing application is shown in Figure 2-11. The AD629 is a differential to single-ended amplifier with a gain of unity. It can handle a CM voltage of ±270 V with supply voltages of ± 15 V, with a small signal bandwidth of 500 kHz.

The high CM voltage range is obtained by attenuating the non-inverting input (pin 3) by a factor of 20 times, using the R1−R2 divider network. On the inverting input, resistor R5 is chosen such that R5?R3 equals resistor R2. The noise gain of the circuit is equal to 20 [1 + R4/(R3‖R5)], thereby providing unity gain for differential input voltages. Laser wafer trimming of the R1−R5 thin-film resistors yields a minimum CMR of 86 dB @ 500 Hz for the AD629B. Within an application, it is good practice to maintain balanced source impedances on both inputs, so dummy resistor RCOMP is chosen to equal to the value of the shunt-sensing resistor RSHUNT.

The Three Op Amp Instrumentation Amplifier Topology

For the highest precision and performance, the three op amp instrumentation amplifier topology is optimum for bridge and other offset transducer applications where high accuracy and low nonlinearity are required (Figure 2-12).

Resistor RG sets the overall gain of this amplifier. It may be internal, external, or (software or pin-strap) programmable, depending on the particular in amp. In this configuration, CMR depends on the ratio matching of R3/R2 to R3′/R2′. Furthermore, CM signals are only amplified by a factor of 1 regardless of gain (no CM voltage will appear across RG, hence, no CM current will flow in it because the input terminals of an op amp will have no significant potential difference between them).

As a result of the high ratio of differential to CM gain in A1–A2, CMR of this in amp theoretically increases in proportion to gain. Large CM signals (within the A1–A2 op amp headroom limits) may be handled at all gains. Finally, because of the symmetry of this configuration, CM errors in the input amplifiers, if they track, tend to be canceled out by the subtractor output stage. These features explain the popularity of this three op amp in amp configuration—it is capable of delivering the highest performance.

The classic three op amp configuration has been used in a number of monolithic IC in amps (see References 8 and 9). Besides offering excellent matching between the three internal op amps, thin-film laser-trimmed resistors provide excellent ratio matching and gain accuracy at much lower cost than using discrete precision op amps and resistor networks. The AD620 (see Reference 10) is an excellent example of monolithic IC in amp technology. A simplified device schematic is shown in Figure 2-13.

The AD620 is a highly popular in amp and is specified for power supply voltages from ±2.3 V to ± 18 V. Input voltage noise is only 9 nV/Hz @ 1 kHz. Maximum input bias current is only 1 nA, due to the use of superbeta transistors for Q1–Q2.

Overvoltage protection is provided, in part, by the internal 400 Ω thin-film current-limit resistors in conjunction with the diodes connected from the emitter-to-base of Q1 and Q2. The gain G is set with a single external RG resistor, as noted by Eq. (2-3):

As can be noted from this expression and Figure 2-13, the AD620 internal resistors are trimmed so that standard 1% or 0.1% resistors can be used to set gain to popular values. Single-supply operation of the three op amp in amp requires an understanding of the internal node voltages. Figure 2-14 shows a generalized diagram of the in amp operating on a single + 5 V supply. The maximum and minimum allowable output voltages of the individual op amps are designated VOH (maximum high output) and VOL (minimum low output), respectively.

Note that the gain from the CM voltage to the outputs of A1 and A2 is unity. It can be stated that the sum of the CM voltage and the signal voltage at these outputs must fall within the amplifier output voltage range. Obviously this configuration cannot handle input CM voltages of either 0 V or +5 V, because of saturation of A1 and A2. The output reference is positioned halfway between VOH and VOL to allow for bipolar differential input signals.

While there are a number of good single supply in amps, such as the AD627, the highest performance devices are still among those specified for traditional dual-supply operation, i.e., the just-discussed AD620. For certain applications, even devices such as the AD620, which has been designed for dual-supply operation, can be used with full precision on a single-supply power system.

Precision Single-Supply Composite In Amp

One way to achieve both high precision and single-supply operation takes advantage of the fact that many popular sensors (e.g., strain gauges) provide an output signal which is inherently centered around an approximate midpoint of the supply voltage (and/or the reference voltage). Taking advantage of this basic point allows the inputs of a signal conditioning in amp to be biased at “mid-supply.” As a consequence of this step, the inputs need not operate near ground or the positive supply voltage, and the in amp can still be used with all its precision.

Under these conditions, an AD620 dual-supply in amp referenced to the supply midpoint followed by a rail-to-rail op amp output-gain stage provides very high DC precision. Figure 2-15 illustrates one such high performance in amp, which operates on a single + 5 V supply.

This circuit uses the AD620 as a low cost precision in amp for the input stage, along with an AD822 JFET input dual rail-to-rail output op amp for the output stage, comprising A1 and A2. The output stage operates at a fixed gain of 3, with overall gain set by RG.

In this circuit, R3 and R4 form a voltage divider which splits the supply voltage nominally in half to +2.5 V, with fine adjustment provided by a trimming potentiometer, P1. This voltage is applied to the input of A1, an AD822 voltage follower, which buffers it and provides a low impedance source needed to drive the AD620’s reference pin as well as providing the output reference voltage VREF. Note that this feature allows a bipolar VOUT to be measured with respect to this +2.5 V reference (not to GND). This is despite the fact that the entire circuit operates from a single (unipolar) supply.

The other half of the AD822 is connected as a gain of 3 inverter, so that it can output ±2.5 V, “rail-to-rail,” with only ±0.83 V required of the AD620. This output voltage level of the AD620 is well within the AD620’s capability, thus ensuring high linearity for the front end.

The general-gain expression for this composite in amp is the product of the gain of the AD620 stage, and the gain of inverting amplifier:

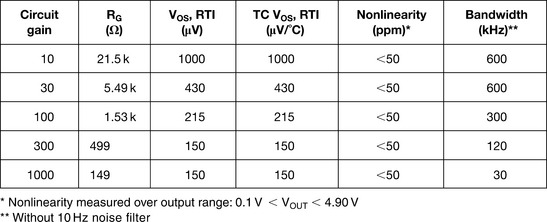

For this example, an overall gain of 10 is realized with RG = 21.5 kΩ (closest standard value). The table shown in Figure 2-16 summarizes various RG gain values, and the resulting performance for gains ranging from 10 to 1,000.

In this application, the allowable input voltage on either input to the AD620 must lie between + 2 V and + 3.5 V in order to maintain linearity. For example, at an overall circuit gain of 10, the CM input voltage range spans from 2.25 V to 3.25 V, allowing room for the ±0.25 V full-scale differential input voltage required to drive the output ±2.5 V about VREF.

The inverting configuration was chosen for the output buffer to facilitate system output offset voltage adjustment by summing currents into the A2 stage buffer’s feedback summing node. These offset currents can be provided by an external DAC, or from a resistor connected to a reference voltage.

To reduce the effects of unwanted noise pickup, a filter capacitor is recommended across A2’s feedback resistance to limit the circuit bandwidth to the frequencies of interest. This capacitor forms a first-order lowpass filter with R2. The corner frequency is 10 Hz as shown, but this may be easily modified. The capacitor should be a high quality film type, such as polypropylene.

The Two Op Amp Instrumentation Amplifier Topology

The circuit shown in Figure 2-17 is referred to as the two op amp in amp. It is particularly applicable in single-supply systems. Dual IC op amps are used in most cases for good matching, such as the OP297 or the OP284. Most often a rail-to-rail op amp is indicated. The resistors are often a thin-film laser-trimmed array, possibly on the same chip. The in amp gain can be easily set with an external resistor, RG. Without RG, the gain is simply 1 + R2/R1. In a practical application, the R2/R1 ratio is chosen for the desired minimum in amp gain.

The input impedance of the two op amp in amp is inherently high, permitting the impedance of the signal sources to be high and unbalanced. The DC CM rejection is limited by the matching of R1/R2 to R1′/R2′. If there is a mismatch in any of the four resistors, the DC CM rejection is limited to:

Notice that the net CMR of the circuit increases proportionally with the working gain of the in amp, an effective aid to high performance at higher gains.

IC in amps are particularly well suited to meeting the combined needs of ratio matching and temperature tracking of the gain-setting resistors. While thin-film resistors fabricated on silicon have an initial tolerance of up to ± 20%, laser trimming during production allows the ratio error (not absolute value) between the resistors to be reduced to 0.01% (100 ppm). Furthermore, the tracking between the temperature coefficients of the thin-film resistors is inherently low and is typically less than 3 ppm/°C (0.0003%/°C).

When dual supplies are used, VREF is normally connected directly to ground. In single-supply applications, VREF is usually connected to a low impedance voltage source equal to one-half the supply voltage. The gain from VREF to node “A” is R1/R2, and the gain from node “A” to the output is R2′/R1′. This makes the gain from VREF to the output equal to unity, assuming perfect ratio matching. Note that it is critical that the source impedance seen by VREF be low; otherwise, CMR will be degraded.

One major disadvantage of the two op amp in amp design is that CM voltage input range must be traded off against gain. The amplifier A1 must amplify the signal at V1 by 1 + R1/R2. If R1 ![]() R2 (a low gain example in Figure 2-18), A1 will saturate if the V1 CM signal is too high, leaving no A1 headroom to amplify the wanted differential signal. For high gains (R1

R2 (a low gain example in Figure 2-18), A1 will saturate if the V1 CM signal is too high, leaving no A1 headroom to amplify the wanted differential signal. For high gains (R1 ![]() R2), there is correspondingly more headroom at node “A,” allowing larger CM input voltages.

R2), there is correspondingly more headroom at node “A,” allowing larger CM input voltages.

The AC CM rejection of this configuration is generally poor because the signal path from V1 to VOUT has the additional phase shift of A1. In addition, the two amplifiers are operating at different closed-loop gains (and thus at different bandwidths). The use of a small trim capacitor “C” as shown in Figure 2-17 can improve the AC CMR somewhat.

A low gain (G = 2) single-supply two op amp in amp configuration results when RG is not used, and is shown in Figure 2-18. The input CM and differential signals must be limited to values which prevent saturation of either A1 or A2. In the example, the op amps remain linear to within 0.1 V of the supply rails, and their upper and lower output limits are designated VOH and VOL, respectively. These saturation voltage limits would be typical for a single-supply, rail–rail output op amp (such as the AD822).

Using the Figure 2-18 equations, the voltage at V1 must fall between 1.3 V and 2.4 V to prevent A1 from saturating. Notice that VREF is connected to the average of VOH and VOL (2.5 V). This allows for bipolar differential input signals with VOUT referenced to +2.5 V.

A high gain (G = 100) single-supply two op amp in amp configuration is shown in Figure 2-19. Using the same equations, note that voltage at V1 can now swing between 0.124 V and 4.876 V. VREF is again 2.5 V, to allow for bipolar input and output signals.

All of these discussions show that the conventional two op amp in amp architecture is fundamentally limited, when operating from a single power supply. These limitations can be viewed in one sense as a restraint on the allowable input CM range for a given gain. Or, alternately, it can be viewed as limitation on the allowable gain range, for a given CM input voltage.

In summary, regardless of gain, the basic structure of the common two op amp in amp does not allow for CM input voltages of zero when operated on a single supply. The only route to removing these restrictions for single-supply operation is to modify the in amp architecture.

In Amp DC Error Sources

The DC and noise specifications for in amps differ slightly from conventional op amps, so some discussion is required in order to fully understand the error sources.

The gain of an in amp is usually set by a single resistor. If the resistor is external to the in amp, its value is either calculated from a formula or chosen from a table on the data sheet, depending on the desired gain.

Absolute value laser wafer trimming allows the user to program gain accurately with this single resistor. The absolute accuracy and temperature coefficient of this resistor directly affects the in amp gain accuracy and drift. Since the external resistor will never exactly match the internal thin-film resistor tempcos, a low TC (<25 ppm/°C) metal film resistor should be chosen, preferably with a 0.1% or better accuracy.

Often specified as having a gain range of 1 to 1,000, or 1 to 10,000, many in amps will work at higher gains, but the manufacturer will not guarantee a specific level of performance at these high gains. In practice, as the gain-setting resistor becomes smaller, any errors due to the resistance of the metal runs and bond wires become significant. These errors, along with an increase in noise and drift, may make higher single-stage gains impractical. In addition, input offset voltages can become quite sizable when reflected to output at high gains. For instance, a 0.5 mV input offset voltage becomes 5 V at the output for a gain of 10,000. For high gains, the best practice is to use an in amp as a preamplifier; then use a post amplifier for further amplification.

In a pin-programmable-gain in amp such as the AD621, the gain-set resistors are internal, well matched, and the device gain accuracy and gain drift specifications include their effects. The AD621 is otherwise generally similar to the externally gain-programmed AD620.

The gain error specification is the maximum deviation from the gain equation. Monolithic in amps such as the AD624C have very low factory trimmed gain errors, with its maximum error of 0.02% at G = 1 and 0.25% at G = 500 being typical for this high quality in amp. Notice that the gain error increases with increasing gain. Although externally connected gain networks allow the user to set the gain exactly, the temperature coefficients of the external resistors and the temperature differences between individual resistors within the network all contribute to the overall gain error. If the data is eventually digitized and presented to a digital processor, it may be possible to correct for gain errors by measuring a known reference voltage and then multiplying by a constant.

Nonlinearity is defined as the maximum deviation from a straight line on the plot of output versus input. The straight line is drawn between the end-points of the actual transfer function. Gain nonlinearity in a high quality in amp is usually 0.01% (100 ppm) or less, and is relatively insensitive to gain over the recommended gain range.

The total input offset voltage of an in amp consists of two components (see Figure 2-20): input offset voltage, VOSI, is the input offset component that is reflected to the output of the in amp by the gain G; output offset voltage, VOSO, is independent of gain.

At low gains, output offset voltage is dominant, while at high gains input offset dominates. The output offset voltage drift is normally specified as drift at G = 1 (where input effects are insignificant), while input offset voltage drift is given by a drift specification at a high gain (where output offset effects are negligible).

The total output offset error, referred to the input (RTI), is equal to VOSI + VOSO/G. In amp data sheets may specify VOSI and VOSO separately, or give the total RTI input offset voltage for different values of gain.

Input bias currents may also produce offset errors in in amp circuits (Figure 2-20, again). If the source resistance, RS, is unbalanced by an amount, ΔRS, (often the case in bridge circuits), then there is an additional input offset voltage error due to the bias current, equal to IBΔRS (assuming that IB+ ≈ IB− = IB). This error is reflected to the output, scaled by the gain G.

The input offset current, IOS, creates an input offset voltage error across the source resistance, RS + ΔRS, equal to IOS(RS + ΔRS), which is also reflected to the output by the gain, G.

In amp CM error is a function of both gain and frequency. Analog Devices specifies in amp CMR for a 1 kΩ source impedance unbalance at a frequency of 60 Hz. The RTI CM error is obtained by dividing the CM voltage, VCM, by the common-mode rejection ratio (CMRR).

Figure 2-21 shows the CMR for the AD620 in amp as a function of frequency, with a 1 kΩ source impedance imbalance.

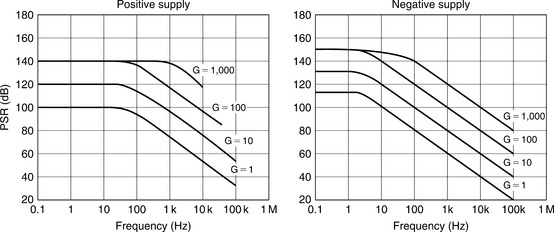

Power supply rejection (PSR) is also a function of gain and frequency. For in amps, it is customary to specify the sensitivity to each power supply separately, as shown in Figure 2-22 for the AD620. The RTI PSR error is obtained by dividing the power supply deviation from nominal by the power supply rejection ratio (PSRR).

Because of the relatively poor PSR at high frequencies, decoupling capacitors are required on both power pins to an in amp. Low inductance ceramic capacitors (0.01–0.1 μF) are appropriate for high frequencies. Low ESR electrolytic capacitors should also be located at several points on the PC board for low frequency decoupling.

Note that these decoupling requirements apply to all linear devices, including op amps and data converters. Further details on power supply decoupling are found in Chapter 7.

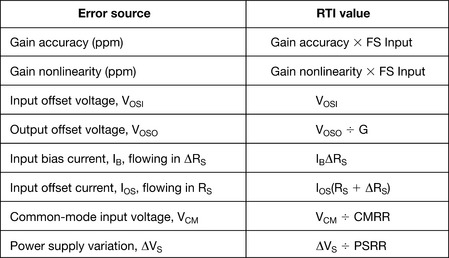

Now that all DC error sources have been accounted for, a worst-case DC error budget can be calculated by reflecting all the sources to the in amp input, as is illustrated by the table of Figure 2-23.

It should be noted that the DC errors can be referred to the in amp output (RTO) by simply multiplying the RTI error by the in amp gain.

In Amp Noise Sources

Since in amps are primarily used to amplify small precision signals, it is important to understand the effects of all the associated noise sources. The in amp noise model is shown in Figure 2-24.

There are two sources of input voltage noise. The first is represented as a noise source, VNI, in series with the input, as in a conventional op amp circuit. This noise is reflected to the output by the in amp gain, G. The second noise source is the output noise, VNO, represented as a noise voltage in series with the in amp output. The output noise, shown here referred to VOUT, can be RTI by dividing by the gain, G.

There are also two noise sources associated with the input noise currents IN+ and IN−. Even though IN+ and IN− are usually equal (IN+ ≈ IN− = IN), they are uncorrelated, and therefore, the noise they each create must be summed in a root-sum-squares (RSS) fashion. IN+ flows through one-half of RS, and IN− the other half. This generates two noise voltages, each having an amplitude INRS/2. Each of these two noise sources is reflected to the output by the in amp gain, G.

The total output noise is calculated by combining all four noise sources in an RSS manner:

The total noise, RTI is simply the above expression divided by the in amp gain, G:

In amp data sheets often present the total voltage noise RTI as a function of gain. This noise spectral density includes both the input (VNI) and output (VNO) noise contributions. The input current noise spectral density is specified separately.

As in the case of op amps, the total in amp noise RTI must be integrated over the applicable in amp closed-loop bandwidth to compute an RMS value. The bandwidth may be determined from data sheet curves that show frequency response as a function of gain.

Regarding this bandwidth, some care must be taken in computing it, as it is often not constant bandwidth product relationship, as is true with VFB op amps. In the case of the AD620 in amp family, e.g., the gain-bandwidth pattern is more like that of a CFB op amp. In such cases, the safest way to predict the bandwidth at a given gain is to use the curves supplied within the data sheet.

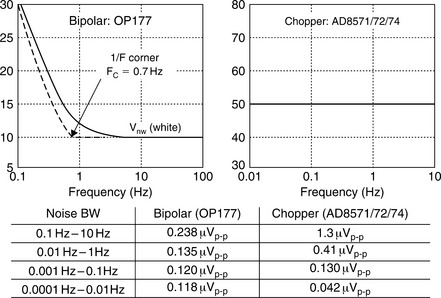

In Amp Bridge Amplifier Error Budget Analysis

It is important to understand in amp error sources in a typical application. Figure 2-25 shows a 350 Ω load cell with a full-scale output of 100 mV when excited with a 10 V source. The AD620 is configured for a gain of 100 using the external 499 Ω gain-setting resistor. The table shows how each error source contributes to a total unadjusted error of 2,145 ppm. Note however that the gain, offset, and CMR errors can all be removed with a system calibration. The remaining errors—gain nonlinearity and 0.1–10 Hz noise—cannot be removed with calibration and ultimately limit the system resolution to 42.8 ppm (approximately 14-bit accuracy).

This example is of course just an illustration, but should be useful toward the importance of addressing performance-limiting errors such as gain nonlinearity and low frequency noise.

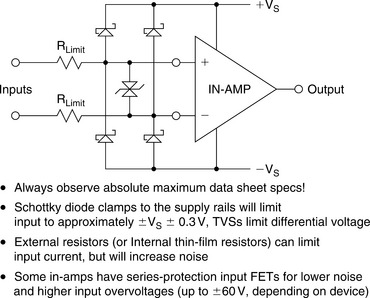

In Amp Input Overvoltage Protection

In their typical application as interface amplifiers for data acquisition systems, in amps are often subjected to input overloads, i.e., voltage levels in excess of the full-scale for the selected gain range. The manufacturer’s “absolute maximum” input ratings for the device should be closely observed. As with op amps, many in amps have absolute maximum input voltage specifications equal to ± VS.

In some cases, external series resistors (for current limiting) and diode clamps may be used to prevent overload, if necessary (see Figure 2-26). Some in amps have built-in overload protection circuits in the form of series resistors. For example, the AD620 series have thin-film resistors, and the substrate isolation they provide allows input voltages that can exceed the supplies. Other devices use series-protection FETs, e.g. the AMP02 and the AD524, because they act as a low impedance during normal operation, and a high impedance during overvoltage fault conditions. In any instance however, there are always finite safe limits to applied overvoltage (Figure 2-26, again).

In some instances, an additional transient voltage suppressor (TVS) may be required across the input pins to limit the maximum differential input voltage. This is especially applicable to three op amp in amps operating at high gain with low values of RG.

A more detailed discussion of input overvoltage and EMI/RFI protection can be found in Chapter 11 of this book.

SECTION 2-4 Differential Amplifiers

Many high performance analog-to-digital converters (ADCs) are now being designed with differential inputs. A fully differential ADC design offers the advantages of good CM rejection, reduction in second-order distortion products, and simplified DC trim algorithms. Although they can be driven single ended, a fully differential driver usually optimizes overall performance.

One of the most common ways to drive a differential input ADC is with a transformer. However, there are many applications where the ADCs cannot be driven with transformers because the frequency response must extend to DC. In these cases, differential drivers are required.

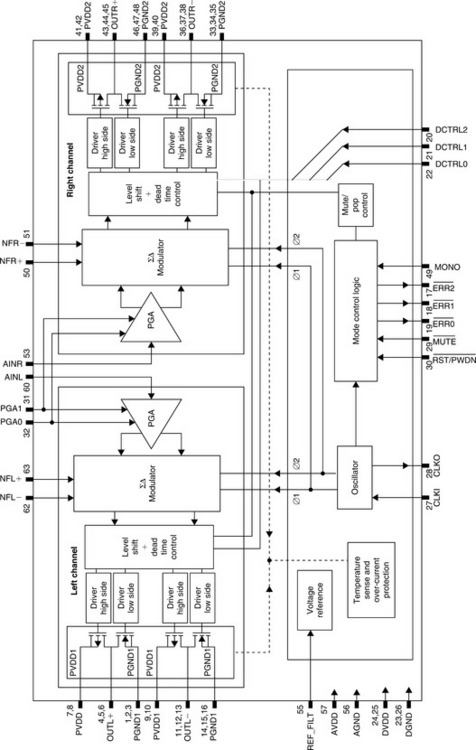

A block diagram of the AD813X family of fully differential amplifiers optimized for ADC driving is shown in Figure 2-27 (see References 3–5). Figure 2-27(A) shows the details of the internal circuit, and Figure 2-27(B) shows the equivalent circuit. The gain is set by the external RF and RG resistors, and the

CM voltage is set by the voltage on the VOCM pin. The internal CM feedback forces the VOUT+ and VOUT− outputs to be balanced, i.e., the signals at the two outputs are always equal in amplitude but 180° out of phase as per the equation:

The circuit can be used with either a differential or a single-ended input, and the voltage gain is equal to the ratio of RF to RG.

If a buffered differential voltage output is required from a current output DAC, the AD813X-series of differential amplifiers can be used as shown in Figure 2-28.

The DAC output current is first converted into a voltage that is developed across the 25 Ω resistors. The voltage is amplified by a factor of 5 using the AD813X. This technique is used in lieu of a direct I/V conversion to prevent fast slewing DAC currents from overloading the amplifier and introducing distortion. Care must be taken so that the DAC output voltage is within its compliance rating.

The VOCM input on the AD813X can be used to set a final output CM voltage within the range of the AD813X. If transmission lines are to be driven at the output, adding a pair of 75 Ω resistors will allow this.

Note also that these amplifiers can be used with single-ended inputs as well. Grounding one of the inputs turns these amplifiers into single ended to differential converters.

SECTION 2-5 Isolation Amplifiers

Analog Isolation Techniques

There are many applications where it is desirable, or even essential, for a sensor to have no direct (“galvanic”) electrical connection with the system to which it is supplying data. This might be in order to avoid the possibility of dangerous voltages or currents from one-half of the system doing damage in the other, or to break an intractable ground loop. Such a system is said to be “isolated,” and the arrangement that passes a signal without galvanic connections is known as an isolation barrier.

The protection of an isolation barrier works in both directions, and may be needed in either, or even in both. The obvious application is where a sensor may encounter high voltages, such as monitoring the current in an AC induction motor, and the system it is driving must be protected. Or a sensor may need to be isolated from accidental high voltages arising downstream, in order to protect its environment: examples include the need to prevent the ignition of explosive gases by sparks at sensors and the protection from electric shock of patients whose ECG, EEG, or EMG is being monitored. The ECG case is interesting, as protection may be required in both directions: the patient must be protected from accidental electric shock, but if the patient’s heart should stop, the ECG machine must be protected from the very high voltages (>7.5 kV) applied to the patient by the defibrillator which will be used to attempt to restart it.

Just as interference, or unwanted information, may be coupled by electric or magnetic fields, or by electromagnetic radiation, these phenomena may be used for the transmission of wanted information in the design of isolated systems.

The most common isolation amplifiers use transformers, which exploit magnetic fields, and another common type uses small high voltage capacitors, exploiting electric fields. Optoisolators, which consist of an LED and a photocell, provide isolation by using light, a form of electromagnetic radiation. Different isolators have differing performance: some are sufficiently linear to pass high accuracy analog signals across an isolation barrier. With others, the signal may need to be converted to digital form before transmission for accuracy is to be maintained (note this is a common V/F converter application).

Transformers are capable of analog accuracy of 12–16 bits and bandwidths up to several hundred kHz, but their maximum voltage rating rarely exceeds 10 kV, and is often much lower. Capacitively coupled isolation amplifiers have lower accuracy, perhaps 12 bits maximum, lower bandwidth, and lower voltage ratings—but they are low cost. Optical isolators are fast and cheap, and can be made with very high voltage ratings (4–7 kV is one of the more common ratings), but they have poor analog domain linearity, and are not usually suitable for direct coupling of precision analog signals.

Linearity and isolation voltage are not the only issues to be considered in the choice of isolation systems. Operating power is of course, essential. Both the input and the output circuitry must be powered, and unless there is a battery on the isolated side of the isolation barrier (which is possible, but rarely convenient), some form of isolated power must be provided. Systems using transformer isolation can easily use a transformer (either the signal transformer or another one) to provide isolated power, but it is impractical to transmit useful amounts of power by capacitive or optical means. Systems using these forms of isolation must make other arrangements to obtain isolated power supplies—this is a powerful consideration in favor of choosing transformer isolated isolation amplifiers: they almost invariably include an isolated power supply.

The isolation amplifier has an input circuit that is galvanically isolated from the power supply and the output circuit. In addition, there is minimal capacitance between the input and the rest of the device. Therefore, there is no possibility for DC current flow, and minimum AC coupling. Isolation amplifiers are intended for applications requiring safe, accurate measurement of low frequency voltage or current (up to about 100 kHz) in the presence of high CM voltage (to thousands of volts) with high CMR. They are also useful for line-receiving of signals transmitted at high impedance in noisy environments, and for safety in general-purpose measurements, where DC and line-frequency leakage must be maintained at levels well below certain mandated minimums. Principal applications are in electrical environments of the kind associated with medical equipment, conventional and nuclear power plants, automatic test equipment, and industrial process control systems.

AD210 Three-Port Isolator

A basic form of isolator is the three-port isolator (input, power, output all isolated) shown in Figure 2-29. Note that in this diagram, the input circuits, output circuits, and power source are all isolated from one another. This Figure represents the circuit architecture of a self-contained isolator, the AD210 (see References 1 and 2).

An isolator of this type requires power from a two-terminal DC power supply (PWR, PWR COM). An internal oscillator (50 kHz) converts the DC power to AC, which is transformer-coupled to the shielded input section, then converted to DC for the input stage and the auxiliary power output. The output current capability of this output is typically limited to ± 15 mA.

The AC carrier is also modulated by the input stage amplifier output, transformer-coupled to the output stage, demodulated by a phase-sensitive demodulator (using the carrier as the reference), filtered, and buffered using isolated DC power derived from the carrier.

The AD210 allows the user to select gains from 1 to 100, using external resistors with the input section op amp. Bandwidth is 20 kHz, and voltage isolation is 2,500 VRMS (continuous) and ± 3,500 VPEAK (continuous).

The AD210 is a three-port isolation amplifier, thus the power circuitry is isolated from both the input and the output stages and may therefore be connected to either (or to neither), without change in functionality. It uses transformer isolation to achieve 3,500 V isolation with 12-bit accuracy.

Motor Control Isolation Amplifier

A typical isolation amplifier application using the AD210 is shown in Figure 2-30. The AD210 is used with an AD620 instrumentation amplifier in a current-sensing system for motor control. The input of the AD210, being isolated, can be directly connected to a 110 or 230 V power line without protection being necessary. The input section’s isolated ± 15 V powers the AD620, which senses the voltage drop in a small value current-sensing resistor. The AD210 input stage op amp is simply connected as a unity-gain follower, which minimizes its error contribution. The 110 or 230 VRMS CM voltage is ignored by this isolated system.

Within this system the AD620 preamp is used as the system scaling control point, and will produce an output voltage proportional to motor current, as scaled by the sensing resistor value and gain as set by the AD620’s RG. The AD620 also improves overall system accuracy, as the AD210’s VOS is 15 mV, versus the AD620’s 30 μV (with less drift also). Note that if higher DC offset and drift are acceptable, the AD620 may be omitted and the AD210 connected at a gain of 100.

Optional Noise Reduction Post Filter

Due to the nature of this type of carrier-operated isolation system, there will be certain operating situations where some residual AC carrier component will be superimposed on the recovered output DC signal. When this occurs, a low impedance passive RC filter section following the output stage may be used (if the following stage has a high input impedance, i.e., non-loading to this filter). Note that it will be the case for many high input impedance sampling ADCs, which appear essentially as small capacitors. A 150 Ω resistance and 1 nF capacitor will provide a corner frequency of about 1 kHz. Note also that the capacitor should be a film type for low errors, such as polypropylene. As an option an active filter may be utilized. Since the output of the filter is low impedance (the output of an op amp), it may be used where the low output is required. Also note that it may be possible to include the anti-aliasing requirement of the ADC into this filter.

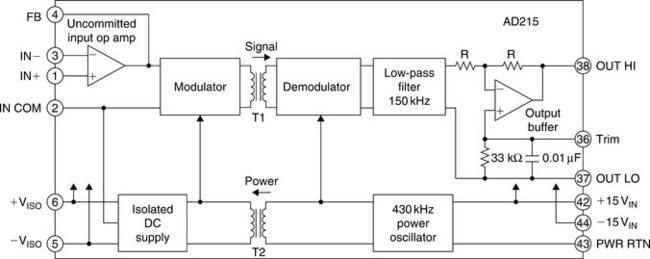

Two-Port Isolator

A two-port isolator differs from a three-port isolator in that the power section is not isolated from the output section. The AD215 is an example of a high speed, two-port isolation amplifier, designed to isolate and amplify wide bandwidth analog signals (see Reference 3). The innovative circuit and transformer design of the AD215 ensures wide-band dynamic characteristics, while preserving DC performance specifications. An AD215 block diagram is shown in Figure 2-31.

The AD215 provides complete galvanic isolation between the input and output of the device, which also includes the user-available front-end isolated bipolar power supply. The functionally complete design, powered by a ± 15 V DC supply on the output side, eliminates the need for a user supplied isolated DC/DC converter. This permits the designer to minimize circuit overhead and reduce overall system design complexity and component costs.

The AD215 has a ± 10 V input/output range, a specified gain range of 1 V/V to 10 V/V, a buffered output with offset trim and a user-available isolated front-end power supply which produces ± 15 V DC at ± 10 mA.

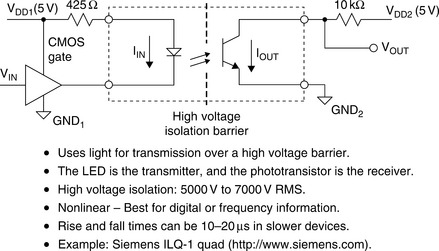

SECTION 2-6 Digital Isolation Techniques

While not a linear circuit, digital isolation is closely related to isolation amplifiers, so they will be discussed here.

Analog isolation amplifiers find many applications where a high isolation is required, such as in medical instrumentation. Digital isolation techniques provide similar galvanic isolation and are a reliable method of transmitting digital signals without ground noise.

Optocouplers (also called optoisolators) are useful and available in a wide variety of styles and packages. A typical optocoupler based on an LED and a phototransistor is shown in Figure 2-32. A current of approximately 10 mA drives an LED transmitter, with light output received by a phototransistor. The light produced by the LED saturates the phototransistor. Input/output isolation of 5,000 VRMS to 7,000 VRMS is common. Although fine for digital signals, optocouplers are too nonlinear for most analog applications. In addition, the transfer characteristics of the optocoupler change with time. Also, since the phototransistor is often being saturated, response times can range from 10 to 20 μs in slower devices, limiting high speed applications.

A much faster optocoupler architecture is shown in Figure 2-33 and is based on an LED and a photodiode. The LED is again driven with a current of approximately 10 mA. This produces a light output sufficient to generate enough current in the receiving photodiode to develop a valid high logic level at the output of the transimpedance amplifier. Speed can vary widely between optocouplers, and the fastest ones have propagation delays of 20 ns typical, and 40 ns maximum, and can handle data rates up to 25 MBd for NRZ data. This corresponds to a maximum square wave operating frequency of 12.5 MHz, and a minimum allowable passable pulse width of 40 ns.

AD260/AD261 High Speed Logic Isolators

The AD260/AD261 family of digital isolators operates on a principle of transformer-coupled isolation (see Reference 4). They provide isolation for five digital control signals to/from high speed DSPs, microcontrollers, or microprocessors. The AD260 also has a 1.5 W transformer for a 3.5 kVRMS isolated external AC/DC power supply circuit.

Each line of the AD260 can handle digital signals up to 20 MHz (40 MBd) with a propagation delay of only 14 ns which allows for extremely fast data transmission. Output waveform symmetry is maintained to within ± 1 ns of the input so the AD260 can be used to accurately isolate time-based pulse width modulator (PWM) signals.

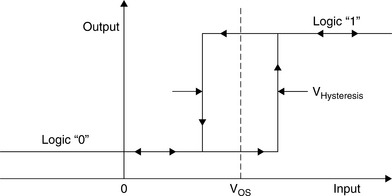

A simplified schematic of one channel of the AD260/AD261 is shown in Figure 2-34. The data input is passed through a Schmitt trigger circuit, through a latch, and a special transmitter circuit which differentiates the edges of the digital input signal and drives the primary winding of a proprietary transformer with a “set-high/set-low” signal.

The secondary of the isolation transformer drives a receiver with the same “set-high/set-low” data, which regenerates the original logic waveform. An internal circuit operating in the background interrogates all inputs about every 5 μs, and in the absence of logic transitions, sends appropriate “set-high/set-low” data across the interface. Recovery time from a fault condition or at power-up is thus between 5 μs and 10 μs.

The power transformer (available on the AD260) is designed to operate between 150 kHz and 250 kHz and will easily deliver more than 1 W of isolated power when driven push–pull (5 V) on the transmitter side. Different transformer taps, rectifier and regulator schemes will provide combinations of ±5 V, 15 V, 24 V, or even 30 V or higher.

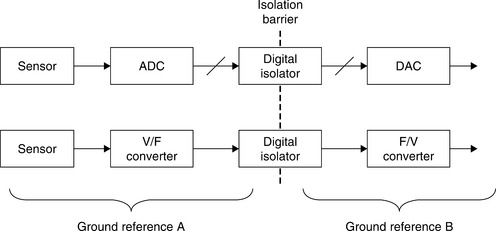

The transformer output voltage when driven with a low voltage drop drive will be 37 Vp−p across the entire secondary with a 5 V push–pull drive. The availability of low cost digital isolators such as those previously discussed solves most system isolation problems in data acquisition systems as shown in Figure 2-35. In the upper example, digitizing the signal first and then using digital isolation eliminates the problem of analog isolation amplifiers. While digital isolation can be used with parallel output ADCs provided the bandwidth of the isolator is sufficient, it is more practical with ADCs that have serial outputs. This minimizes cost and component count. A three-wire interface (data, serial clock, framing clock) is all that is required in these cases.

An alternative (lower example) is to use a voltage-to-frequency converter (VFC) as a transmitter and a frequency-to-voltage converter (FVC) as a receiver. In this case, only one digital isolator is required.

iCoupler® Technology

In many industrial applications, such as process control systems or data acquisition and control systems, digital signals must be transmitted from various sensors to a central controller for processing and analysis. The controller then needs to transmit commands as a result of the analysis performed, coupled with user inputs to various actuators, to achieve certain operations. To maintain safety voltage at the user interface and to prevent transients from being transmitted from the sources, galvanic isolation is required. There are three commonly known classes of isolation devices: optocouplers, capacitively coupled isolators, and transformer-based isolators. Optocouplers rely on light emitting diodes to convert the electrical signals to light signals and on photo detectors to convert the light signals back to electrical signals. The intrinsic low conversion efficiencies for electrical light conversion and slow response photo detectors lead to optocoupler limitations in terms of lifetime, speed, and power assumption. The capacitively coupled isolators have limitations in their size and ability to reject CM voltage transients, while the traditional transformer assembly based isolators are bulky and expensive. All these isolators are restricted, moreover, because of integrated circuit integration limitations and the fact that they often need hybrid packaging.

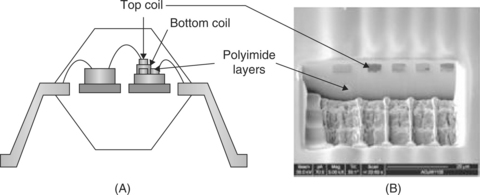

Recently iCoupler®, a new isolation technology, based on chip scale transformers, was developed by Analog Devices. The first product was the ADuM1100 single-channel digital isolator. iCoupler® technology leverages thick-film processing techniques to build microscale on-chip transformers and achieves thousands of volts of isolation on a chip.

iCoupler® isolated transformers can be monolithically integrated with standard silicon ICs and can be fabricated in single- or multichannel configurations. The bidirectional nature of inductive coupling further facilitates bidirectional signal transfer. The combination of high bandwidth for these on-chip transformers and fine-scale CMOS circuitry leads to isolators of unmatched performance characteristics in power, speed, timing accuracy, and ease of use.

ADuM1100 Architecture: A Single-Channel Digital Isolator

The ADuM1100 is a single-channel 100 Mbps digital isolator. It has two ICs packaged in an eight-lead SOIC package. A cross-section view of the ADuM1100 is shown in Figure 2-36. There are two lead frame paddles inside the package, with a gap between them of about 0.4 mm. The molding compound has breakdown strength over 25 kV/mm, so the 0.4 mm gap filled with molding compound provides greater than 10 kV insulation between the substrates of two IC chips.

Figure 2-36: (A) Cross-sectional view of ADuM1100 in an eight-lead SOIC package. (B) Cross-sectional view of the top coil and polyimide layers

The driver chip sitting on the left paddle takes the input digital signal, encodes it, and drives the encoded differential signal through bond wires to the top coils of the transformers built on top of the receiver chip sitting on the right paddle. The driver die is a standard CMOS chip, and the receiver die is a CMOS chip with the additional structures of two polyimide layers and transformer primary coil fabricated on top of the passivation. The polyimide between the top and bottom coils is about 20 μm thick. The breakdown strength of the cured polyimide film is greater than 300 V/m, so 20 μm of polyimide provides greater than 6 kV of insulation between a given transformer’s coils. This provides a comfortable margin over the production test voltage of 3 kVRMS.

Because of the structural quality of these wafer processed polyimide films, no partial discharge over 5 pC can be detected, even at 3 kVRMS. The top coil is gold plated, with a 4-μm thick layer, and the coil track width and spacing between the turns are all 4 μm. The polyimide layers have good mechanical elongation and tensile strength, which also helps the adhesion between the polyimide layers or between the polyimide layer and deposited metal layer. The minimum interaction between the gold film and the polyimide film, coupled with high temperature stability of the polyimide film, results in a system that provides reliable insulation when subjected to various types of environmental stress.

In addition to the fact that thousands of volts of isolation can be achieved on-chip, the ADuM110 also makes it possible to transmit very high bandwidth signals very efficiently, accurately, and reliably. Figure 2-37 shows a simplified schematic of the ADuM1100. To guarantee input stability, the front glitch filter filters out pulses narrower than a pulse width of approximately 2 ns. Upon the receipt of a signal edge, a 1 ns pulse is sent to either Coil 1 or Coil 2. (For a leading edge signal it is sent to Coil 1, and for a falling edge signal to Coil 2.) Once the short pulses are transmitted to the secondary coils (the bottom coils in this case), they are amplified and the input signal is reconstructed through an SR flip-flop to appear as an isolated output. The wide bandwidth of these microscale transformers and high speed CMOS makes the transmission of these short nanosecond pulses possible. Since only signal edges are being used, this transmission scheme is very power efficient. With a very energetic pulse having a current ramping to 100 mA within 1 ns, the average current for a 1 Mbps input signal is only 50 μA. Some additional power is dissipated by the switching of the surrounded CMOS gates. At 5 V, an additional 50 μA/Mbps is needed if the total capacitance of the CMOS gates is 20 pF. The typical optocoupler, on the other hand, dissipates over 10 mA, even operating at 1 Mbps. This represents two orders of magnitude (100×) improvement in power dissipation provided by iCoupler® isolators.

If there is no input change for a certain period of time, approximately 1 μs, the monostable generates a 1 ns pulse and sends it to Coil 1 or Coil 2, depending on the input logic level. The 1 ns refreshing pulse is sent to Coil 1 if input is high and is sent to Coil 2 if input is low. This helps maintain DC correctness for the isolator because normally pulses are transmitted only on reception of a signal edge. The receiver includes a watchdog circuit that will timeout at 2 μs if it is not reset by an incoming pulse. If a timeout happens, the receiver output will return to a default safe level (logic high in the ADuM1100). The combination of refresh and watchdog functions provides the additional advantage of detecting the failure of any field device on the system side. With other isolators, this would ordinarily require the use of an extra isolated data channel.

The bandwidth of the isolator is dependent on the input filter bandwidth within. For example, 500 Mbps can be achieved with a 2 ns input filter. For the ADuM1100, we chose a signal bandwidth of 100 MBd, still 2 times faster than the fastest optocouplers. Very tight edge symmetry between input and output logic signals is also preserved due to the instantaneous nature of the inductive coupling between these microscale on-chip coils.

The ADuM1100 has edge symmetry of better than 2 ns for 5 V operation. As the bandwidth of isolation systems continues to expand, the iCoupler® technology will be capable of meeting the challenge while optocoupler technology is likely to struggle.

In addition to the improvements in efficiency and bandwidth iCoupler® technology provides, it also offers a more robust and reliable isolation solution than competitive offerings. Because high voltage transients are present in many data acquisition and control systems, the ability of the isolator to prevent transients from affecting the logic controller is very important. High performance optocouplers have transient immunity of less than 10 kV/μs, while the ADuM1100 has a transient immunity better than 25 kV/μs. The induced error voltage at the receiver input induced by an input–output transient is given by:

where C is the capacitance between the input coil and the receiver coil, R, is the resistance of the bottom coil, and dV/dt is the magnitude of the transient.

In the ADuM1100, the capacitance between the top (input) coil and the bottom (receiver) coil is only 0.2 pF, while the bottom coil has a resistance of 80 Ω. Thus the error signal induced on the bottom coil by a 25 kV/μs transient on the top coil is only 0.4 V, much less than the receiver detection threshold. The transient immunity of iCoupler® isolators can be optimized through careful selection of the decoder detection threshold, the resistance of the receiving coil, and, of course, the capacitance between the top and bottom coils.

One recurring question about transformer-based isolators involves their magnetic immunity capability. Since iCouplers® use air core technology, no magnetic components are present and the problem of magnetic saturation for the core material does not exist. Therefore, iCouplers® have essentially infinite DC field immunity. The limitation on the ADuM1100’s AC magnetic field immunity is set by the condition in which the induced error voltage in the receiving coil (the bottom coil in this case) is made sufficiently large, either to falsely set or reset the decoder. The voltage induced across the bottom coil is given by:

where β is the magnetic flux density (Gauss), N is the number of turns in receiving coil, and rn is the radius of nth turn in receiving coil (cm).

Because of the very small geometry of the receiving coil in the ADuM1100, even a wire carrying 1,000A at 1 MHz and positioned only 1 cm away from the ADuM1100 would not induce an error voltage large enough to falsely trigger the decoder. Note that at combinations of strong magnetic field and high frequency, any loops formed by printed circuit board traces could induce error voltages sufficiently large to trigger the thresholds of succeeding circuitry. Typically the PC board design rather than the isolator itself is the limiting factor in the presence of such big magnetic transients. In addition to magnetic immunity, the level of electromagnetic radiation emitted from the iCoupler® device is a concern. Using far-field approximation,

where P is the total radiated power and I is the coil loop current.

Again, given the very small geometry of the coils, the total radiated power is still less than 50 pW, even if the part is operating at 0.5 GHz.

ADuM130x/ADuM140x: Multichannel Products

In addition to the many performance improvements discussed previously, iCoupler® technology also offers tremendous advantages in terms of integration. The optical interference makes the realization of multichannel optocouplers very difficult.

Transformers based on iCoupler® technology can be easily integrated onto a single chip. Furthermore, one data channel can transmit signals in one direction, say from the top coil to the bottom coil, while the neighboring channel can transmit a signal in the other direction, from the bottom coil to the top coil. The bidirectional nature of inductive coupling makes this possible.

Additional products consist of five three-channel and four-channel products covering all possible channel directionality configurations. Besides providing flexible channel configurations, they support both 3 V and 5 V operations at either side of the isolation barrier and support the use of these isolators as level translators. One side could be at 2.7 V, e.g., while the other side could be at 5.5 V. The edge symmetry of 2 ns is preserved over all possible supply configurations at all temperatures from −40°C to 100°C. The ability to mix bidirectional channels of isolation in a single package enables users to reduce the size and cost of their systems.

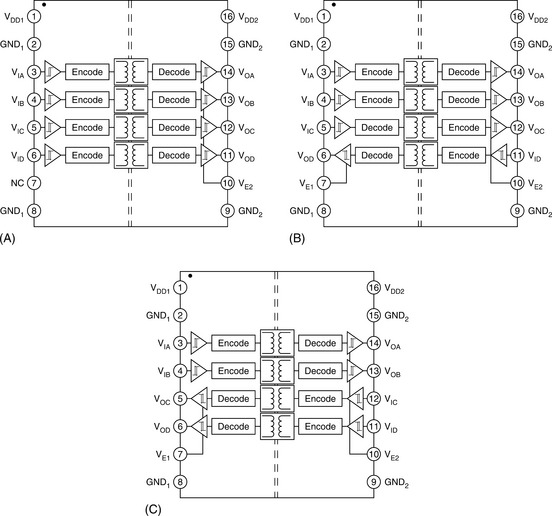

For the ADuM1100, two transformers are used to transmit a single channel of data. One is dedicated to transmit pulses representing the signal’s leading edge or updating input high, and the other is dedicated to transmit pulses representing the signal’s falling edge or updating input low. For the ADuM130x/ADuM140x product family, a single transformer is used for each data channel. The ADuM140x shown in Figure 2-38 has four transformers in total. The leading edge and falling edge are encoded differently, and the encoded pulses are combined in the same transformer; as a result, the receiver has responsibility for decoding the pulses to see whether they are for leading edge or falling edge. The output signal is then reconstructed correspondingly (Figure 2-39).

Of course, there is a penalty for using a single transformer per data channel rather than using two transformers per data channel. The propagation delay is longer for the single transformer architecture because of the additional encode and decode time needed. The penalty for bandwidth is hardly a factor, even at input speed of 100 Mbps.

In contrast to the ADuM1100, the ADuM130x/ADuM140x uses a dedicated transformer chip, separate from the receiver integrated circuit. This partitioning exemplifies the ease of integration for iCoupler technology. Besides standalone multichannel isolators, the iCoupler technology can be embedded with other data acquisition and control ICs to make the use of isolation even more transparent. Consequently, in the future, system designers will be able to devote their time to improving system functionality, rather than worrying about isolation.

SECTION 2-7 Active Feedback Amplifiers

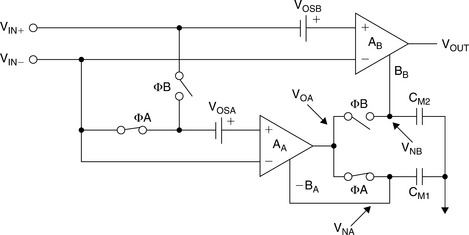

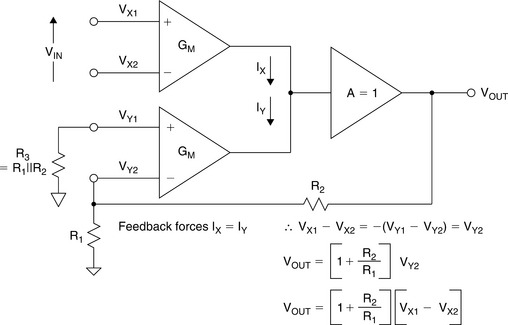

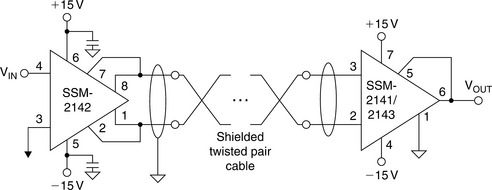

The AD8129/AD8130 differential line receivers, along with their predecessor the AD830, utilize a novel amplifier topology called active feedback (see Reference 8). A simplified block diagram of these devices is shown in Figure 2-40.

The AD830 and the AD8129/AD8130 have two sets of fully differential inputs, available at VX1−VX2 and VY1−VY2, respectively. Internally, the outputs of the two GM stages are summed and drive a buffer output stage.

In this device the overall feedback loop forces the internal currents IX and IY to be equal. This condition forces the differential voltages VX1−VX2 and VY1−VY2 to be equal and opposite in polarity. Feedback is taken from the output back to one input differential pair, while the other pair is driven directly by an input differential input signal.

An important point of this architecture is that high CM rejection is provided by the two differential input pairs, so CMR is not dependent on resistor bridges and their associated matching problems. The inherently wideband balanced circuit and the quasi-floating operation of the driven input provide the high CMR, which is typically 100 dB at DC.

One way to view this topology is as a standard op amp in a non-inverting mode with a pair of differential inputs in place of the op amps standard inverting and non-inverting inputs. The general expression for the stage’s gain “G” is like a non-inverting op amp, or:

As should be noted, this expression is identical to the gain of a non-inverting op amp stage, with R2 and R1 in analogous positions.

The AD8129 is a low noise high gain (G = 10 or greater) version of this family, intended for applications with very long cables where signal attenuation is significant. The related AD8130 device is stable at a gain of one. It is used for those applications where lower gains are required, such as a gain of two, for driving source and load terminated cables.

The AD8129 and AD8130 have a wide power supply range, from single + 5 V to ± 12 V, allowing wide CM and differential-mode voltage ranges. The wide CM range enables the driver/receiver pair to operate without isolation transformers in many systems where the ground potential difference between driver and receiver locations is several volts. Both devices include a logic-controlled power-down function.

Both devices have high, balanced input impedances, and achieve 70 dB CMR @ 10 MHz, providing excellent rejection of high frequency CM signals. Figure 2-41 shows AD8130 CMR for various supplies. As can be noted, it can be as high as 95 dB at 1 MHz, an impressive figure considering that no trimming is required.

The typical 3 dB bandwidth for the AD8129 is 200 MHz, while the 0.1 dB bandwidth is 30 MHz in the SOIC package, and 50 MHz in the μSOIC package. The conditions for these specifications are for VS = ±5 V and G = 10.

The typical 3 dB bandwidth for the AD8130 is 270 MHz, and the 0.1 dB bandwidth is 45 MHz, in either package. The conditions for these specifications are for VS = ±5 V and G = 1. Typical differential gain and phase specifications for the AD8130 for G = 2, VS = ±5 V, and RL = 150 Ω are 0.13% and 0.15°, respectively.

SECTION 2-8 Logarithmic Amplifiers

The term “logarithmic amplifier” (generally abbreviated to “log amp”) is something of a misnomer, and “logarithmic converter” would be a better description. The conversion of a signal to its equivalent logarithmic value involves a nonlinear operation, the consequences of which can be confusing if not fully understood. It is important to realize that many of the familiar concepts of linear circuits are irrelevant to log amps. For example, the incremental gain of an ideal log amp approaches infinity as the input approaches zero, and a change of offset at the output of a log amp is equivalent to a change of amplitude at its input—not a change of input offset.

For the purposes of simplicity in our initial discussions, we shall assume that both the input and the output of a log amp are voltages, although there is no particular reason why logarithmic current, transimpedance, or transconductance amplifiers could not also be designed.

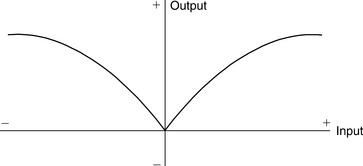

If we consider the equation y = log(x) we find that every time x is multiplied by a constant A, y increases by another constant A1. Thus if log(K) = K1, then log(AK) = K1 + A1, log(A2K) = K1 + 2A1, and log(K/A) = K1−A1. This gives a graph as shown in Figure 2-42, where y is zero when x is unity, y approaches minus infinity as x approaches zero, and where y has no values for which x is negative.

On the whole, log amps do not behave in this way. Apart from the difficulties of arranging infinite negative output voltages, such a device would not, in fact, be very useful. A log amp must satisfy a transfer function of the form:

over some range of input values which may vary from 100:1 (40 dB) to over 1,000,000:1 (120 dB).

With inputs very close to zero, log amps cease to behave logarithmically, and most then have a linear VIN/VOUT law. This behavior is often lost in device noise. Noise often limits the dynamic range of a log amp. The constant, VY, has the dimensions of voltage, because the output is a voltage. The input, VIN, is divided by a voltage, VX, because the argument of a logarithm must be a simple dimensionless ratio.

A graph of the transfer characteristic of a log amp is shown in Figure 2-43. The scale of the horizontal axis (the input) is logarithmic, and the ideal transfer characteristic is a straight line. When VIN = VX, the logarithm is zero (log 1 = 0). VX is therefore known as the intercept voltage of the log amp because the graph crosses the horizontal axis at this value of VIN.

The slope of the line is proportional to VY. When setting scales, logarithms to the base 10 are most often used because this simplifies the relationship to decibel values: when VIN = 10 VX, the logarithm has the value of 1, so the output voltage is VY. When VIN = 100 VX, the output is 2 VY, and so forth. VY can therefore be viewed either as the “slope voltage” or as the “volts per decade factor.”

The logarithm function is indeterminate for negative values of x. Log amps can respond to negative inputs in three different ways: (1) They can give a full-scale negative output as shown in Figure 2-44. (2) They can give an output which is proportional to the log of the absolute value of the input and disregards its sign as shown in Figure 2-45. This type of log amp can be considered to be a full-wave detector with a logarithmic characteristic and is often referred to as a detecting log amp. (3) They can give an output which is proportional to the log of the absolute value of the input and has the same sign as the input as shown in Figure 2-46. This type of log amp can be considered to be a video amp with a logarithmic characteristic, and may be known as a logarithmic video (log video) amplifier or, sometimes, a true log amp (although this type of log amp is rarely used in video-display-related applications).

There are three basic architectures which may be used to produce log amps: the basic diode log amp, the successive detection log amp, and the true log amp which is based on cascaded semi-limiting amplifiers. The successive detection log amp and the true log amp are discussed in the RF/IF section.

The voltage across a silicon diode is proportional to the logarithm of the current through it. If a diode is placed in the feedback path of an inverting op amp, the output voltage will be proportional to the log of the input current as shown in Figure 2-47. In practice, the dynamic range of this configuration is limited to 40–60 dB because of non-ideal diode characteristic, but if the diode is replaced with a diode-connected transistor as shown in Figure 2-48, the dynamic range can be extended to 120 dB or more. This type of log amp has three disadvantages: (1) both the slope and intercept are temperature dependent; (2) it will only handle unipolar signals; and (3) its bandwidth is both limited and dependent on signal amplitude.

Where several such log amps are used on a single chip to produce an analog computer which performs both log and antilog operations, the temperature variation in the log operations is unimportant, since it is compensated by a similar variation in the antilogging. This makes possible the AD538 (Figure 2-49), a monolithic analog computer which can multiply, divide, and raise to powers. Where actual logging is required, however, the AD538 and similar circuits require temperature compensation (Reference 7). The major disadvantage of this type of log amp for high frequency applications, though, is its limited frequency response—which cannot be overcome. However carefully the amplifier is designed, there will always be a residual feedback capacitance, CC (often known as Miller capacitance), from output to input which limits the high frequency response.

What makes this Miller capacitance particularly troublesome is that the impedance of the emitter–base junction is inversely proportional to the current flowing in it—so that if the log amp has a dynamic range of 1,000,000:1, then its bandwidth will also vary by 1,000,000:1. In practice, the variation is less because other considerations limit the large signal bandwidth, but it is very difficult to make a log amp of this type with a small signal bandwidth greater than a few hundred kHz.

We also discuss high speed log amps in the RF/IF section (Section 4-4).

SECTION 2-9 High Speed Clamping Amplifiers

There are many situations where it is desirable to clamp the output of an op amp to prevent overdriving the circuitry which follows. Specially designed high speed, fast recovery clamping amplifiers offer an attractive alternative to designing external clamping/protection circuits. The AD8036/AD8037’s low distortion, wide bandwidth clamp amplifiers represent a significant breakthrough in this technology. These devices allow the designer to specify a high (VH) and low (VL) clamp voltage. The output of the device clamps when the input exceeds either of these two levels. The AD8036/AD8037 offers superior clamping performance compared to competing devices that use output clamping. Recovery time from overdrive is less than 5 ns.

The key to the AD8036 and AD8037’s fast, accurate clamp and amplifier performance is their proprietary input clamp architecture. This new design reduces clamp errors by more than 10× over previous output clamp-based circuits, as well as substantially increasing the bandwidth, precision, and versatility of the clamp inputs.

Figure 2-50 shows an idealized block diagram of the AD8036 connected as a unity-gain voltage follower. The primary signal path comprises A1 (a 1,200 V/μs, 240 MHz high voltage gain, differential to single-ended amplifier) and A2 (a G = +1 high current gain output buffer). The AD8037 differs from the AD8036 only in that A1 is optimized for closed-loop gains of two or greater.

The input clamp section is composed of comparators CH and CL, which drive switch S1 through a decoder. The unity-gain buffers in series with the +VIN, VH, and VL inputs isolate the input pins from the comparators and S1 without reducing bandwidth or precision.

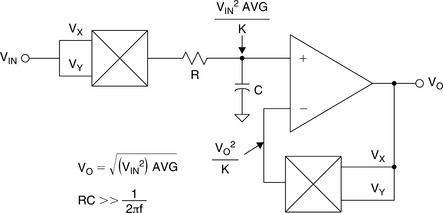

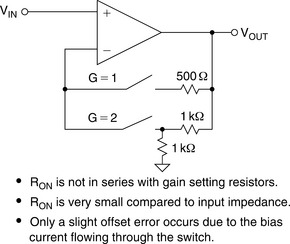

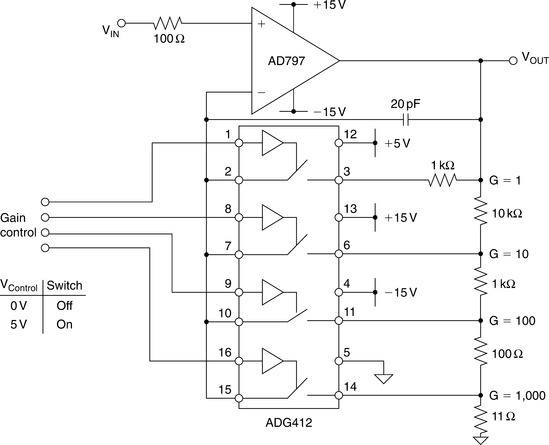

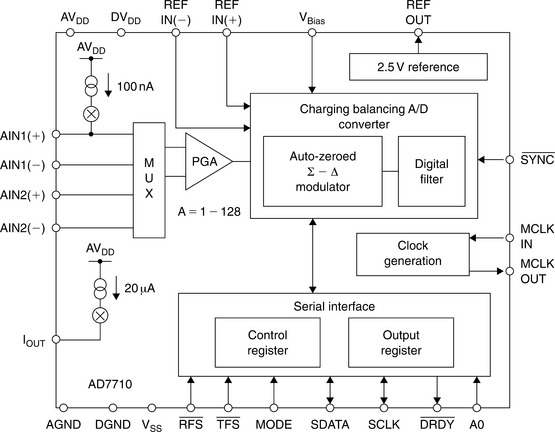

The two comparators have about the same bandwidth as A1 (240 MHz), so they can keep up with signals within the useful bandwidth of the AD8036. To illustrate the operation of the input clamp circuit, consider the case where VH is referenced to +1 V, VL is open, and the AD8036 is set for a gain of + 1 by connecting its output back to its inverting input through the recommended 140 Ω feedback resistor. Note that the main signal path always operates closed loop, since the clamping circuit only affects A1’s non-inverting input.