CHAPTER 6 Converters

![]() Section 6-1: DAC Architectures

Section 6-1: DAC Architectures

![]() Section 6-2: ADC Architectures

Section 6-2: ADC Architectures

![]() Section 6-3: Sigma–Delta Converters

Section 6-3: Sigma–Delta Converters

![]() Section 6-4: Defining the Specifications

Section 6-4: Defining the Specifications

![]() Section 6-5: DAC and ADC Static Transfer Functions and DC Errors

Section 6-5: DAC and ADC Static Transfer Functions and DC Errors

![]() Section 6-6: Data Converter AC Errors

Section 6-6: Data Converter AC Errors

![]() Section 6-7: Timing Specifications

Section 6-7: Timing Specifications

Chapter Introduction

There are two basic types of converters, digital-to-analog (DACs or D/As) and analog-to-digital (ADCs or A/Ds). Their purpose is fairly straightforward. In the case of DACs, they output an analog voltage that is a proportion of a reference voltage, the proportion based on the digital word applied. In the case of ADCs, a digital representation of the analog voltage that is applied to the ADCs input is outputted, the representation proportional to a reference voltage.

In both cases the digital word is almost always based on a binarily weighted proportion. The digital input or output is arranged in words of varying widths, referred to as bits, typically anywhere from 6 bits to 24 bits. In a binarily weighted system each bit is worth half of the bit to its left and twice the bit to its right. The greater the number of bits in the digital word, the finer the resolution. These bits are typically arranged in groups of 4, called bytes, for convenience.

For a better understanding of the relationship between the digital domain and the analog domain please refer to the section on sampling theory.

As stated earlier, we shall look at the operation of converters primarily from a “black box” view. We will concern ourselves less with the internal construction of the converter and more with its operation. We cannot, however, completely ignore the internal architecture because in many cases it is relevant to operational advantages or limitations. There are a number of works that cover the internal workings of the converters in much more detail (see references).

Another point that should be kept in mind is the difference between accuracy and resolution. The resolution of a converter is the number of bits in its digital word. The accuracy is the number of those bits that meet the specifications. For instance, a DAC might have 16 bits of resolution, but might only be monotonic to 14 bits. This means that the assured accuracy of the DAC will be no better than 14 bits. Also, an audio ADC might have a digital word width of 16 bits, but the signal-to-noise ratio (SNR) may be only 70 dB. This means that the accuracy will only be at the 12-bit level. This is not to say that the other bits are irrelevant. With further processing, typically filtering, often the accuracy can be improved. While these terms are similar and sometimes used interchangeably, the distinction between the two should be remembered.

SECTION 6-1 DAC Architectures

DACs or D/As Introduction

What we commonly refer to as a DAC today is typically quite a bit more. The DAC will typically have the converter itself and a collection of support circuitry built into the chip (Figure 6-1).

The first DACs were board level designs, built from discrete components, including vacuum tubes as the switching elements. Monolithic DACs began to appear in the early 1970s. These early examples were actually sub-blocks of the DAC. An example of this would be the AD550, which was a 4 bit binarily weighted current source. This current source block would be mated to a separate part, such as the AD850, which contained a resistor array and complementary-MOS (CMOS) switches. Together these would form the basic DAC. As we moved on in time these functions were integrated on the same die, additional digital circuitry, specifically latches to store the digital input, were added. Then a second rank of latches were often added. The purpose of the second rank was to allow the microprocessor or microcontroller to write many DACs in a system and update them all at the same time. The input rank of latches could also be a shift register, which would allow a serial interface.

On the back end, since the output of the DAC is often a current, an op amp is often added to perform the current-to-voltage (I/V) conversion. On the front end a voltage reference is often added.

Process limitations did not allow the integration of all these sub-blocks to occur at once. Initially, the processes used to make the various sub-blocks were not compatible. The process that made the best switches was typically not the best for the amplifier and the reference. As the processes became more advanced these limitations became less. Today CMOS can make acceptable amplifiers and processes combining bipolar and CMOS together exist.

There are several advantages to including all this additional circuitry in one package. The first is the obvious advantage of reducing the chip count. This reduces the size of the circuitry and increases the reliability. Probably more important is that the circuit designer now does not have to concern himself with the accuracy of several parts in a system. The system is now one part and tested by the manufacturer as a unit.

Next we will look at the various DAC architectures. When we refer to DACs here we are referring to the basic converter rather than the complete system.

Kelvin Divider (String DAC)

The simplest structure of all is the Kelvin divider or string DAC as shown in Figure 6-2. An N-bit version of this DAC simply consists of 2N equal resistors in series and 2N switches (usually CMOS), one between each node of the chain and the output. The output is taken from the appropriate tap by closing just one of the switches (there is some slight digital complexity involved in decoding to 1 of 2N switches from N-bit data).

This architecture is simple, has a voltage output, and is inherently monotonic—even if a resistor is accidentally short-circuited, output n cannot exceed output n + 1. It is linear if all the resistors are equal, but may be made deliberately nonlinear if a nonlinear DAC is required. The output is a voltage, but it has the disadvantage of having a relatively large output impedance. This output impedance is also code dependent (the impedance changes with changes to the digital input). In many cases it will be beneficial to follow the output of the DAC with an op amp to buffer this output impedance and present a low impedance source to the following circuitry.

Since only two switches operate during a transition it is a low glitch architecture (the concept of glitch will be examined in a following section). Also, the switching glitch is not code-dependent, making it ideal for low distortion applications. Because the glitch is constant regardless of the code transition, the frequency content of the glitch is at the DAC update rate and its harmonics—not at the harmonics of the DAC output signal frequency. The major drawback of the Kelvin DAC is the large number of resistors and switches required for high resolution. There are 2N resistors required, so a 10-bit DAC would require 1,024 switches and resistors, and as a result it was not commonly used as a simple DAC architecture until the recent advent of very small integrated circuit (IC) feature sizes made it very practical for low and medium resolution (typically up to 10 bits) DACs.

As we mentioned in the section on sampling theory, the output of a DAC for an all 1s code is 1 least significant bit (LSB) below the reference, so a Kelvin divider DAC intended for use as a general purpose DAC has a resistor between the reference terminal and the first switch as shown in Figure 6-2.

Segmented String DACs

A variation of the Kelvin divider is the segmented string DAC. Here we reduce the number of resistors required by segmenting. Figure 6-3 shows two varieties of segmented voltage-output DAC. The architecture in Figure 6-3(A) is sometimes called a Kelvin–Varley divider. Since there are buffers between the first and second stages, the second string DAC does not load the first, and the resistors in the second string do not need to have the same value as the resistors in the first. All the resistors in each string, however, do need to be equal to each other or the DAC will not be linear. The examples shown have 3-bit first and second stages but for the sake of generality, let us refer to the first (most significant bit (MSB)) stage resolution as M bits and the second (LSB) as K bits for a total of N = M + K bits. The MSB DAC has a string of 2M equal resistors, and a string of 2K equal resistors in the LSB DAC. As an example if we make a 10-bit string DAC out of two 5-bit sections, each segment would have 25 or 32 resistors, for a total of 64, as opposed to the 1,024 required for a standard Kelvin divider. This is an obvious advantage.

Buffer amplifiers can have offset, of course, and this can cause non-monotonicity in a buffered segmented string DAC.

In the simpler configuration of a buffered Kelvin–Varley divider buffer (Figure 6-3(A)), buffer A is always “below” (at a lower potential than) buffer B, and the extra tap labeled “A” on the LSB string DAC is not necessary. The data decoding is just two priority encoders.

But if the decoding of the MSB string DAC is made more complex so that buffer A can only be connected to the taps labeled “A” in the MSB string DAC, and buffer B to the taps labeled “B,” then it is not possible for buffer offsets to cause non-monotonicity. Of course, the LSB string DAC decoding must change direction each time one buffer “leapfrogs” the other, and taps A and B on the LSB string DAC are alternately not used—but this involves a fairly trivial increase in logic complexity and is justified by the increased performance.

Rather than using a second string of resistors, a binary R–2R DAC can be used to generate the three LSBs as shown in Figure 6-3(B). This voltage-output DAC (Figure 6-3(B)) consists of a 3-bit string DAC followed by a 3-bit buffered voltage-mode ladder network. Again the number of resistors required for the DAC is reduced.

An unbuffered version of the segmented string DAC is shown in Figure 6-4. This version is more clever in concept. Here, the resistors in the two strings must be equal, except that the top resistor in the MSB string must be smaller—1/(2K) of the value of the others—and the LSB string has 2K −1 resistors rather than 2K. Because there are no buffers, the LSB string appears in parallel with the resistor in the MSB string that is switched across and loads it. This drops the voltage across that MSB resistor by 1 LSB of the LSB DAC—which is exactly what is required. The output impedance of this DAC, being unbuffered, varies with changing digital code. This circuit is intrinsically monotonic since it is unbuffered (and, of course, can be manufactured on CMOS processes which make resistors and switches but not high precision amplifiers, so it may be cheaper as well).

In order to understand this clever concept better, the actual voltages at each of the taps has been worked out and labeled for the 6-bit segmented DAC composed of two 3-bit string DACs shown in Figure 6-4. The reader is urged to go through this simple analysis with the second string DAC connected across any other resistor in the first string DAC and verify the numbers. A detailed mathematical analysis of the unbuffered segmented string DAC can be found in the relevant patent filed by Dennis Dempsey and Christopher Gorman of Analog Devices in 1997 (Reference 14).

Digital Pots

Another variation of the string DAC is the digital potentiometer. A simple digital potentiometer is shown in Figure 6-5.

The major difference is that the lower arm of the pot (terminal B) is not connected to ground, but is instead left floating. The absolute values of the resistors in a Kelvin DAC typically are not critical. They are limited by the available material. They must, of course, be the same as each other. In a digital pot the end-to-end resistance is specified. The accuracy of the end-to-end resistance is on the order of a mechanical pot.

Digital pots are typically available in end-to-end resistance values from 10 kΩ to 1 MΩ. Lower values of end-to-end resistance are difficult since the on-resistance of the CMOS switches is on the order of the resistor segment, so the linearity of the pot suffers at the low end.

The advantages to digital pots are many. Even the lowest resolution digital pots have better setability than their mechanical counterparts. Also they are immune to mechanical vibration and oxidation of the wiper contact. Obviously, adjustments can be made without human intervention.

In most digital pots the voltage on the input pins cannot exceed the supplies (typically 3 V or 5 V) due to the CMOS switches used in their construction, but certain models are designed for ± 15 V operation.

Another design feature on many of the digital pots is that on power-up (sometimes from an internal timer, sometimes controlled by an external pin) the wiper is shorted to one of the terminals. This is useful since output on power-up is undefined until it is written to. Since it might take a while (relatively) for the microcontroller to initialize itself and then get around to initializing the rest of the system, having the digital pot in a known state can be useful. Some digital potentiometers incorporate non-volatile logic so that their settings are retained when they are turned off.

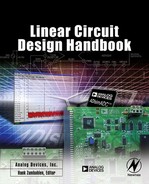

One time programmable (OTP) versions of digital pots have become available. Here the digital code is locked into the pot once the setting had been determined. The technology used is fusible links. A variation on this theme is the two times programmable (TTP) digital pot. This allows the non-volatile settings to be modified one time. The block diagram of a TTP digital pot is shown in Figure 6-6.

Thermometer (Fully Decoded) DACs

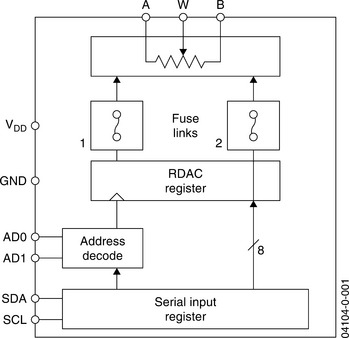

There is a current-output DAC architecture analogous to a string DAC which consists of 2N–1 switchable current sources (which may be resistors and a voltage reference or may be active current sources) connected to an output terminal. This output must be at, or close to, ground. Figure 6-7 shows a thermometer DAC which uses resistors connected to a reference voltage to generate the currents.

If active current sources are used as shown in Figure 6-8, the output may have more compliance (the allowable voltage on the output pin which still guarantees performance), and a resistive load is typically used to develop an output voltage. The load resistor must be chosen so that at maximum output current the output terminal remains within its rated compliance voltage.

Once a current in a thermometer DAC is switched into the circuit by increasing the digital code, any further increases do not switch it out again. The structure is thus inherently monotonic, irrespective of inaccuracies in the currents. Again, like the Kelvin divider, only the advent of high density IC processes has made this architecture practical for general purpose medium resolution DACs, although a slightly more complex version—shown in the next diagram—is quite widely used in high speed applications. Unlike the Kelvin divider, this type of current-mode DAC does not have a unique name, although both types may be referred to as fully decoded DACs or thermometer DACs.

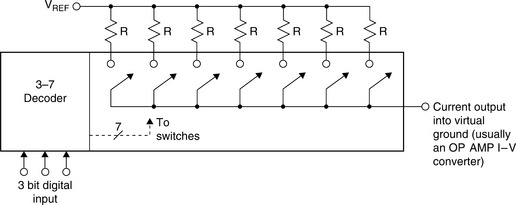

A DAC where the currents are switched between two output lines—one of which is often grounded, but may, in the more general case, be used as the inverted output—is more suitable for high speed applications because switching a current between two outputs is far less disruptive, and so causes a far lower glitch than simply switching a current on and off. This architecture is shown in Figure 6-9.

But the settling time of this DAC still varies with initial and final code, giving rise to intersymbol distortion (ISI). This can be addressed with even more complex switching where the output current is returned to zero before going to its next value. Note that although the current in the output is returned to zero it is not “turned off”—the current is dumped to ground when it is not being used, rather than being switched on and off. The techniques involved are too complex to discuss in detail here but can be found in the references.

In the normal (linear) version of this DAC, all the currents are nominally equal. Where it is used for high speed reconstruction, its linearity can also be improved by dynamically changing the order in which the currents are switched by ascending code. Instead of code 001 always turning on current A; code 010 always turning on currents A and B; code 011 always turning on currents A, B, and C; etc. the order of turn-on relative to ascending code changes for each new data point. This can be done quite easily with a little extra logic in the decoder. The simplest way of achieving it is with a counter which increments with each clock cycle so that the order advances: ABCDEFG, BCDEFGA, CDEFGAB, etc. but this algorithm may give rise to spurious tones in the DAC output. A better approach is to set a new pseudo-random order on each clock cycle—this requires a little more logic, but even complex logic is now very cheap and easily implemented on CMOS processes. There are other, even more complex, techniques which involve using the data itself to select bits and thus turn current mismatch into shaped noise. Again they are too complex for a book of this sort (see references for a more detailed discussion).

Binary-Weighted Current Source

The voltage-mode binary-weighted resistor DAC shown in Figure 6-10 is usually the simplest textbook example of a DAC. However, this DAC is not inherently monotonic and is actually quite hard to manufacture successfully at high resolutions due to the large spread in component (resistor) values. In addition, the output impedance of the voltage-mode binary DAC changes with the input code.

Current-mode binary-weighted DACs are shown in Figure 6-11(A) (resistor-based), and Figure 6-11(B) (current-source based). An N-bit DAC of this type consists of N-weighted current sources (which may simply be resistors and a voltage reference) in the ratio 1:2:4:8: …:2N–1. The LSB switches the 2N–1 current, the MSB the 1 current, etc. The theory is simple but the practical problems of manufacturing an IC of an economical size with current or resistor ratios of even 128:1 for an 8-bit DAC are enormous, especially as they must have matched temperature coefficients. This architecture is virtually never used on its own in IC DACs, although, again, 3- or 4-bit versions have been used as components in more complex structures. For example, the AD550 mentioned at the beginning of this section is an example of a binary-weighted DAC.

If the MSB current is slightly low in value, it will be less than the sum of the other bit currents, and the DAC will not be monotonic (the differential nonlinearity (DNL) of most types of DAC is worst at major bit transitions).

However, there is another binary-weighted DAC structure which has recently become widely used. This uses binary-weighted capacitors as shown in Figure 6-12. The problem with a DAC using capacitors is that leakage causes it to lose its accuracy within a few milliseconds of being set. This may make capacitive DACs unsuitable for general purpose DAC applications, but it is not a problem in successive approximation ADCs, since the conversion is complete in a few microseconds or less—long before leakage has any appreciable effect.

The use of capacitive charge redistribution DACs offers another advantage as well—the DAC itself behaves as a sample-and-hold amplifier (SHA) circuit, so not only is an external SHA unnecessary with these ADCs, there is no need to allocate separate chip area for a separate integral SHA.

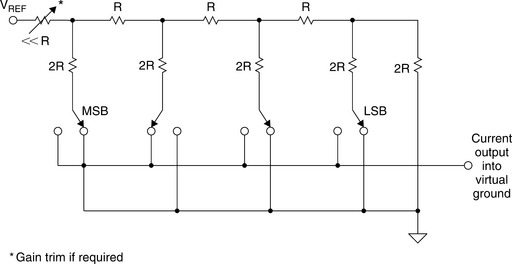

R–2R Ladder

One of the most common DAC building-block structures is the R–2R resistor ladder network shown in Figure 6-13. It uses resistors of only two different values, and their ratio is 2:1. An N-bit DAC requires 2 N resistors, and they are quite easily trimmed. There are also relatively few resistors to trim.

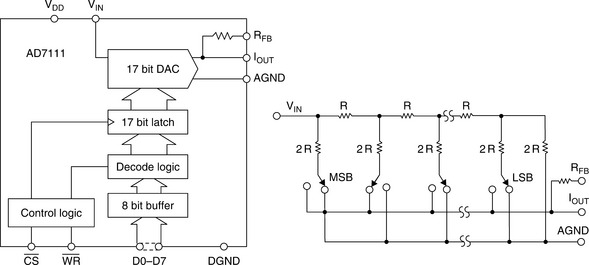

This structure is the basis of a large family of DACs. Figure 6-14 is the block diagram of the AD7524, which is typical of a basic current-output CMOS DAC. The diagram shows the structure of the DAC.

The input impedance (basically the value of the resistors) is not a closely specified parameter. The specified range is 4:1 (5 kΩ minimum, 20 kΩ maximum, although it is typically closer than that). It is the relative accuracy, not the absolute accuracy of the resistors that is of interest. In most applications the absolute value is not important. Certain applications exist where the value does matter. In these instances, the parts must be selected at test.

Note the extra resistor added at the RFEEDBACK pin. This is designed to be the feedback resistor for the I/V op amp. This resistor is trimmed along with the rest of the resistors so it tracks. Also, since it is made of the same material as the rest of the resistors, therefore having the same temperature coefficient, and is on the same substrate, hence at the same temperature, it will track over temperature.

Figure 6-15 shows a more modern example of a CMOS DAC, the AD7394. Several trends are obvious here. First off all, the output is voltage, not current. Advancements in process technology have allowed reasonable quality CMOS op amps to be created. Also note the two ranks of latches. The purpose of these latches is to allow the microcontroller to write to all converters in a system and then update them all at the same time. This will be covered in more detail in a later section. Note also the power on reset circuit. Since the wake up state of a CMOS DAC is undefined and not repeatable, many modern DACs include a circuit to force the output to either half-scale of minimum scale, depending on whether the intended application is unipolar or bipolar. Probably the most obvious difference is that this is a multiple DAC package. Shrinking device geometries have allowed more circuitry to be included, even with the smaller packages in use today.

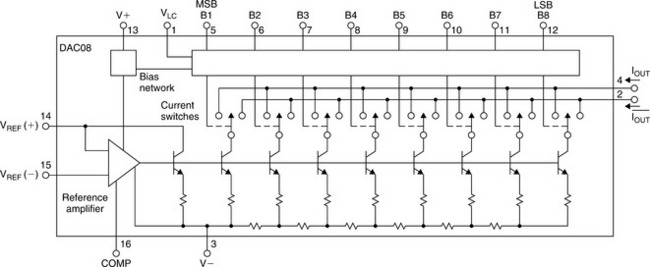

The previous examples were CMOS devices, that is to say that the switches were implemented with CMOS switches. The switches could also be implemented with bipolar junction transistors (BJT). An example of this is the classic DAC-08. Its block diagram is shown in Figure 6-16. One major difference in the BJT implementation is that the switch allows current in one direction, versus the CMOS switch, which can allow bidirectional current. This limits the BJT DAC to two-quadrant operation while the CMOS version can be four-quadrant. Supplies tend to be different as well.

There are two ways in which the R–2R ladder network may be used as a DAC—known respectively as the voltage mode and the current mode (they are sometimes called “normal” mode and “inverted” mode, but as there is no consensus on whether the voltage mode or the current mode is the “normal” mode for a ladder network this nomenclature can be misleading, although in most cases the current mode would be considered the “normal” mode). Each mode has its advantages and disadvantages.

In the current-mode R–2R ladder DAC shown in Figure 6-17, the gain of the DAC may be adjusted with a series resistor at the VREF terminal, since in the current mode, the end of the ladder, with its code-independent impedance, is used as the VREF terminal; and the ends of the arms are switched between ground and an output line which must be held at ground potential. The normal connection of a current-mode ladder network output is to an op amp’s inverting input (virtual ground), but stabilization of this op amp is complicated by the DAC output impedance variation with digital code.

Current-mode operation has a larger switching glitch than voltage mode since the switches connect directly to the output line(s). However, since the switches of a current-mode ladder network are always at ground potential, their design is less demanding and, in particular, their voltage rating does not affect the reference voltage rating. If switches capable of carrying current in either direction (such as CMOS devices) are used, the reference voltage may have either polarity, or may even be AC. Such a structure is one of the most common types used as a multiplying DAC (MDAC) which will be discussed later in this section.

Since the switches are always at, or very close to, ground potential, the maximum reference voltage may greatly exceed the logic voltage, provided the switches are make-before-break—which they are in this type of DAC. It is not unknown for a CMOS MDAC to accept a ± 30 V reference (or even a 60 V peak-to-peak AC reference) while working from a single 5 V supply.

In the voltage-mode R–2R ladder DAC shown in Figure 6-18, the “rungs” or arms of the ladder are switched between VREF and ground, and the output is taken from the end of the ladder. The output may be taken as a voltage, but the output impedance is independent of code, so it may equally well be taken as a current into a virtual ground.

The voltage output is an advantage of this mode, as is the constant output impedance, which eases the stabilization of any amplifier connected to the output node. Additionally, the switches switch the arms of the ladder between a low impedance VREF connection and ground, which is also, of course, low impedance, so capacitive glitch currents tend not to flow in the load. On the other hand, the switches must operate over a wide voltage range (VREF to ground), which is difficult from a design and manufacturing viewpoint, and the reference input impedance varies widely with code, so that the reference input must be driven from a very low impedance. In addition, the gain of the DAC cannot be adjusted by means of a resistor in series with the VREF terminal. Probably the most important advantage to the voltage mode is that it allows single-supply operation. This is because the op amp that is commonly used as I/V converter in the current-mode converter is in the inverting configuration so would require a negative output for a positive input, assuming ground reference. Of course you could bias everything up to a rail-splitter ground, but that introduces other issues into the system.

Multiplying DACs

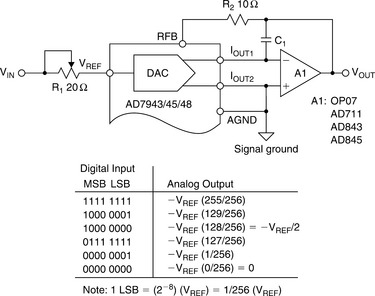

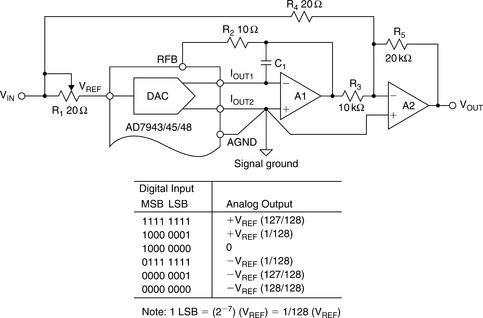

In most cases the reference to a DAC is a highly stable DC voltage. In some instances, however, it is useful to have a variable reference. The R–2R ladder structure using CMOS switches can easily handle a bipolar signal on its input. Having the ability to have bipolar (positive and negative) signals on the input allows construction of two-quadrant and four-quadrant MDACs. Figure 6-19 shows the schematic and the table in this figure outlines the operation of a two-quadrant MDAC, and Figure 6-20 shows the schematic and the table in this figure outlines the operation of a four-quadrant MDAC for an 8-bit DAC.

DACs utilizing BJTs as switches, such as the DAC-08 above, cannot accommodate bipolar signals on the reference. Therefore they can only implement two-quadrant MDACs. In addition, the reference voltage cannot go all the way to 0 V. The maximum allowable range is typically from 10% to 100% of the allowable reference voltage range.

One of the main applications of the MDAC is as a variable gain amplifier, where the gain is controlled by the digital word applied to the MDAC.

The frequency response of the MDAC is limited by the parasitic capacitance across the switches in the off condition. As the frequency goes up the impedance of the capacitors goes down, effectively bypassing the switch. This reduces the off isolation at higher frequencies. Typically the frequency response of an MDAC will be on the order of 1 MHz.

Segmented DACs

So far we have considered mostly basic DAC architectures. When we are required to design a DAC with a specific performance, it may well be that no single architecture is ideal. In such cases, two or more DACs may be combined in a single higher resolution DAC to give the required performance. These DACs may be of the same type or of different types and need not each have the same resolution. For example, the segmented string DAC is a segmented DAC where 2 Kelvin DACs are cascaded.

Typically, one DAC handles the MSBs, another handles the LSBs, and their outputs are added in some way. The process is known as “segmentation,” and these more complex structures are called “segmented DACs.” There are many different types of segmented DACs and some, but by no means all, of them will be illustrated in the next few diagrams. It is sometimes not obvious from looking at the data sheet that a particular DAC is segmented.

Very high speed DACs for video, communications, and other high frequency reconstruction applications are often built with arrays of fully decoded current sources. The 2 or 3 LSBs may use binary-weighted current sources. It is extremely important that such DACs have low distortion at high frequency, and there are several important issues to be considered in their design.

Two examples of segmented current-output DAC structures are shown in Figure 6-21. Figure 6-21(A) shows a resistor-based approach for the 7-bit DAC where the 3 MSBs are fully decoded, and the 4 LSBs are derived from an R–2R network. Figure 6-21(B) shows a similar implementation using current sources. The current source implementation is by far the most popular for today’s high speed reconstruction DACs.

It is also often desirable to utilize more than one fully decoded thermometer section to make up the total DAC. Figure 6-22 shows a 6-bit DAC constructed from two fully decoded 3-bit DACs. As previously discussed, these current switches must be driven simultaneously from parallel latches in order to minimize the output glitch.

The AD9775 14-bit, 160 MSPS (input)/400 MSPS (output) TxDAC™ uses three sections of segmentation as shown in Figure 6-23. Other members of the AD977x-family and the AD985x-family also use this same basic core.

The first 5 bits (MSBs) are fully decoded and drive 31 equally weighted current switches, each supplying 512 LSBs of current. The next 4 bits are decoded into 15 lines which drive 15 current switches, each supplying 32 LSBs of current. The 5 LSBs are latched and drive a traditional binary-weighted DAC which supplies 1 LSB per output level. A total of 51 current switches and latches are required to implement this ultra low glitch architecture.

Decoding must be done before the new data is applied to the DAC so that all the data is ready and can be applied simultaneously to all the switches in the DAC. This is generally implemented by using a separate parallel latch for the individual switches in fully decoded array. If all switches were to change state instantaneously and simultaneously there would be no skew glitch—by very careful design of propagation delays around the chip and time constants of switch resistance and stray capacitance the update synchronization can be made very good, and hence the glitch-related distortion is very small.

I/V Converters

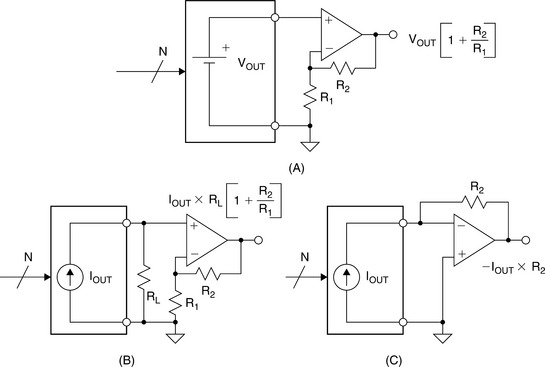

Modern IC DACs provide either voltage or current outputs. Figure 6-24 below shows three fundamental configurations, all with the objective of using an op amp for a buffered output voltage.

Figure 6-24(A) shows a buffered voltage-output DAC. In many cases, the DAC output can be used directly, without additional buffering. If an additional op amp is needed, it is usually configured in a non-inverting mode, with gain determined by R1 and R2.

There are two basic methods for dealing with a current-output DAC.

A direct method to convert the output current into a voltage is shown in Figure 6-24(C). This circuit is usually called a current-to-voltage converter, or I/V. In this circuit, the DAC output drives the inverting input of an op amp, with the output voltage developed across the R2 feedback resistor. In this approach the DAC output always operates at virtual ground (which may give a linearity improvement vis-à-vis Figure. 6-24(B)).

In Figure 6-24(B) a voltage is simply developed across external load resistor, RL. This is typically done with high speed op amps. An external op amp can be used to buffer and/or amplify this voltage if required. The output current is dumped into a resistor instead of into an op amp directly since the fast edges may exceed the slew rate of the amplifier and cause distortion. Many DACs supply full-scale currents of 20 mA or more, thereby allowing reasonable voltages to be developed across fairly low value load resistors. For instance, fast settling video DACs typically supply nearly 30 mA full-scale current, allowing 1 V to be developed across a source and load terminated 75 Ω coaxial cable (representing a DC load of 37.5 Ω to the DAC output).

The general selection process for an op amp used as a DAC buffer is that the performance of the op amp should not compromise the performance of the DAC. The basic specifications of interest are DC accuracy, noise, settling time, bandwidth, distortion, etc.

Differential to Single-Ended Conversion Techniques

A general model of a modern current-output DAC is shown in Figure 6-25. This model is typical of the AD976X and AD977X TxDAC™ series (see Reference 1).

Current output is more popular than voltage output, especially at audio frequencies and above. If the DAC is fabricated on a bipolar or BiCMOS process, it is likely that the output will sink current, and that the output impedance will be less than 500 Ω (due to the internal R–2R resistive ladder network). On the other hand, a CMOS DAC is more likely to source output current and have a high output impedance, typically greater than 100 kΩ.

Another consideration is the output compliance voltage—the maximum voltage swing allowed at the output in order for the DAC to maintain its linearity. This voltage is typically 1–1.5 V, but will vary depending on the DAC. Best DAC linearity is generally achieved when driving a virtual ground, such as an op amp I/V converter. Modern current-output DACs usually have differential outputs, to achieve high CM rejection and reduce the even-order distortion products. Full-scale output currents in the range of 2–20 mA are common.

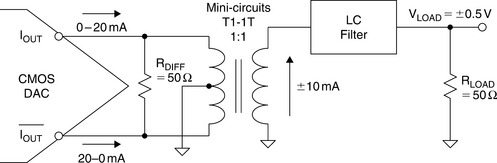

In most applications, it is desirable to convert the differential output of the DAC into a single-ended signal, suitable for driving a coax line. This can be readily achieved with a radio frequency (RF) transformer, provided low frequency response is not required. Figure 6-26 shows a typical example of this approach. The high impedance current-output of the DAC is terminated differentially with 50 Ω, which defines the source impedance to the transformer as 50 Ω.

The resulting differential voltage drives the primary of a 1:1 RF transformer, to develop a single-ended voltage at the output of the secondary winding. The output of the 50 Ω LC filter is matched with the 50 Ω load resistor RL, and a final output voltage of 1 Vp-p is developed.

The transformer not only serves to convert the differential output into a single-ended signal, but it also isolates the output of the DAC from the reactive load presented by the LC filter, thereby improving overall distortion performance.

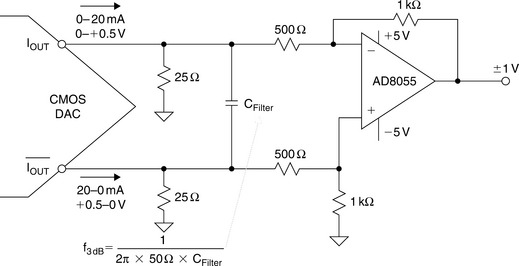

An op amp connected as a differential to single-ended converter can be used to obtain a single-ended output when frequency response to DC is required. In Figure 6-28 the AD8055 op amp is used to achieve high bandwidth and low distortion (see Reference 2). The current-output DAC drives balanced 25 Ω resistive loads, thereby developing an out of phase voltage of 0 V to +0.5 V at each output. The AD8055 is configured for a gain of 8, to develop a final single-ended ground-referenced output voltage of 2 Vp-p. Note that because the output signal swings above and below ground, a dual-supply op amp is required (Figure 6-27).

The CFILTER capacitor forms a differential filter with the equivalent 50 Ω differential output impedance. This filter reduces any slew induced distortion of the op amp, and the optimum cutoff frequency of the filter is determined empirically to give the best overall distortion performance.

A modified form of Figure 6-26 circuit can also be operated on a single supply, provided the CM voltage of the op amp is set to mid-supply (+2.5 V). This is shown in Figure 6-28. The output voltage is 2 Vp-p centered around a CM voltage of +2.5 V. This CM voltage can be either developed from the + 5 V supply using a resistor divider, or directly from a +2.5 V voltage reference. If the +5 V supply is used as the CM voltage, it must be heavily decoupled to prevent supply noise from being amplified.

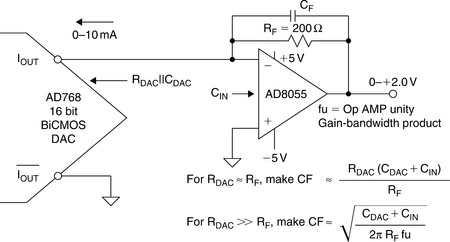

Single-Ended Current-to-Voltage Conversion

Single-ended current-to-voltage conversion is easily performed using a single op amp as an I/V converter, as shown in Figure 6-29. The 10 mA full-scale DAC current from the AD768 (see Reference 3) develops a 0 V to +2 V output voltage across the 200 Ω RF.

Driving the virtual ground of the AD8055 op amp minimizes any distortion due to nonlinearity in the DAC output impedance. In fact, most high resolution DACs of this type are factory trimmed using an I/V converter.

It should be recalled, however, that using the single-ended output of the DAC in this manner will cause degradation in the CM rejection and increased second-order distortion products, compared to a differential operating mode.

The CF feedback capacitor should be optimized for best pulse response in the circuit. The equations given in the diagram should only be used as guidelines. A more detailed analysis of this circuit is given in the References.

Differential Current-to-Differential Voltage Conversion

If a buffered differential voltage output is required from a current-output DAC, the AD813X-series of differential amplifiers can be used as shown in Figure 6-30.

The DAC output current is first converted into a voltage that is developed across the 25 Ω resistors. The voltage is amplified by a factor of five using the AD813X. This technique is used in lieu of a direct I/V conversion to prevent fast slewing DAC currents from overloading the amplifier and introducing distortion. Care must be taken so that the DAC output voltage is within its compliance rating.

The VOCM input on the AD813X can be used to set a final output CM voltage within the range of the AD813X. If transmission lines are to be driven at the output, adding a pair of 75 Ω resistors will allow this.

Digital Interfaces

The earliest monolithic DACs contained little, if any, logic circuitry, and parallel data had to be maintained on the digital input to maintain the digital output. Today almost all DACs are latched and data need only be written to them, not maintained. Some even have nonvolatile latches and remember settings while turned off.

There are innumerable variations of DAC digital input structure, which will not be discussed here, but nearly all are described as “double-buffered.” A double-buffered DAC has two sets of latches. Data is initially latched in the first rank and subsequently transferred to the second as shown in Figure 6-31. There are two reasons why this arrangement is useful.

The first is that it allows data to enter the DAC in many different ways. A DAC without a latch, or with a single latch, must be loaded in parallel with all bits at once, since otherwise its output during loading may be totally different from what it was or what it is to become. A double-buffered DAC, on the other hand, may be loaded with parallel data, or with serial data, or with 4-bit or 8-bit words, or whatever, and the output will be unaffected until the new data is completely loaded and the DAC receives its update instruction.

The other convenience of the double-buffered structure is that many DACs may be updated simultaneously: data is loaded into the first rank of each DAC in turn, and when all is ready, the output buffers of all the DACs are updated at once. There are many DAC applications where the output of a number of DACs must change simultaneously, and the double-buffered structure allows this to be done very easily.

Most early monolithic high resolution DACs had parallel or byte-wide data ports and tended to be connected to parallel data buses and address decoders and addressed by microprocessors as if they were very small write-only memories. (Some parallel DACs are not write-only, but can have their contents read as well—this is convenient for some applications, but is not very common.) A DAC connected to a data bus is vulnerable to capacitive coupling of logic noise from the bus to the analog output. Serial interfaces are less vulnerable to such noise (since fewer noisy pins are involved), use fewer pins and therefore take less board space, and are frequently more convenient for use with modern microprocessors, most of which have serial data ports. Some, but not all, of such serial DACs have data outputs as well as data inputs so that several DACs may be connected in series and data clocked to them all from a single serial port. This arrangement is often referred to as “daisy-chaining.”

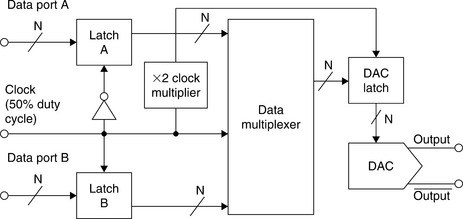

Of course, serial DACs cannot be used where high update rates are involved, since the clock rate of the serial data would be too high. Some very high speed DACs actually have two parallel data ports and use them alternately in a multiplexed fashion (sometimes this is called a “ping-pong” input) to reduce the data rate on each port as shown in Figure 6-32. The alternate loading (ping-pong) DAC in the diagram loads from port A and port B alternately on the rising and falling edges of the clock, which must have a mark-space ratio close to 50:50. The internal clock multiplier ensures that the DAC itself is updated with data A and data B alternately at exactly 50:50 time ratio, even if the external clock is not so precise.

Historically IC logic circuitry (with the exception of emitter coupled logic or ECL) operated from 5 V supplies and had compatible logic levels—with a few exceptions 5 V logic would interface with other 5 V logic. Today, with the advent of low voltage logic operating with supplies of 3.3 V, 2.7 V or even less, it is important to ensure that logic interfaces are compatible. There are several issues which must be considered—absolute maximum ratings, worst case logic levels, and timing. The logic inputs of ICs generally have absolute maximum ratings, as do most other inputs, of 300 mV outside the power supply.

Note that these are instantaneous ratings. If an IC has such a rating and is currently operating from a +5 V supply then the logic inputs may be between −0.3 and +5.3 V—but if the supply is not present then that input must be between +0.3 V and −0.3 V not the −0.3 V to +5.3 V which are the limits once the power is applied—ICs cannot predict the future.

The reason for the rating of 0.3 V is to ensure that no parasitic diode inside the IC is ever turned on by a voltage outside the IC’s absolute maximum rating. It is quite common to protect an input from such overvoltage with a Schottky diode clamp. At low temperatures the clamp voltage of a Schottky diode may be a little more than 0.3 V, and so the IC may see voltages just outside its absolute maximum rating. Although, strictly speaking, this subjects the IC to stresses outside its absolute maximum ratings and so is forbidden, this is an acceptable exception to the general rule provided the Schottky diode is at a similar temperature to the IC that it is protecting (say within ± 10°C).

Some low voltage devices, however, have inputs with absolute maximum ratings which are substantially greater than their supply voltage. This allows such circuits to be driven by higher voltage logic without additional interface or clamp circuitry. But it is important to read the data sheets and ensure that both logic levels and absolute maximum voltages are compatible for all combinations of high and low supplies.

This is the general rule when interfacing different low voltage logic circuitry—it is always necessary to check both that at the lowest value of its power supply the logic 1 output from the driving circuit applied to its worst case load is greater than the specified minimum logic 1 input for the receiving circuit, and that, again with its lowest value of power supply and with its output sinking maximum allowed current, the logic 0 output is less than the specified logic 0 input of the receiver. If the logic specifications of your chosen devices do not meet these criteria it will be necessary to select different devices, use different power supplies, or use additional interface circuitry to ensure that the required levels are available. Note that additional interface circuitry will introduce extra delays in timing.

It is not sufficient to build an experimental set-up and test it. In general, logic thresholds are generously specified and usually logic circuits will work correctly well outside their specified limits—but it is not possible to rely on this in a production design. At some point a batch of devices near the limit on low output swing will be required to drive some devices needing slightly more drive than usual—and will be unable to do so.

One of the latest developments in high speed logic interface is low voltage differential signaling (LVDS). LVDS presents a solution to the high speed converter interface problem by mitigating the effects of CMOS single-ended interfaces and accommodating higher data rates. The LVDS standard specifies a p-p voltage swing of 350 mV around a common-mode voltage (CMV) of 1.2 V, which facilitates transmission of high speed differential digital signals with balanced current, thereby reducing the slew rate requirement. Reducing the slew rate eliminates the gradients that result in noise from ground bounce that are present in conventional CMOS drivers. Ground-bounce noise can couple back into sensitive analog circuits and degrade the converter’s dynamic range. Parallel LVDS interfaces enable much higher data rates and optimum dynamic performance, in high speed data converters.

LVDS also offers some benefit in reduced electromagnetic interference (EMI). The EMI fields generated by the opposing currents will tend to cancel each other (for matched edge rates). Trace length, skew, and discontinuities will reduce this benefit and should be avoided.

LVDS also offers simpler timing constraints compared to a demuxed CMOS solution at similar data rates. A demuxed databus requires a synchronization signal that is not required in LVDS. In demuxed CMOS buses, a clock equal to one-half the ADC sample rate is needed, adding cost and complexity, that is not required in LVDS. In general, the LVDS is more forgiving and can lead to a simpler, cleaner design.

The LVDS specification (IEEE Standard 1596.3) was developed as an extension to the 1992 SCI protocol (IEEE Standard 1596-1992). The original SCI protocol was suitable for high speed packet transmissions in high end computing and used ECL levels. However, for low end and power-sensitive applications, a new standard was needed. LVDS signals were chosen because the voltage swing is smaller than that of ECL outputs, allowing for lower power supplies in power-sensitive designs.

Unlike CMOS, which is typically a voltage output, LVDS is a current-output technology. LVDS outputs for high performance converters should be treated differently than standard LVDS outputs used in digital logic (Figure 6-33). While standard LVDS can drive 1–10 m in high speed digital applications (dependent on data rate), it is not recommended to let high performance converters drive that distance. It is recommended to keep the output trace lengths short (<2 inches), minimizing the opportunity for any noise coupling onto the outputs from the adjacent circuitry, which may get back to the analog outputs.

The differential output traces should be routed close together, maximizing common-mode rejection (CMR) with the 100 Ω termination resistor close to the receiver. Users should pay attention to printed circuit board (PCB) trace lengths to minimize any delay skew.

A typical differential microstrip PCB trace cross section is shown in Figure 6-34.

Power supply decoupling is very important with these fast (<0.5 ns) edge rates. A low inductance, surface mount capacitor should be placed at every power supply and ground pin as close to the converter as possible. Placing the decoupling caps on the other side of the PCB is not recommended, since the via inductance will reduce the effective decoupling. The differential ZO will tend to be slightly lower than twice the single-ended ZO of each conductor due to proximity effects—the ZO of each line should be designed to be slightly higher than 50 Ω. Simulation can be used in critical applications to verify impedance matching. In short runs, this should not be critical.

Data Converter Logic: Timing and Other Issues

It is not the purpose of this brief section to discuss logic architectures, so we shall not define the many different data converter logic interface operations and their timing specifications except to note that data converter logic interfaces may be more complex than you expect—do not expect that because there is a pin with the same name on memory and interface chips it will behave in exactly the same way in a data converter. Unfortunately, there is not a standard nomenclature for pin functionality, even for the same manufacturer. The data sheet should always be consulted to determine the operation of all control pins. Also some data converters reset to a known state on power-up but many more do not.

But it is very necessary to consider general timing issues. The new low voltage processes which are used for many modern data converters have a number of desirable features. One which is often overlooked by users (but not by converter designers!) is their higher logic speed. DACs built on older processes frequently had logic which was orders of magnitude slower than the microprocessors that they interfaced with and it was sometimes necessary to use separate buffers, or multiple WAIT instructions, to make the two compatible. Today it is much more common for the write times of DACs to be compatible with those of the fast logic with which they interface.

Nevertheless not all DACs are speed compatible with all logic interfaces and it is still important to ensure that minimum data set-up times and write pulse widths are observed. Again, experiments will often show that devices work with faster signals than their specification requires—but at the limits of temperature or supply voltage some may not and interfaces should be designed on the basis of specified rather than measured timing.

Interpolating DACs (Interpolating TxDACs)

The concept of oversampling, to be discussed in another section (on sampling theory), can be applied on high speed DACs typically used in communications applications. Oversampling relaxes the requirements on the output filter as well as increasing the SNR due to process gain.

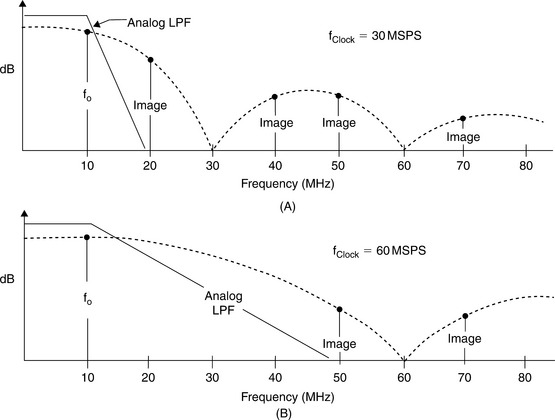

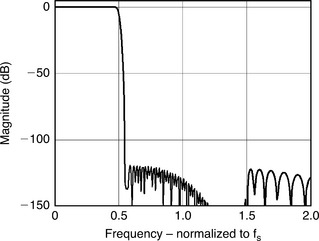

Assume a traditional DAC is driven at an input word rate of 30 MSPS (see Figure 6-35(A)). Assume the DAC output frequency is 10 MHz. The image frequency component at 30–10 = 20 MHz must be attenuated by the analog reconstruction filter, and the transition band of the filter is therefore 10–20 MHz. Assume that the image frequency must be attenuated by 60 dB. The filter must therefore go from a passband of 10 MHz to 60 dB stopband attenuation over the transition band lying between 10 and 20 MHz (one octave). Filter gives 6 dB attenuation per octave for each pole. Therefore, a minimum of 10 poles is required to provide the desired attenuation. This is a fairly aggressive filter and would involve high Q sections which would be difficult to align and manufacture. Filters become even more complex as the transition band becomes narrower.

Assume that we increase the DAC update rate to 60 MSPS and insert a “zero” between each original data sample. The parallel data stream is now 60 MSPS, but we must now determine the value of the zero-value data points. This is done by passing the 60 MSPS data stream with the added zeros through a digital interpolation filter which computes the additional data points. The response of the digital filter relative to the 2-times oversampling frequency is shown in Figure 6-35(B). The analog antialiasing filter transition zone is now 10–50 MHz (the first image occurs at 2fc − fo = 60−10 = 50 MHz). This transition zone is a little greater than 2 octaves, implying that a 5- or 6-pole Butterworth filter is sufficient.

The AD9773/AD9775/AD9777 (12/14/16-bit) series of Transmit DACs (TxDAC™) are selectable 2 times, 4 times, or 8 times oversampling interpolating dual DACs, and a simplified block diagram is shown in Figure 6-36. These devices are designed to handle 12/14/16-bit input word rates up to 160 MSPS. The output word rate is 400 MSPS maximum. For an output frequency of 50 MHz, an input update rate of 160 MHz, and an oversampling ratio of 2 times, the image frequency occurs at 320 MHz −50 MHz = 270 MHz. The transition band for the analog filter is therefore 50–270 MHz. Without 2 times oversampling, the image frequency occurs at 160 MHz −50 MHz = 110 MHz, and the filter transition band is 60–110 MHz.

Reconstruction Filters

The output of a DAC is not a continuously varying waveform, but instead a series of DC levels. This output must be passed through a filter to remove the high frequency components and smooth waveform into a more truly analog waveform.

The concept of filtering is discussed in more detail in Chapter 8.

In general, to preserve spectral purity, the images of the DAC output must be attenuated below the resolution of DAC. To use the example sited above, we assume that the DAC output passband is 10 MHz. The sample rate is 30 MHz. Therefore the image of the passband that must be attenuated is 30 MHz −10 MHz = 20 MHz. This is the sample rate minus the passband frequency. The DAC in this example is a 10-bit device, which would indicate a distortion level of −60 dB. So a reconstruction filter should reduce the image by 60 dB while not attenuating the fundamental at all. Since a filter attenuates at 6 dB/pole, this would indicate that a tenth-order filter would be required.

There are several other considerations that must be taken into account.

First is that most filter cutoffs are measured at the −3 dB point. Therefore, if we do not want the fundamental attenuated, some margin in the filter is required. The graphs in the filter section will help illustrate this point. This will cause the transition band to become narrower and thus the order of the filter to increase.

Sin(x)/(x)(Sinc)

The output of a DAC is not a continually varying waveform but instead a series of DC levels. The DAC puts out a DC level until it is told to put out a new level. This is illustrated in Figure 6-37.

The width of the pulses is 1/FS. The spectrum of each pulse is the sin(x)/x curve. This is also known as the sinc curve. This response is added to the response of the reconstruction filter to provide the overall response of the converter. This will cause an amplitude error as the output frequency approaches the Nyquist frequency (FS/2). The value of the sinc function is shown in Figure 6-38. Some high speed DACs incorporate an inverse filter (in the digital domain) to compensate for this rolloff.

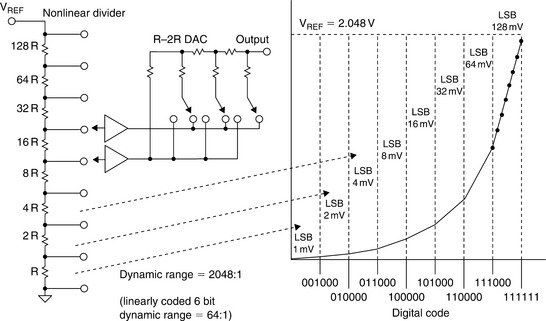

Intentionally Nonlinear DACs

Thus far, we have emphasized the importance of maintaining good differential and integral linearity. However, there are situations where ADCs and DACs which have been made intentionally nonlinear (but maintaining good differential linearity) are useful, especially when processing signals having a wide dynamic range. One of the earliest uses of nonlinear data converters was in the digitization of voiceband signals for pulse code modulation (PCM) systems. Major contributions were made at Bell Labs during the development of the T1 carrier system. The motive for the nonlinear ADCs and DACs was to reduce the total number of bits (and therefore the serial transmission rate) required to digitize voice channels. Straight linear encoding of a voice channel required 11 or 12 bits at an 8 kSPS per channel sampling rate. In the 1960s Bell Labs determined that 7-bit nonlinear encoding was sufficient, and later in the 1970s went to 8-bit nonlinear encoding for better performance.

The nonlinear transfer function allocates more quantization levels out of the total range for small signals and fewer for large amplitude signals. In effect, this reduces the quantization noise associated with small signals (where it is most noticeable) and increases the quantization noise for larger signals (where it is less noticeable). The term companding is generally used to describe this form of encoding.

The logarithmic transfer function chosen is referred to as the “Bell μ-255” standard, or simply “μ-law.” A similar standard developed in Europe is referred to as “A-law.” The Bell μ-law allows a dynamic range of about 4,000:1 using 8 bits, whereas an 8-bit linear data converter provides a range of only 256:1.

The first generation channel bank (D1) used temperature-controlled resistor-diode networks for “compressors” ahead of a 7-bit linear ADC in the transmitter to generate the logarithmic transfer function. Corresponding resistor-diode “expandors” having an inverse transfer function followed the 7-bit linear DAC in the receiver. The next generation D2 channel banks used nonlinear ADCs and DACs to accomplish the compression/expansion functions in a much more reliable and cost-effective manner and eliminated the need for the temperature-controlled diode networks.

In his 1953 classic paper, B.D. Smith proposed that the transfer function of a successive approximation ADC utilizing a nonlinear internal DAC in the feedback path would be the inverse transfer function of the DAC (Reference 8). The same basic DAC could therefore be used in the ADC and also for the reconstruction DAC. Later in the 1960s and early 1970s, nonlinear ADC and DAC technology using piecewise linear approximations of the desired transfer function allowed low cost high volume implementations (References 18–23). These nonlinear 8-bit, 8-kSPS data converters became popular telecommunications building blocks.

The nonlinear transfer function of the 8-bit DAC is first divided into 16 segments (chords) of different slopes—the slopes are determined by the desired nonlinear transfer function. The 4 MSBs determine the segment containing the desired data point, and the individual segment is further subdivided into 16 equal quantization levels by the 4 LSBs of the 8-bit word. This is shown in Figure 6-39 for a 6-bit DAC, where the first 3 bits identify one of the 8 possible chords, and each chord is further subdivided into 8 equal levels defined by the 3 LSBs. The 3 MSBs are generated using a nonlinear string DAC, and the 3 LSBs are generated using a 3-bit binary R–2R DAC.

In 1982, Analog Devices introduced the LOGDAC™ AD7111 monolithic MDAC featuring wide dynamic range using a logarithmic transfer function. The basic DAC in the LOGDAC is a linear 17-bit voltage-mode R–2R DAC preceded by an 8-bit input decoder (a functional diagram of the LOGDAC is shown in Figure 6-40). The LOGDAC can attenuate an analog input signal, VIN, over the range 0–88.5 dB in 0.375 dB steps. The degree of attenuation across the DAC is determined by a nonlinear-coded 8-bit word applied to the onboard decode logic. This 8-bit word is mapped into the appropriate 17-bit word which is then applied to a 17-bit, R–2R ladder. In addition to providing the logarithmic transfer function, the LOGDAC also acts as a full four-quadrant MDAC.

With the introduction of high resolution linear ADCs and DACs, the method used in the LOGDAC™ is widely used today to implement various nonlinear transfer functions such as the μ-law and A-law companding functions required for telecommunications and other applications. Figure 6-41 shows a general block diagram of the modern approach. The μ-law or A-law companded input data is mapped into data points on the transfer function of a high resolution DAC. This mapping can be easily accomplished by a simple lookup table in either hardware, software, or firmware. A similar nonlinear ADC can be constructed by digitizing the analog input signal using a high resolution ADC and mapping the data points into a shorter word using the appropriate transfer function. A big advantage of this method is that the transfer curve does not have to be approximated with straight line segments as in the earlier method, thereby providing more accuracy.

SECTION 6-2 ADC Architectures

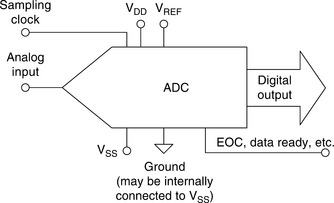

The basic ADC function is shown in Figure 6-42. This could also be referred to as a quantizer. Most ADC chips also include some of the support circuitry, such as clock oscillator for the sampling clock, reference (REF), the SHA function, and output data latches. In addition to these basic functions, some ADCs have additional circuitry built in. These functions could include multiplexers, sequencers, auto-calibration circuits, programmable gain amplifiers (PGAs), etc.

Similar to DACs, some ADCs use external references and have a reference input terminal, while others have an output from an internal reference. In some instances the ADC may have an internal reference that is pinned out through a resistor. This connection allows the reference to be filtered (using the internal R and an external C) or by allowing the internal reference to be overdriven by an external reference. The AD789X family of parts are examples of ADC that use this type of connection. The simplest ADCs, of course, have neither—the reference is on the ADC chip and has no external connections.

If an ADC has an internal reference, its overall accuracy is specified when using that reference. If such an ADC is used with a perfectly accurate external reference, its absolute accuracy may actually be worse than when it is operated with its own internal reference. This is because it is trimmed for absolute accuracy when working with its own actual reference voltage, not with the nominal value. Twenty years ago it was common for converter references to have accuracies as poor as ±5% since these references were trimmed for low temperature coefficient rather than absolute accuracy, and the inaccuracy of the reference was compensated in the gain trim of the ADC itself. Today the problem is much less severe, but it is still important to check for possible loss of absolute accuracy when using an external reference with an ADC which has a built-in one.

ADCs which have reference terminals must, of course, specify their behavior and parameters. If there is a reference input the first specification will be the reference input voltage—and of course this has two values, the absolute maximum rating, and the range of voltages over which the ADC performs correctly.

Most ADCs require that their reference voltage is within quite a narrow range whose maximum value is less than or equal to the ADC’s VDD.

The reference input terminal of an ADC may be buffered as shown in Figure 6-43, in which case it has input impedance (usually high) and bias current (usually low) specifications, or it may connect directly to the ADC. In either case, the transient currents developed on the reference input due to the internal conversion process need good decoupling with external low inductance capacitors. Good ADC data sheets recommend appropriate decoupling networks.

The reference output may be buffered or unbuffered. If it is buffered, the maximum output current will probably be specified. In general such a buffer will have a unidirectional output stage which sources current but does not allow current to flow into the output terminal. If the buffer does have a push–pull output stage (not as common), the output current will probably be defined as ± (some value) mA. If the reference output is unbuffered, the output impedance may be specified, or the data sheet may simply advise the use of a high input impedance external buffer.

There are some instances where the power supply is the reference. In these cases it is imperative to make sure the power supply is clean.

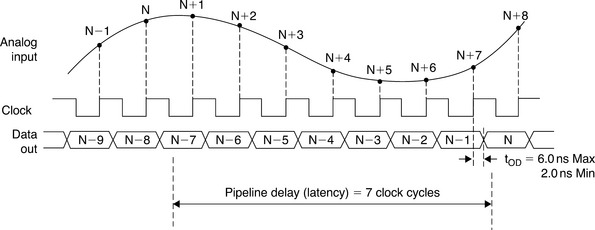

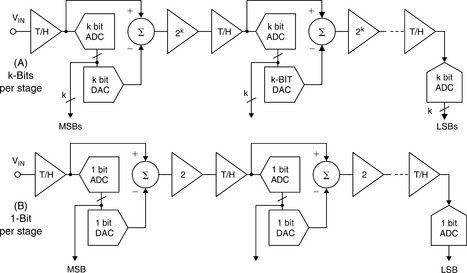

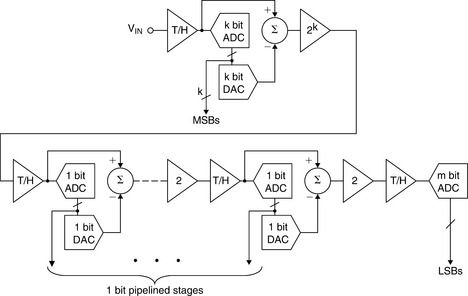

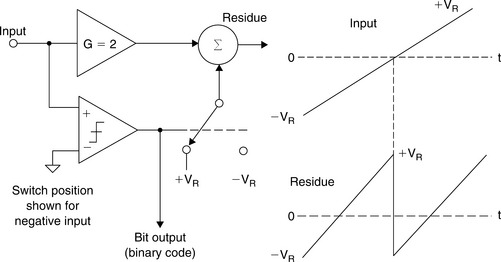

The sampling clock input is a critical function in an ADC and a source of some confusion. It could truly be the sampling clock. This frequency would typically be several times higher than the sampling rate of the converter. It could also be a convert start (or encode) command which would happen once per conversion. Pipeline architecture devices and sigma–delta (ΣΔ) converters are continuously converting and have no convert start command.

Regardless of the ADC, it is extremely important to read the data sheet and determine exactly what the external clock requirements are, because they can vary widely from one ADC to another.

At some point after the assertion of the sampling clock, the output data is valid. This data may be in parallel or serial format depending on the ADC. Early successive approximation ADCs such as the AD574 simply provided a STATUS output (STS) which went high during the conversion, and returned to the low state when the output data was valid. In other ADCs, this line is variously called busy, end-of-conversion (EOC), data ready (DRDY), etc. Regardless of the ADC, there must be some method of knowing when the output data is valid—and again, the data sheet is where this information can always be found.

Another detail which can cause trouble is the difference between EOC and DRDY. EOC indicates that conversion has finished, DRDY that data is available at the output. In some ADCs, EOC functions as DRDY—in others, data is not valid until several tenths of nanoseconds after the EOC has become valid, and if EOC is used as a data strobe, the results will be unreliable.

There are one or two other practical points which are worth remembering about the logic of ADCs. On power-up, many ADCs do not have logic reset circuitry and may enter an anomalous logical state. Several conversions may be necessary to restore their logic to proper operation so: (a) the first few conversions after power-up should never be trusted, and (b) control outputs (EOC, DRDY, etc.) may behave in unexpected ways at this time (and not necessarily in the same way at each power-up), and (c) care should be taken to ensure that such anomalous behavior cannot cause system latch-up. For example, EOC should not be used to initiate conversion if there is any possibility that EOC will not occur until the first conversion has taken place, as otherwise initiation will never occur.

Some low power ADCs now have power-saving modes of operation variously called standby, power-down, sleep, etc. When an ADC comes out of one of these low power modes, there is a certain recovery time required before the ADC can operate at its full specified performance. The data sheet should therefore be carefully studied when using these modes of operation.

As a final example, some ADCs use CS (chip select) edges to reset internal logic, and it may not be possible to perform another conversion without asserting or reasserting CS (or it may not be possible to read the same data twice, or both).

For more detail, it is important to read the whole data sheet before using an ADC since there are innumerable small logic variations from type to type. Unfortunately, many data sheets are not as clear as one might wish, so it is also important to understand the general principles of ADCs in order to interpret data sheets correctly. That is one of the purposes of this section.

There are a couple of general trend in ADCs that should be addressed. The first is the general trend toward lower supply voltages. This is partially due to the processes, particularly CMOS, which are used to manufacture the chips. Increasing demand for speed has driven the feature size of the processes down. This typically results in lower breakdown voltages for the transistors. This, in turn, requires lower supply voltages. Very few new parts are developed with the legacy ± 15 V supplies and ± 10 V input range.

Since the input signal range of the ADCs is shrinking, there is also a trend toward differential inputs. This helps improve the dynamic range of a converter, typically by 6 dB. There could be even further improvement since the common-mode ground-referenced noise is rejected. In many cases the differential input can be driven single endedly (with the resultant reduction of SNR). Occasionally the REF input might also be differential.

The Comparator: A 1-Bit ADC

A comparator is a 1-bit ADC (see Figure 6-44). If the input is above a threshold, the output has one logic value, below it has another. There is no ADC architecture which does not use at least one comparator of some sort. So while a 1-bit ADC is of very limited usefulness it is a building block for other architectures.

Comparators used as building blocks in ADCs need good resolution which implies high gain. This can lead to uncontrolled oscillation when the differential input approaches zero. In order to prevent this, hysteresis is often added to comparators using a small amount of positive feedback. Figure 6-44 shows the effects of hysteresis on the overall transfer function. Many comparators have a millivolt or two of hysteresis to encourage “snap” action and to prevent local feedback from causing instability in the transition region. Note that the resolution of the comparator can be no less than the hysteresis, so large values of hysteresis are generally not useful.

Successive Approximation ADCs

The successive approximation ADC has been the mainstay of data acquisition for many years. Recent design improvements have extended the sampling frequency of these ADCs into the megahertz region.

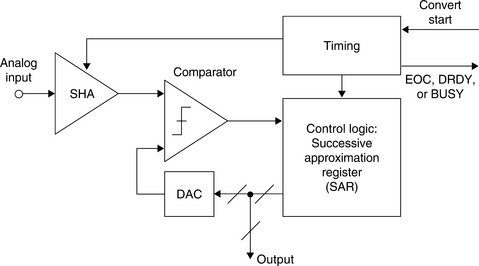

The basic successive approximation ADC is shown in Figure 6-45. It performs conversions on command. On the assertion of the CONVERT START command, the SHA is placed in the hold mode, and all the bits of the successive approximation register (SAR) are reset to “0” except the MSB which is set to “1.” The SAR output drives the internal DAC. If the DAC output is greater than the analog input, this bit in the SAR is reset, otherwise it is left set. The next MSB is then set to “1.” If the DAC output is greater than the analog input, this bit in the SAR is reset, otherwise it is left set. The process is repeated with each bit in turn. When all the bits have been set, tested, and reset or not as appropriate, the contents of the SAR correspond to the value of the analog input, and the conversion is complete. These bit “tests” can form the basis of a serial output version SAR-based ADC.

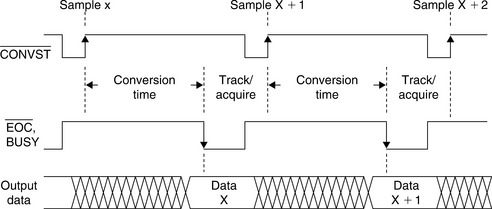

The fundamental timing diagram for a typical SAR ADC is shown in Figure 6-46. The EOC is generally indicated by an EOC, DRDY, or a busy signal (actually, not-BUSY indicates EOC). The polarities and name of this signal may be different for different SAR ADCs, but the fundamental concept is the same. At the beginning of the conversion interval, the signal goes high (or low) and remains in that state until the conversion is completed, at which time it goes low (or high). The trailing edge is generally an indication of valid output data, but the data sheet should be carefully studied—in some ADCs additional delay is required before the output data is valid.

An N-bit conversion takes N steps. It would seem on superficial examination that a 16-bit converter would have twice the conversion time of an 8-bit one, but this is not the case. In an 8-bit converter, the DAC must settle to 8-bit accuracy before the bit decision is made, whereas in a 16-bit converter, it must settle to 16-bit accuracy, which takes a lot longer. In practice, 8-bit successive approximation ADCs can convert in a few hundred nanoseconds, while 16-bit ones will generally take several microseconds.

While there are some variations, the fundamental timing of most SAR ADCs is similar and relatively straightforward. The conversion process is initiated by asserting a CONVERT START signal. This signal is typically named something like ![]() or CS. This signal is usually a negative-going pulse whose positive-going edge actually initiates the conversion. The internal SHA is placed in the hold mode on this edge, and the various bits are determined using the SAR algorithm. The negative-going edge of the

or CS. This signal is usually a negative-going pulse whose positive-going edge actually initiates the conversion. The internal SHA is placed in the hold mode on this edge, and the various bits are determined using the SAR algorithm. The negative-going edge of the ![]() pulse causes a signal typically called

pulse causes a signal typically called ![]() or BUSY to go high. When the conversion is complete, the BUSY line goes low (or

or BUSY to go high. When the conversion is complete, the BUSY line goes low (or ![]() goes high), indicating the completion of the conversion process. In most cases the trailing edge of the BUSY line can be used as an indication that the output data is valid and can be used to strobe the output data into an external register.

goes high), indicating the completion of the conversion process. In most cases the trailing edge of the BUSY line can be used as an indication that the output data is valid and can be used to strobe the output data into an external register.

There may also be other control lines. And sometimes control lines have dual function. This is primarily done when the chip is pin limited. Because of the many variations in terminology and design, the individual data sheet should always be consulted when using a specific ADC.

It should also be noted that some SAR ADCs require an external high frequency clock in addition to the CONVERT START command. In most cases, there is no need to synchronize the two. The frequency of the external clock, if required, generally falls in the range of 1–30 MHz depending on the conversion time and resolution of the ADC. Other SAR ADCs have an internal oscillator which is used to perform the conversions and only requires the CONVERT START command. Because of their architecture, SAR ADCs generally allow single-shot conversion at any repetition rate from DC to the converter’s maximum conversion rate.

Notice that the overall accuracy and linearity of the SAR ADC is determined primarily by the internal DAC. Until recently, most precision SAR ADCs used laser-trimmed thin-film DACs to achieve the desired accuracy and linearity. The thin-film resistor trimming process adds cost, and the thin-film resistor values may be affected when subjected to the mechanical stresses of packaging.

For these reasons, switched capacitor (or charge redistribution) DACs have become popular in newer SAR ADCs. The advantage of the switched capacitor DAC is that the accuracy and linearity are primarily determined by photolithography, which in turn controls the capacitor plate area and the capacitance as well as matching. In addition, small capacitors can be placed in parallel with the main capacitors which can be switched in and out under control of autocalibration routines to achieve high accuracy and linearity without the need for thin-film laser trimming. Temperature tracking between the switched capacitors can be better than 1 ppm/°C, thereby offering a high degree of temperature stability.

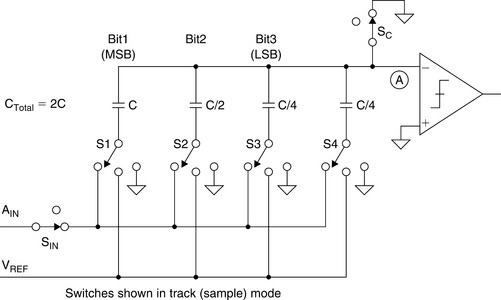

A simple 3-bit capacitor DAC is shown in Figure 6-47. The switches are shown in the track, or sample mode where the analog input voltage, AIN, is constantly charging and discharging the parallel combination of all the capacitors. The hold mode is initiated by opening SIN, leaving the sampled analog input voltage on the capacitor array. Switch SC is then opened allowing the voltage at node A to move as the bit switches are manipulated. If S1, S2, S3, and S4 are all connected to ground, a voltage equal to –AIN appears at node A. Connecting S1 to VREF adds a voltage equal to VREF/2 to –AIN. The comparator then makes the MSB bit decision, and the SAR either leaves S1 connected to VREF or connects it to ground depending on the comparator output (which is high or low depending on whether the voltage at node A is negative or positive, respectively). A similar process is followed for the remaining two bits. At the EOC interval, S1, S2, S3, S4, and SIN are connected to AIN, SC is connected to ground, and the converter is ready for another cycle.

Note that the extra LSB capacitor (C/4 in the case of the 3-bit DAC) is required to make the total value of the capacitor array equal to 2C so that binary division is accomplished when the individual bit capacitors are manipulated.

The operation of the capacitor DAC (cap DAC) is similar to an R–2R resistive DAC. When a particular bit capacitor is switched to VREF, the voltage divider created by the bit capacitor and the total array capacitance (2C) adds a voltage to node A equal to the weight of that bit. When the bit capacitor is switched to ground, the same voltage is subtracted from node A.

An example of charge redistribution successive approximation ADCs is Analog Devices’ PulSAR™ series. The AD7677 is a 16-bit, 1 MSPS, PulSAR, fully differential ADC that operates from a single 5 V power supply (see Figure 6-48). The part contains a high speed 16-bit sampling ADC, an internal conversion clock, error correction circuits, and both serial and parallel system interface ports. The AD7677 is hardware factory calibrated and comprehensively tested to ensure such AC parameters as SNR and total harmonic distortion (THD), in addition to the more traditional DC parameters of gain, offset, and linearity. It features a very high sampling rate mode (Warp) and, for asynchronous conversion rate applications, a fast mode (Normal) and, for low power applications, a reduced power mode (Impulse) where the power is scaled with the throughput.

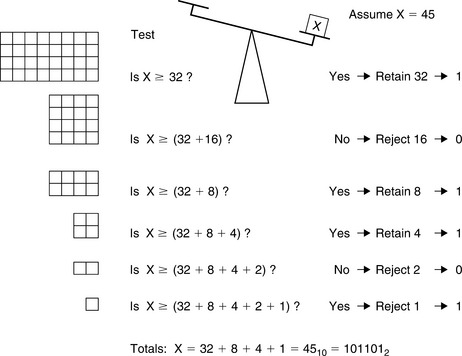

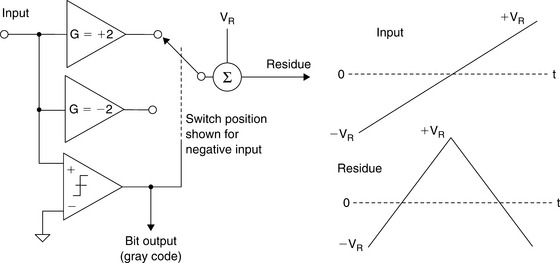

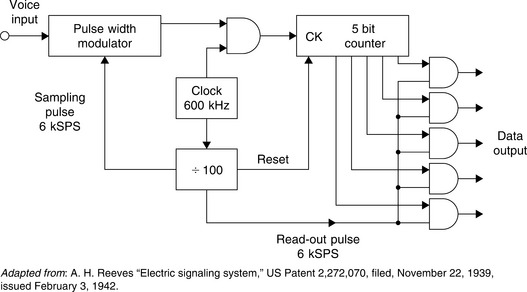

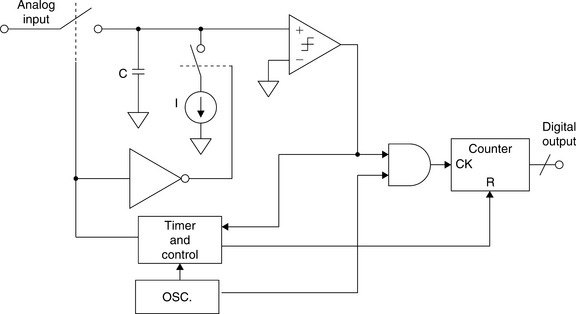

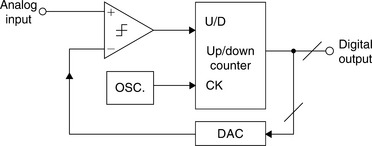

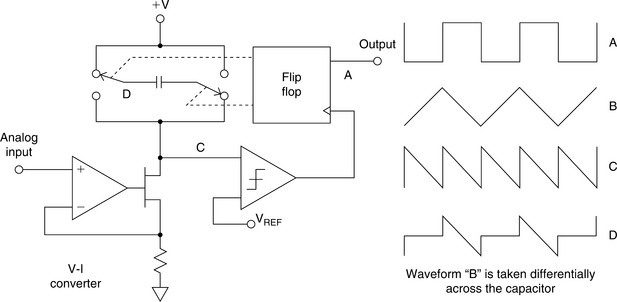

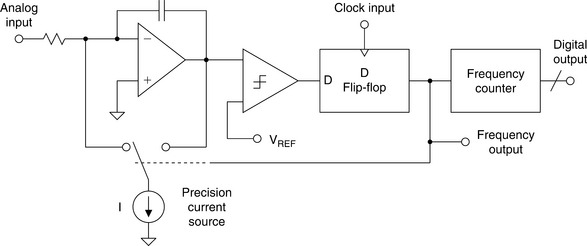

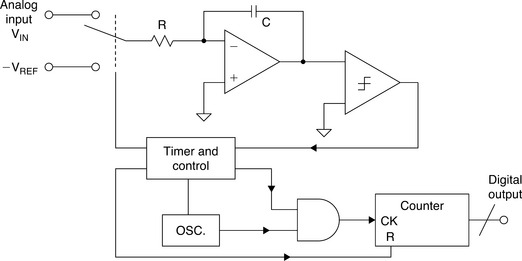

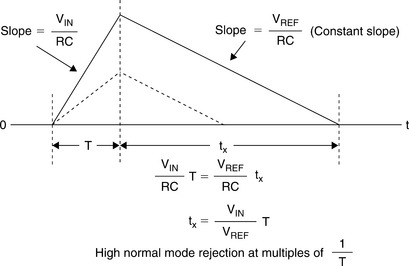

The operation of a successive approximation ADC is as follows. Using Figure 6-49 as an example, one side of the balance is loaded with half-scale (in this case 32 lbs.). Call this the proof mass. The test mass is then put on the other side of the balance. If the test mass is greater, as it is in this case, the proof mass is retained, otherwise it is discarded. Next a proof mass equal to 1/4 scale is added. Again, if the test mass is still greater the proof mass is retained, otherwise it is rejected. In the example it is rejected. This process is continued, each time cutting the proof mass in half, until the desired resolution is reached. The proof masses are added up. This will equal the mass of the test mass, to the resolution of the test.