Appendix. Symbols

Ladder Programs

| Semi-graphic form | Full graphic form | |

|---|---|---|

| A horizontal link along which power can flow | ||

| Interconnection of horizontal and vertical power flows |  |  |

| Left-hand power connection of a ladder rung |  |  |

| Right-hand power connection of a ladder rung |  |  |

| Normally open contact | ||

| Normally closed contact | ||

| Positive transition-sensing contact, power flow occurs when associated variable changes from 0 to 1. | ||

| Negative tranistion-sensing contact, power flow occurs when assoaciated variable changes from 1 to 0 | ||

| Output coil: if the power flow to it is on then the coil state is on | ||

| Set coil | ||

| Reset coil | ||

| Retentive memory coil, the state of the associated variable is retained on PLC power fail |

Function Blocks

| Semi-graphic form | Full graphic form | |

|---|---|---|

| Horizontal and vertical lines |  | |

| Interconnection of horizontal and vertical signal flows |  |  |

| Crossing horizontal and vertical signal flow |  |  |

| Blocks with connections |  |  |

| Connectors |

Commonly Encountered Blocks

| BOOL is Boolean signal, INT is integer, REAL is a floating point number, ANY is any form of signal | |

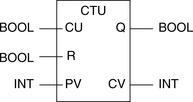

| Up-counter counts the number of rising edges at input CU. PV defines the maximum value of the counter. Each new rising edge at CU increments CV by 1. Output Q occurs after set count. R is the reset. |  |

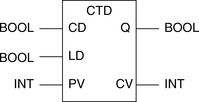

| Down-counter counts down the number of rising edges at input CU. PV defines the starting value of the counter. Each new rising edge at CU decrements CV by 1. Output Q occurs when count reaches. zero. |  |

| Up-down counter. It can be used to count up on one input and down on the other. |  |

| On-delay timer. When input IN goes true, the elapsed time at about ET starts to increase and when it reaches the set time, specified by input PT, the output Q goes true. |  |

| Off-delay timer. When input IN goes true, the output Q follows and remains true for the set time after the input Q goes false. |  |

| Pulse timer. When input IN goes true, output Q follows and remains true for the pulse duration specified by input PT. |  |

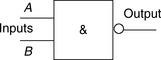

Logic Gates

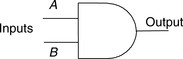

| AND gate |  |  |

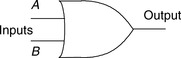

| OR gate |  |  |

| NOT gate |  |  |

| NAND gate |  |  |

| NOR Gate |  |  |

| XOR Gate |  |  |

Sequential Function Charts

| Start step. This defines the step which will be activated when the PLC is Cold-started. | |

| Transition condition. Every transition must have a condition. One that always occurs should be shown with the condition TRUE. | |

| Step in a program | |

| Every step can have an associated action. An action describes the bahviour that occurs when the step is activated. Each action can have a qualifier: N indicates the action is executed while the step is active. If no qualifier is indicated it is taken to be N. |  |

| Selective branching |  |

| Parallel branching when the transition occurs |  |

| Convergence when both transitions occur |  |

| Simultaneous convergence |  |

Instruction List (IEC 1131-3 Symbols)

LDStart a rung with an open contact

LDNStart a rung with a closed contact

STAn output

SSet true

RReset false

ANDBoolean AND

ANDNBoolean NAND

ORBoolean OR

ORNBoolean NOR

XORBoolean XOR

NOTBoolean NOT

ADDAddition

SUBSubtraction

MULMultiplication

DIVDivision

Structured Text

X:= YY represents an expression that produces a new value for the variable X.

Operators

(…)Parenthesized (bracketed) expression

Function(…)List of parameters of a function

**Raising to a power

−,NOT Negation, Boolean NOT

*, /, MODMultiplication, division, modulus operation

+, −Addition, subtraction

<, >, <=, >=Less than, greater than, less than or equal to, greater than or equal to

=, <>Equality, inequality

AND, &Boolean AND

XORBoolean XOR

ORBoolean OR

Conditional and Iteration Statements

IF … THEN … ELSE is used when selected statements are to be executed when certain conditions occur.

The FOR … DO iteration statement allows a set of statements to be repeated, depending on the value of the iteration integer variable.

The WHILE … DO iteration statement allows one or more statements to be executed while a particular Boolean expression remains true.

The REPEAT … UNTIL iteration statement allows one or more statements to be executed and repeated while a particular Boolean expression remains true.

..................Content has been hidden....................

You can't read the all page of ebook, please click here login for view all page.