Appendix E

Assembly Instructions

This appendix lists the different assembly instructions used on ARM cores, and what architecture each instruction introduced.

ARM INSTRUCTIONS

The following is a list of ARM-state instructions, separated into various categories.

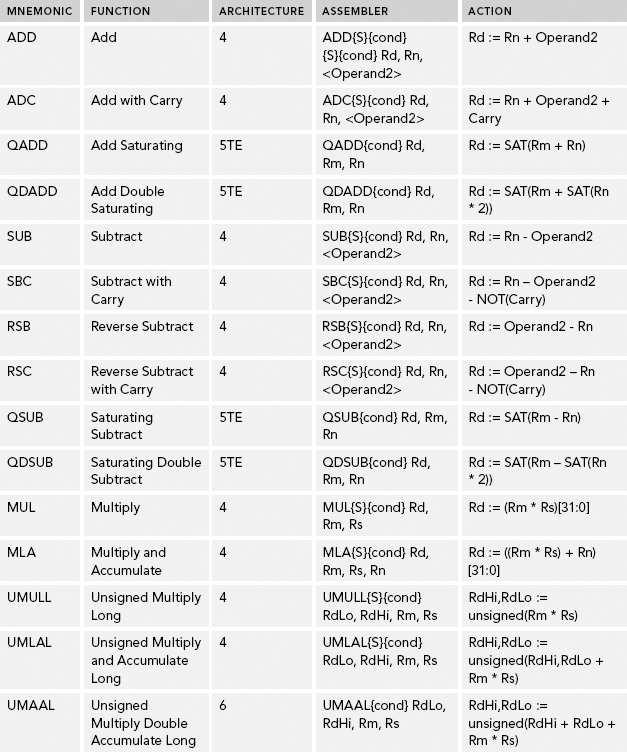

Arithmetic Instructions

Arithmetic instructions do basic mathematical calculations: addition, subtraction, multiplication, and division. These instructions are listed in Table E-1, as well as the architecture in which they were introduced.

TABLE E-1: List of Arithmetic Instructions

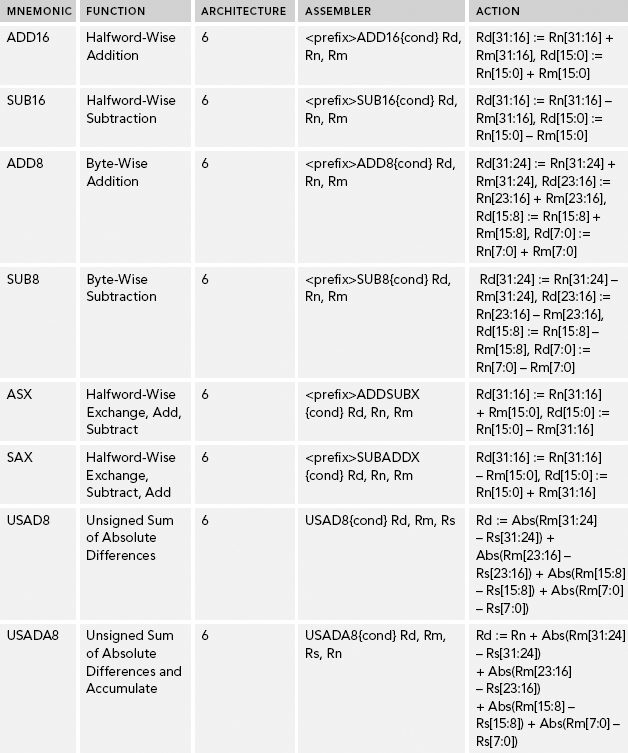

Parallel Arithmetic

Parallel arithmetic instructions are instructions that work on two or more values packed into 32-bit data. Parallel arithmetic instructions use prefixes, listed in Table E-2.

TABLE E-2: Parallel Arithmetic Prefixes

| PREFIX | FUNCTION |

| S | Signed arithmetic modulo 28 or 216. Sets APSR GE flags |

| Q | Signed saturating arithmetic |

| SH | Signed arithmetic, halving the results |

| U | Unsigned arithmetic modulo 28 or 216. Sets APSR GE flags |

| UQ | Unsigned saturating arithmetic |

| UH | Unsigned arithmetic, halving the results |

Table E-3 lists parallel arithmetic instructions, their usage, and their effect.

TABLE E-3: Parallel Arithmetic Instructions

Movement

Movement instructions take data from one register before moving it to a second register, optionally negating the data first. Movement instructions can also place data into registers from operands. These instructions are listed in Table E-4.

TABLE E-4: Movement Instructions

The MSR instruction uses a field parameter that specifies the SPSR or CPSR fields to be moved. They are listed in Table E-5.

TABLE E-5: MSR Fields Parameters

| FIELD | DESCRIPTION |

| C | Control field mask byte, PSR[7:0] |

| X | Extension field mask byte, PSR[15:8] |

| S | Status field mask byte, PSR[23:16] |

| F | Flags field mask byte, PSR[31:24] |

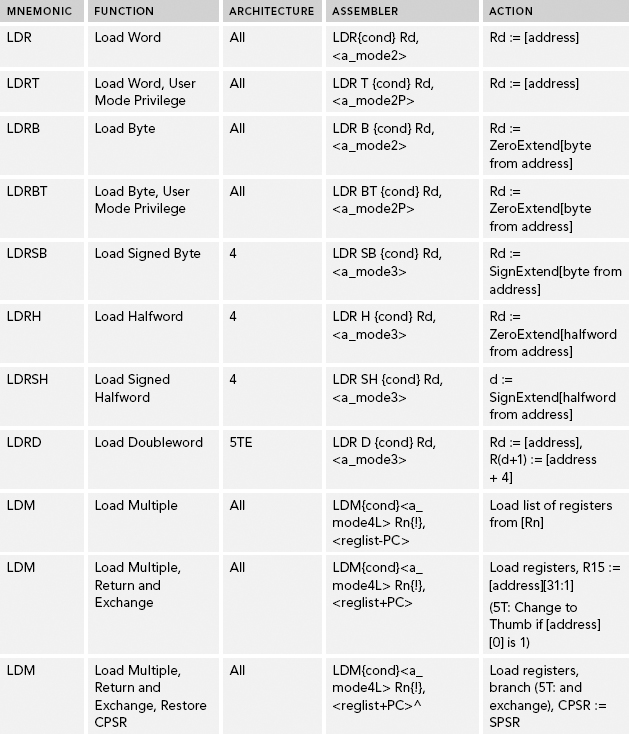

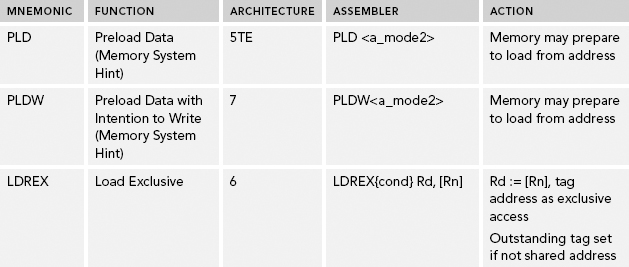

Load

Load instructions take memory addresses and put the contents of those locations into registers. They are listed in Table E-6.

TABLE E-6: Load Instructions.

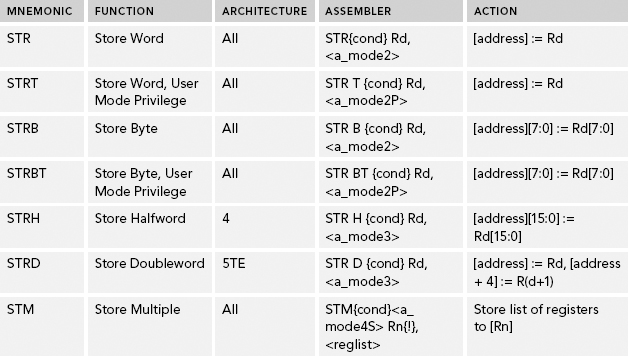

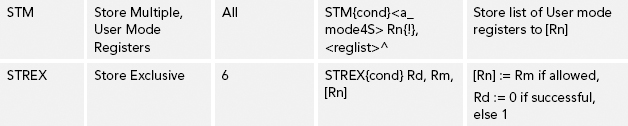

Store

Store instructions place memory from registers into system memory. The data size can vary, and multiple registers can be stored to memory in a single instruction. Store instructions are listed in Table E-7.

TABLE E-7: Store Instructions

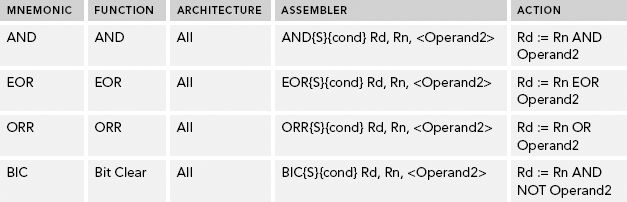

Logical

Logical instructions perform logical bit-wise operations on registers. They are listed in Table E-8.

TABLE E-8: Logical Instructions

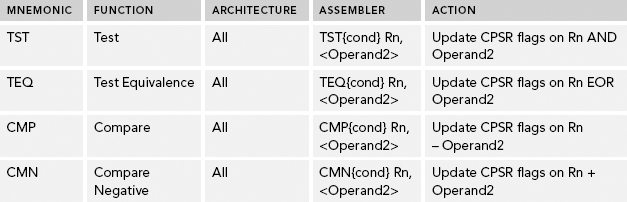

Comparison

Comparison instructions compare a register to another register, or to static data, and test bitwise data. The instructions are listed in Table E-9.

TABLE E-9: Comparison Instructions

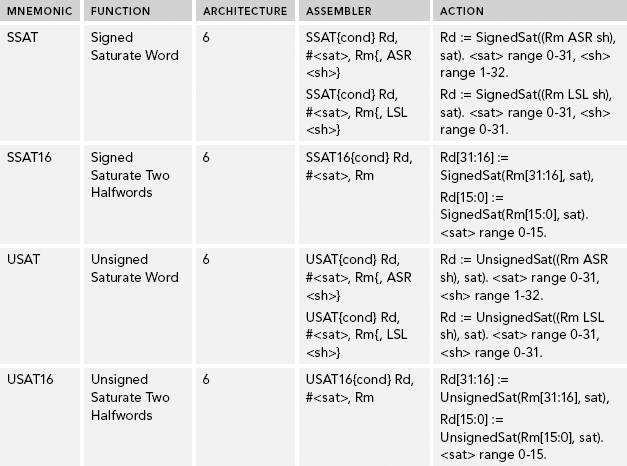

Saturate

Saturating instructions are arithmetic instructions that saturate; they will not overflow their containers, and will return the maximum or minimum value possible when an overflow would occur. They are listed in Table E-10.

TABLE E-10: Saturating Arithmetic Instructions

Branch

Branch instructions order the processor or microcontroller to execute code elsewhere, conditionally or unconditionally. Branching instructions can link, and can change processor modes if required. They are listed in Table E-11.

TABLE E-11: Branch Instructions

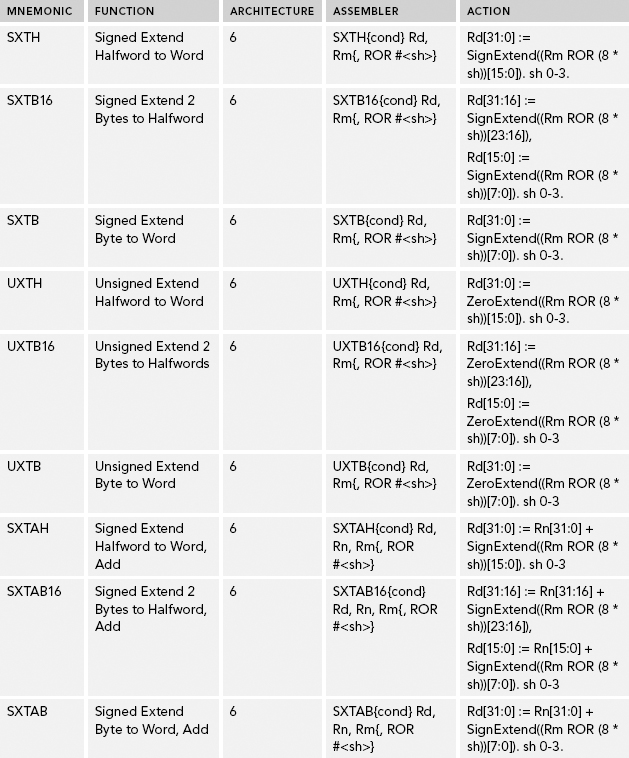

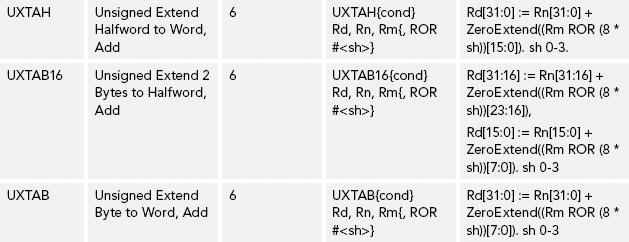

Extend

Extend instructions change a value’s size, for example, extending a 16-bit signed or unsigned value to 32-bits. They are listed in Table E-12.

TABLE E-12: Extend Instructions

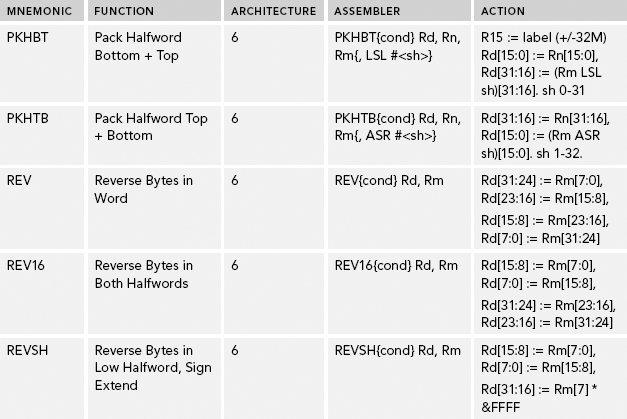

Miscellaneous

These are instructions that do not belong to any previous category. They are listed in Table E-13.

TABLE E-13: Miscellaneous Instructions

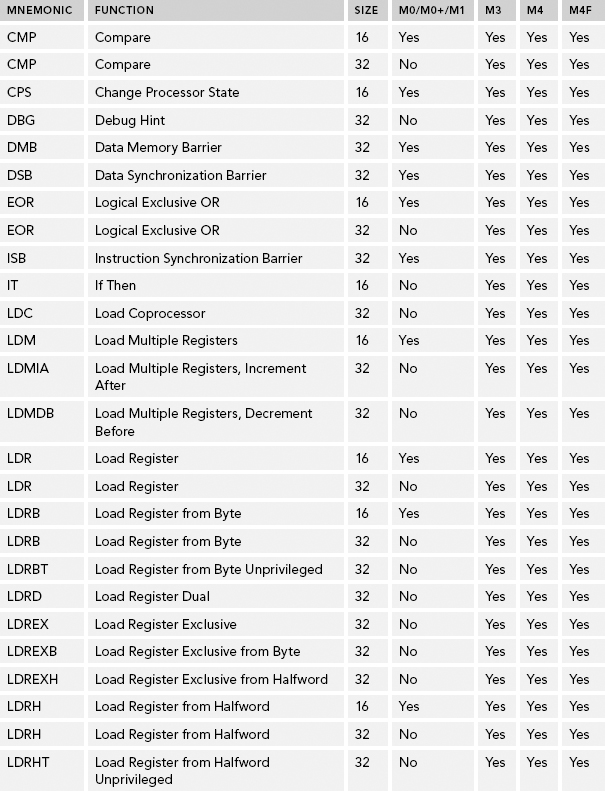

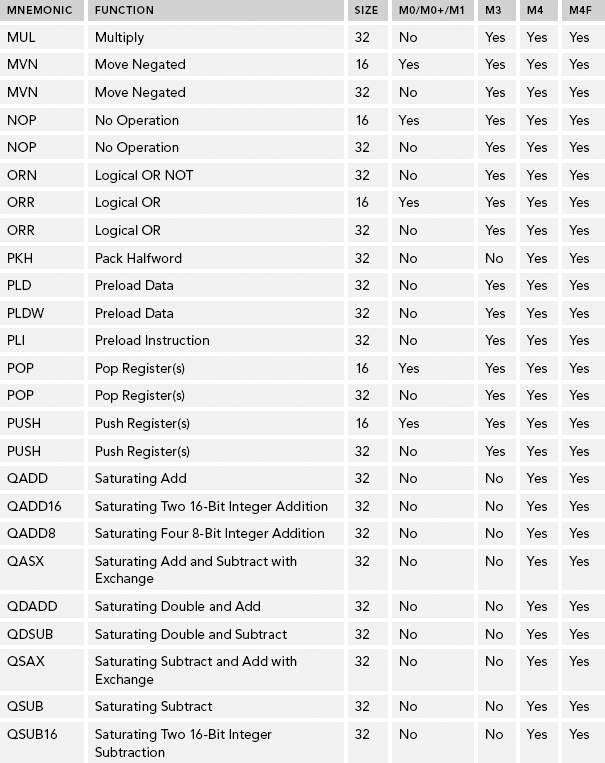

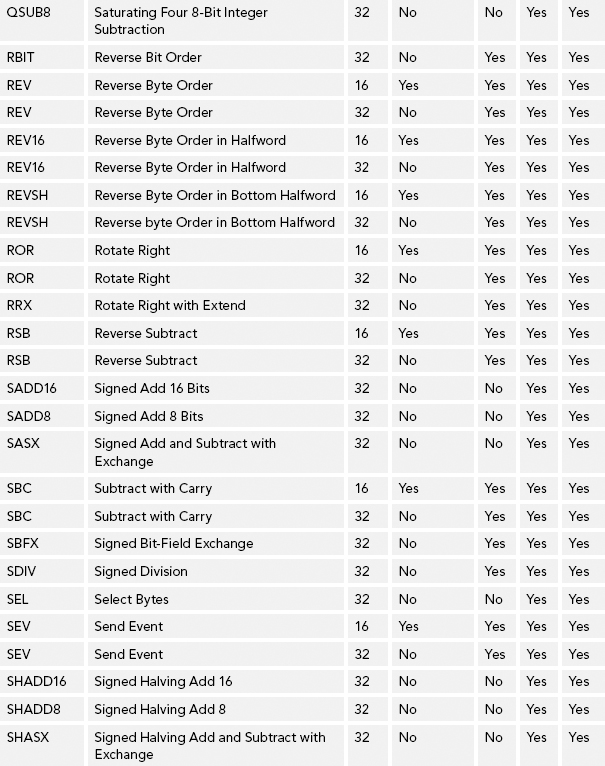

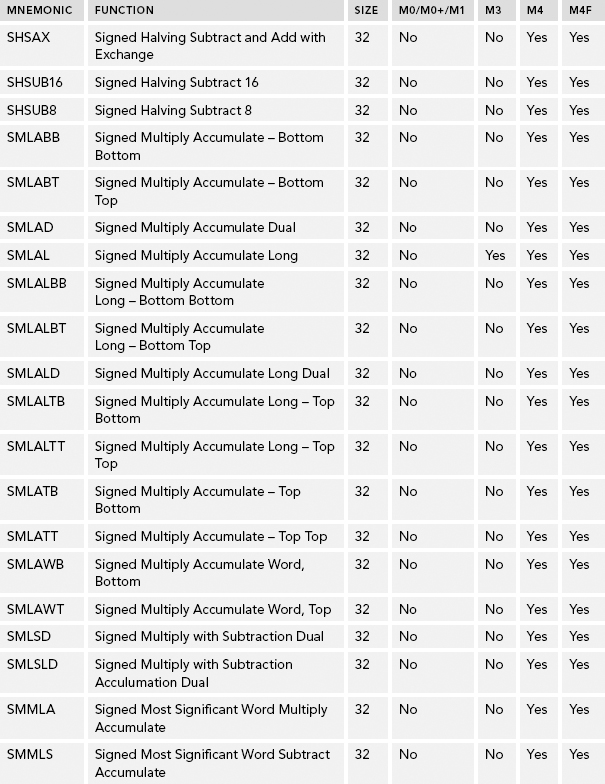

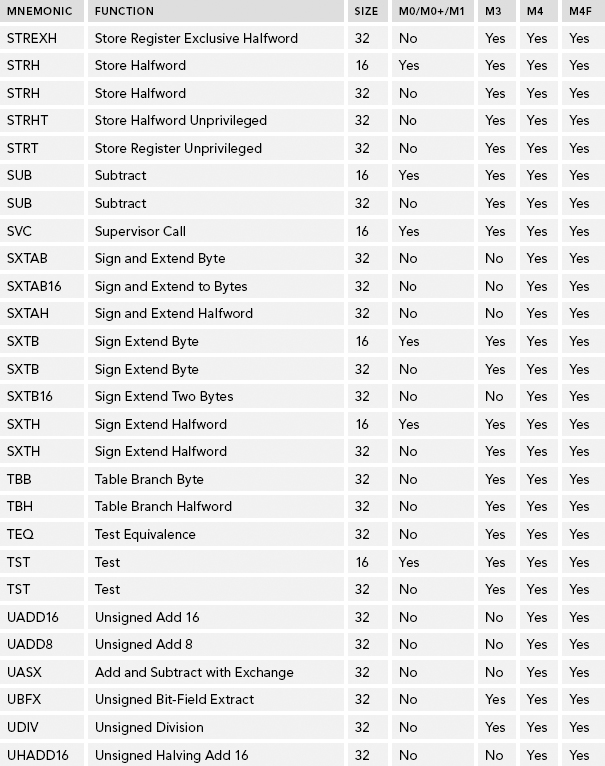

THUMB INSTRUCTIONS ON CORTEX-M CORES

Cortex-M cores support only a subset of Thumb instructions, or the entire Thumb instruction set, depending on the core. Table E-14 lists the different Cortex-M cores, and the supported instructions.

TABLE E-14: Thumb Instructions on Cortex-M Cores